聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602037 -

DDR3

+關注

關注

2文章

274瀏覽量

42186 -

存儲器

+關注

關注

38文章

7455瀏覽量

163623 -

Altera

+關注

關注

37文章

777瀏覽量

153861

發布評論請先 登錄

相關推薦

JEDEC發布DDR3存儲器標準的DDR3L規范

JEDEC 固態技術協會,微電子產業標準全球領導制定機構,今天宣布正式發布JEDEC DDR3L規范。這是廣受期待的DDR3存儲器標準JESD79-3 的附件。這是

發表于 08-05 09:10

?3740次閱讀

基于FPGA的DDR3多端口讀寫存儲管理系統設計

本文以Kintex-7系列XC7K410T FPGA芯片和兩片MT41J128M16 DDR3 SDRAM芯片為硬件平臺,設計并實現了基于FPGA的視頻圖形顯示系統的DDR3多端口

發表于 04-07 15:52

?1.3w次閱讀

基于FPGA的DDR3多端口讀寫存儲管理設計

。

DDR3存儲器控制模塊采用Xilinx公司的MIG[4](Memory Interface Generator)方案,通過用戶接口建立FPGA內部控制邏輯到DDR3

發表于 06-26 18:13

基于FPGA的DDR3多端口讀寫存儲管理的設計與實現

作者:吳連慧,周建江,夏偉杰摘要:為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3

發表于 08-02 11:23

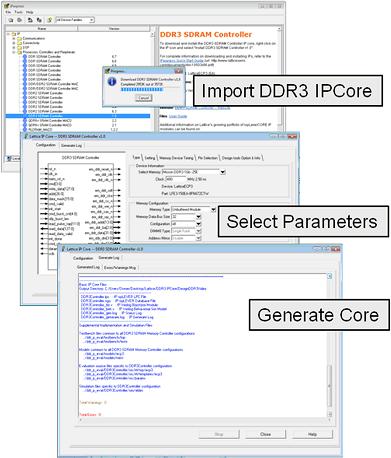

DDR3存儲器接口控制器IP助力數據處理應用

了設計的一大挑戰。FPGA可通過在單個FPGA中實現多個視頻處理器來提供強大的處理能力。那么現在的挑戰就變成了要使數據盡快且高效地從FPGA

發表于 05-24 05:00

基于DDR3存儲器的數據處理應用

了設計的一大挑戰。FPGA可通過在單個FPGA中實現多個視頻處理器來提供強大的處理能力。那么現在的挑戰就變成了要使數據盡快且高效地從FPGA

發表于 05-27 05:00

如何用中檔FPGA實現高速DDR3存儲器控制器?

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的

發表于 08-09 07:42

用中檔FPGA實現高速DDR3存儲器控制器

用中檔FPGA實現高速DDR3存儲器控制器

引言

由于系統帶寬不斷的增加,因此針對更高的速度和性能,設計人員對存儲技術

發表于 01-27 11:25

?984次閱讀

DDR3存儲器接口控制器IP核在視頻數據處理中的應用

DDR3存儲器系統可以大大提升各種數據處理應用的性能。然而,和過去幾代(DDR和DDR2)器件相比,D

發表于 07-16 10:46

?1838次閱讀

基于FPGA的DDR3多端口讀寫存儲管理的設計與實現

為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲

發表于 11-18 18:51

?7089次閱讀

Stratix III FPGA的特點及如何實現和高速DDR3存儲器的接口

DR3 在高頻時數據出現了交錯,因此,高速DDR3存儲器設計有一定的難度。如果FPGA I/O 結構中沒有直接內置調平功能,那么連接

FPGA學習-DDR3

一、DDR3簡介 ? ? ? ? DDR3全稱double-data-rate 3 synchronous dynamic RAM,即第三代雙倍速率同步動態隨機存儲器。所謂同步,是指

完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數據表

電子發燒友網站提供《完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器

發表于 04-09 09:49

?0次下載

FPGA如何與DDR3存儲器進行正確的數據對接?

FPGA如何與DDR3存儲器進行正確的數據對接?

評論