聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

Altera

+關(guān)注

關(guān)注

37文章

777瀏覽量

153852 -

內(nèi)存模型

+關(guān)注

關(guān)注

0文章

7瀏覽量

6133

發(fā)布評論請先 登錄

相關(guān)推薦

利用RLDRAM II存儲器提高網(wǎng)絡(luò)設(shè)備性能

隨著語音、數(shù)據(jù)、視頻流的逐漸融合,下一代網(wǎng)絡(luò)(NGN)設(shè)計和新的寬帶平臺必須能在嚴(yán)格的帶寬和時延條件下提供更強的系統(tǒng)性能。而RLDRAM II存儲器采用專門針對高速運算進行優(yōu)化的8個內(nèi)存組(Bank

發(fā)表于 10-08 15:45

通過VeriStand加載MATLAB模型到實時仿真機,VeriStand出現(xiàn)卡頓現(xiàn)象

軟件版本:NI VeriStand 2016運行環(huán)境:Windows7 旗艦版 SP1宿主機配置:i7處理器,8G內(nèi)存,固態(tài)盤仿真機配置:i5處理器,4G內(nèi)存,固態(tài)盤實時

發(fā)表于 06-09 10:28

給Altera Arria 10 FPGA和Arria 10 SoC供電:經(jīng)過測試和驗證的電源管理解決方案

)、更改功率額定值、計算效率和功率損耗、進行每個電源模塊的仿真、選擇 DC/DC 穩(wěn)壓器的型號、并認(rèn)證一款定制的解決方案。LTpowerPlanner 可針對 Arria 10 開發(fā)套件的 FPGA

發(fā)表于 10-29 17:01

SIMULINK仿真的運行

SIMULINK仿真的運行構(gòu)建好一個系統(tǒng)的模型之后,接下來的事情就是運行模型,得出仿真結(jié)果。

發(fā)表于 06-19 12:53

?4113次閱讀

基于Arria 10 SoC FPGA的高性能低成本解決方案

本文介紹了Arria 10 SoC FPGA主要特性,框圖以及Arria 10 SoC開發(fā)板主要特性,電源分布網(wǎng)絡(luò)圖和電路圖。

在Arria 10 PCI Express中更改串行和PIPE仿真的方法

如何在Arria 10 PCI Express (PCIe)中更改串行(Serial)和PIPE仿真

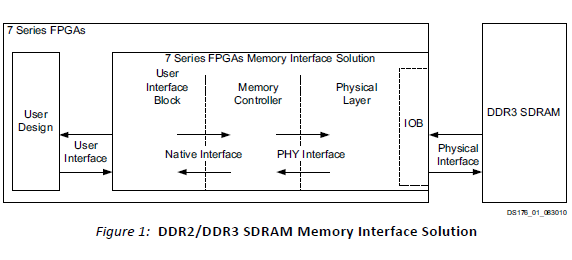

Zynq-7000 SoC和7系列FPGA設(shè)備內(nèi)存接口解決方案資料說明

Xilinx Zynq-7000 SOC和7系列FPGA內(nèi)存接口解決方案核心提供了到DDR3和DDR2 SDRAM、QDR II+SRAM、RLDRAM II/RLDRAM

發(fā)表于 02-25 17:24

?18次下載

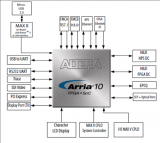

英特爾Arria 10 FPGA的應(yīng)用之路

中,小編為大家分別總結(jié)了英特爾 Cyclone FPGA和英特爾 Stratix 10 FPGA的應(yīng)用之路,今天就輪到咱們的英特爾 Arria 10 FPGA了~ ? ? 英特爾 Arria

jvm內(nèi)存模型和內(nèi)存結(jié)構(gòu)

JVM(Java虛擬機)是Java程序的運行平臺,它負(fù)責(zé)將Java程序轉(zhuǎn)換成機器碼并在計算機上執(zhí)行。在JVM中,內(nèi)存模型和內(nèi)存結(jié)構(gòu)是兩個重要的概念,本文將詳細(xì)介紹它們。 一、JVM

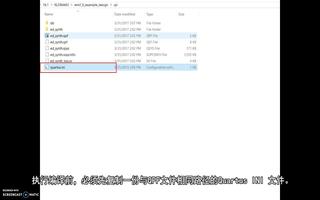

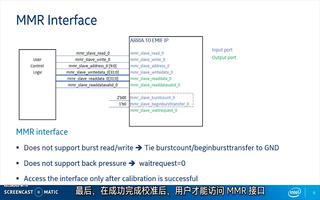

廠商內(nèi)存模型運行 Arria 10 RLDRAM3 的仿真操作

廠商內(nèi)存模型運行 Arria 10 RLDRAM3 的仿真操作

評論