計算機體系結構頂會ISCA-18上周結束,圖靈獎得主John Hennessy和David Patterson發表特邀報告,展望體系結構新的黃金時代。本屆會議近1/3的論文關于神經網絡加速器,專用領域架構和軟硬件協同設計是最受關注的議題。谷歌、Facebook等非傳統硬件公司的存在感也愈發強烈。加州大學圣芭芭拉分校(UCSB)謝源課題組神經網絡架構研究團隊博士后胡杏、鄧磊、謝新峰、谷芃和劉瀏對大會技術趨勢做了總結。

ISCA是計算機體系結構領域的頂級會議,本屆ISCA的亮點無疑是新當選的圖靈獎得主、體系結構領域的兩位宗師級人物John L. Hennessy和David A. Patterson做的特邀報告。

本文將先從兩位圖靈獎得主的報告講起,總結會議關鍵技術趨勢,展現與會專家的觀點與評論,最后對論文接收和子領域熱度等會議情況進行介紹。

從這屆會議中可以發現四大關鍵技術趨勢,

專用架構與軟硬件協同設計將是未來專有化架構研究趨勢,也將是走出摩爾定律困境一個富有前景的方向;

神經網絡加速器開始從設計走向落地;

由于Meltdown和Spectre,硬件安全性得到更多關注。安全領域的研究方法除軟件、系統,也需要從體系結構的層面來進一步加強;

RISC-V為敏捷開發提供了可能,未來可能成為開源硬件的基礎。

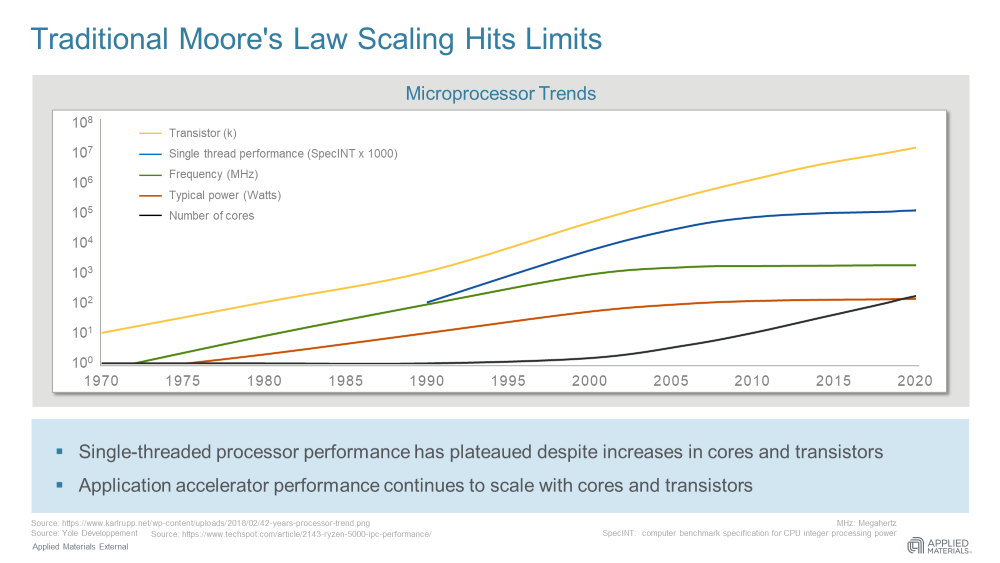

如何走出摩爾定律困境?Keynote演講人、Facebook Research的Kim Hazelwood博士半開玩笑說,這屆ISCA每個keynote前面都要放這張slide,表明了領域的困境與研究方向

Turing Lecture:體系結構迎來新的黃金時代

在本次大會的圖靈講座(Turing Lecture)上,2017年榮獲圖靈獎的John L. Hennessy和David A. Patterson首先簡要回顧了計算機體系結構的發展史,總結了目前體系結構研究的兩大挑戰:通用處理器性能提升的停滯和體系結構安全的問題。

兩位演講者提及到上世紀80年代是體系結構發展的黃金時期,諸如RISC、超標量處理器(superscalar)、多層緩存(multilevelcaches)、預測技術(speculation)、編譯器優化(compileroptimization)等等體系結構創新,使得計算機性能每年提升約60%。在上世紀90年代到21世紀初,由于體系結構創新的放緩,計算機性能的提升主要依賴于工藝技術的進步、更高的時鐘頻率和更大的緩存。

目前,隨著摩爾定律(Moore’s Law)和登納德縮放比例定律(Dennard Scaling)的放緩甚至停滯,單處理器核心的性能每年的提升已降為3%左右。與此同時,近來的計算機漏洞幽靈(Spectre)和融毀(Meltdown),均利用了體系結構設計的缺陷,而體系結構的安全性問題在近幾十年來沒有得到體系結構研究者和設計者的足夠關注。

David Patterson(左)與John Hennessy(右)和與圖靈像合影;旁邊展示了本屆ISCA贊助商,谷歌、微軟、亞馬遜、Facebook等非傳統硬件廠商的存在感在增強

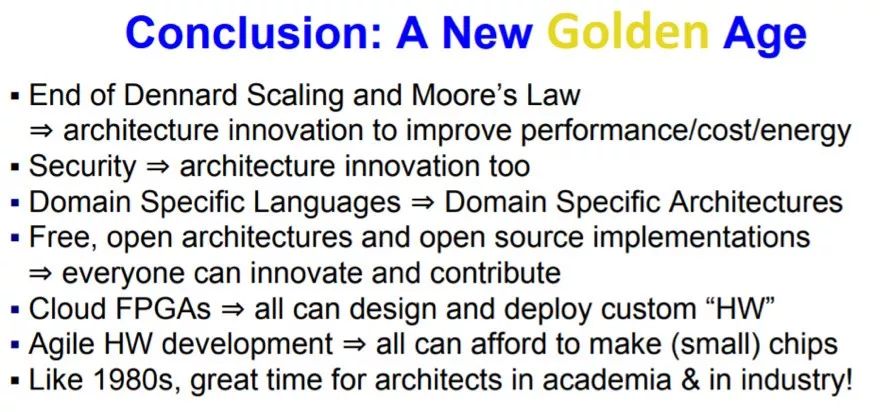

對于這些挑戰,兩位演講者總結了體系結構新的機遇:(1)軟硬件協同設計(Hardware/Software Co-Design)和高層專用語言(High-Level and Domain-Specific Languages);(2)計算機體系結構安全性的提升;(3)開源體系結構設計(Free and Open Architectures and Open-Source Implementations);(4)創新的敏捷芯片開發(Agile Chip Development)。

這其中(1)強調了專用體系結構(Application Specific IC/Architecture)和專用編程語言(Domain Specific)的開發,對于提升特定領域性能、功耗和開發效率的重要性,尤其是神經網絡(neural network)、圖計算(graph computation)等新興且需要高性能計算的領域。(2)強調了安全應該和性能同樣地受到體系結構設計研究的重視,尤其是防止信息泄露和邊信道攻擊(Side-channel attack)。(3)強調了體系結構設計開源,尤其是指令集架構(Instruction Set Architecture)開源的重要性。兩位演講者介紹了他們近幾年在RISC-V方面所作的工作。最后,(4)強調了怎樣縮短芯片開發的時間和成本這兩個核心要素。他們認為敏捷開發(Agile development process)可以使得較小的研究開發組可以反復迭代地在短時間內廉價地開發產品原型。最終的目標是體系結構的研究者可以利用這種開發方式,得以流片(tape-out)驗證有價值的設計方案。

非硬件公司存在感增強,機器學習影響架構和編程語言

在keynote方面,本次大會邀請了Kim Hazelwood(Facebook Research),Kunle Olukotun(斯坦福大學)以及Doug Burger(Microsoft Research),分別針對Facebook的機器學習、軟件2.0(機器學習怎樣影響架構和編程語言)和數據流架構(Explicit Dataflow Execution)進行了介紹。

值得一提,本次大會同時頒發了 Eckert-Mauchly Award,這是計算機體系結構領域最崇高的獎項,此前JohnHennessy和David Patterson也先后獲得過這一榮譽。

今年Eckert-Mauchly Award的獲獎者是華盛頓大學(University of Washington's Paul G. Allen School of Computer Science & Engineering)的Susan Eggers教授,基于她對同步多線程體系結構和多核共享和一致性問題的貢獻。她也是首位獲此殊榮的女性。Susan Eggers本身經歷比較傳奇,她在本科拿到經濟學學士后,在其他領域工作了十年才轉到計算機領域,47歲時博士畢業到華盛頓大學開始教職生涯。

此外,Gabriel Loh本次因在三維堆疊架構領域的杰出貢獻,獲得Maurice Wilkes獎,Wilkes獎每年一次,主要表彰推動體系結構工業發展的個人。Gabriel Loh于 2010年加入AMD,2013年成為AMD Fellow。

謝源課題組與Gabriel Loh(后排右數第六位)合影,后排右一是謝源教授

技術趨勢預測:專用領域架構全棧設計和軟硬件協同,神經網絡加速器從設計到落地

1、專用領域語言 (Domain Specific Language) 與專用領域架構(Domain Specific Architecture)計算模型與架構硬件能力的抽象至關重要。

針對專用領域或者應用的架構設計仍是今年ISCA的一大焦點,隨之而來的是專用領域語言與硬件的設計又被帶入了大眾的視野。隨著專用領域架構的發展,對這些架構進行支持的編程語言也受到了廣泛的關注。這種考慮專用應用領域的架構與語言的軟硬件協同設計方法將會是未來專有化架構研究的一個趨勢,以及這將成為走出摩爾定律帶來的困境的一個富有前景的方案。

在圖靈獎演講中,2017年圖靈獎獲得者John Hennessy教授指出了,隨著摩爾定律的終結,我們需要新的計算機架構研究方法。他預言,計算機架構團隊縱向整合的時代即將復興,體系結構設計者將如過去一樣,不僅需要了解底層器件,工藝,以及電路的知識,也需要有著對編程語言以及編譯器的了解。John在總結中慷慨激昂地提到:“一切舊的東西又是新的!(Everything old is new again!)”

John Hennessy在演講中指出,隨著摩爾定律的終結,我們需要新的計算機架構研究方法。圖片來自ACM Twitter

在ISCA第二天的keynote中,來自斯坦福大學的Kunle Olukotun教授介紹了他們對于軟件2.0時代的計算機系統研究。他們指出了神經網路應用對計算機硬件設計帶來了極其難得的機遇,最重要的是,該應用對于硬件的一些正確性指標有著相對強大的容錯能力,比如內存一致性與計算精確度。同時,在他的演講中,Kunle也強調了全棧優化的重要性。在他們的研究中,他們提出了若干并行計算的模式,并針對這些專用模式進行專用領域硬件的設計,極大提升了在專用領域硬件的性能,以及通過開發專用領域語言減輕了軟件開發者在新興架構上開發高性能程序的壓力。

專用領域帶來了新的機會,這些新的機會幫助我們設計新硬件,也讓軟件開發變得更加高效。從這些研究中,我們也看到了軟硬針對專用協同設計的未來!

2、神經網絡加速器從設計到落地:加速器落地真實物理系統及全系統優化

縱觀近兩年神經網絡加速所采用的模型壓縮算法,主要包括對于神經元狀態和權重連接參數的稀疏化和低比特量化,以及加速器硬件優化策略,主要包括處理單元數據復用、存儲計算一體化、存儲器優化等,對加速器性的提升幾乎已經做到了極致的優化。從最初的純硬件優化到如今的算法和硬件協同優化,使得神經網絡加速器的優化空間逐漸收縮,基于現有方法和技術很難再實現大幅度的性能改善。在這樣的情況下,未來會逐漸發生從如何設計加速器到如何使用加速器的轉變,從設計加速器本身到設計全系統,并最終落地現實應用場景。

一方面,需要盡快構建神經網絡加速器的編程抽象模型、編程語言和編譯器,從而促進加速器的模塊化、標準化和易用性;另一方面,需要根據不同應用場景,選擇對應特性的加速器進行真實物理系統設計、優化和實現,從而促進加速器落地于現實生活。正如兩位圖靈獎獲得者JohnL. Hennessy and David A. Patterson在演講中提到的兩大熱點:專用域架構(Domain-specific Architecture)和專用域語言(Domain-specific Language),接下來學術界和產業界會更加關注上層語言的設計和開發。

同時,在移動平臺分會場,來自康奈爾大學的Mark Buckler和來自羅徹斯特大學的Yuhao Zhu在演講中均展示了如何把神經網絡加速器作為一個IP模塊進行移動視覺系統設計和優化。由此可見,神經網絡加速器的標準化或開源化,對于加速器的推廣和應用至關重要。

3、安全性受到關注。安全領域的研究方法除軟件,系統,也需要從體系結構的層面來進一步加強

針對最近的體系結構安全性問題(Meltdown& Spectre Design Flaws),本次大會的專家討論(panel discussion)邀請了5位專家和教授:Mark Hill作為主持人,Paul Kocher, Ruby B. Lee, Simha Sethumadhavan和Timothy Sherwood作為嘉賓對安全問題展開了討論。Paul指出了現有系統設計主題思想是面向性能,而缺乏安全性分析和設計。雖然性能的量化指標豐富且成熟,但安全性指標的量化體系并沒有建立,比如緩存行為,預測器,debug模式,以及功耗,內部傳感器等等對安全性的影響。由于量化分析方法的缺乏,加上微體系結構設計本身對軟件開發者不開放,導致系統構建時存在一些錯誤的安全性假設,也無法做性能和安全性的聯合優化和管理。Ruby Lee,Samira和Tim都認為體系結構社區需要對安全性投入更多關注,設計安全性能感知的計算機體系結構十分重要。

4、RISC-V為敏捷開發提供了可能,未來可能成為開源硬件的基礎

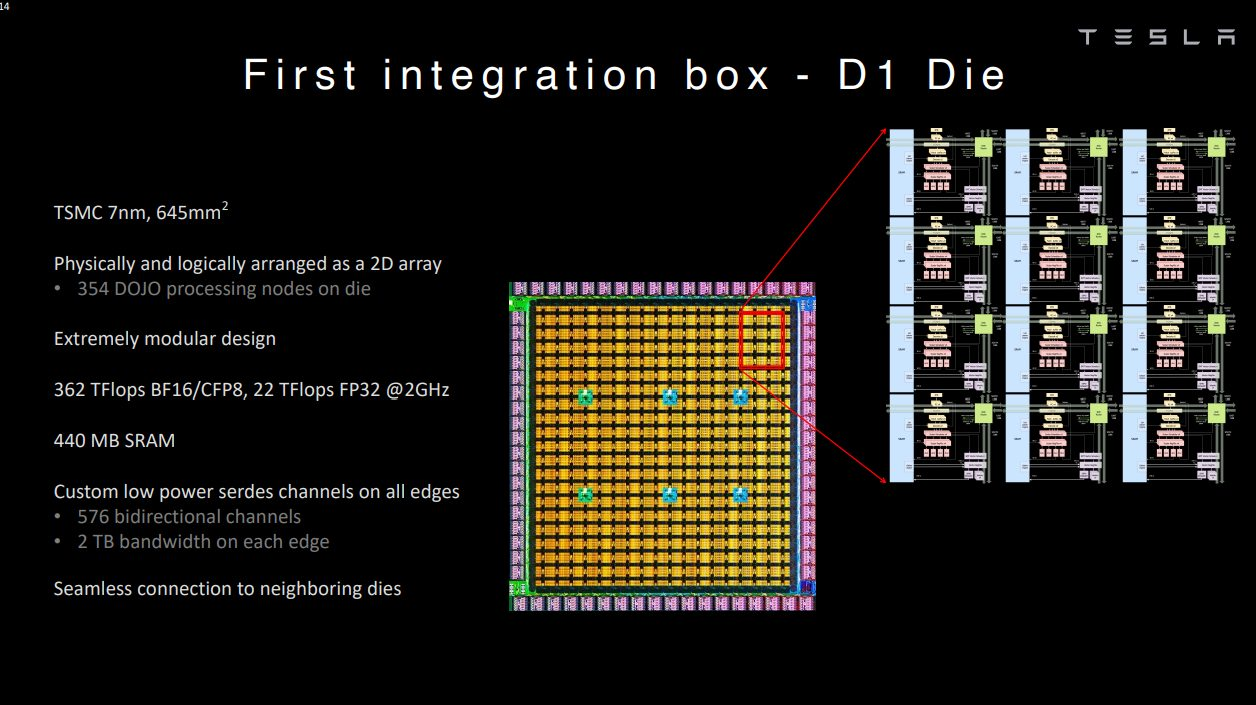

從兩位圖靈獎得主的演講當中,我們可以看到RISC-V作為開源精簡指令集對專用領域架構的重要性。隨著數據中心定制化硬件的普及,例如谷歌TPU和微軟Brainwave,硬件架構師不能僅模擬單節點而把問題留給流片后的測試,也需要模擬定制化部分。然后缺少高效和可擴展的模擬環境阻礙著新一代Warehouse-Scale Computers (WSCs) 的發展。

來自加州大學伯克利Krste Asanovi教授團隊的FireSim填補了這一項空白;也正是主推RISC-V的團隊。通過利用云端FPGA,FireSim結合基于RISC-V的Rocket Chip和cycle-accurateC++ switch模型可以模擬多達4096個核心和16TB存儲器。

同樣是來自伯克利的另一項工作,針對GarbageCollection設計了硬件加速器,并且集成到RocketChip 當中。整個系統從JavaVM到Linux再到FPGA全面地展示了端到端模擬能力。同時,在關于RISC-V對計算機體系結構研究的workshop(CARRV)當中,基于RISC-V 的工具鏈在包括模擬器,加密,和數字信號處理中都影響著學界和業界。

大會概況:28%的論文有關神經網絡加速器,清華大學入選一篇

1、神經網絡加速依舊火熱

神經網絡加速器依舊持續火熱,除兩個機器學習系統分會場外,還分布于云數據中心、新型應用加速、新型計算范式、內存持久性、新型存儲器、移動平臺等各大分會場。

神經網絡加速器共計接收18篇論文(28%),從研究內容可分為:DNN推理加速(10篇)、移動系統(3篇)、脈沖神經網絡(2篇)、DNN訓練加速(1篇)、GAN加速(1篇)、編程指令集架構(1篇)。

論文主要來自于美國,包括微軟、伊利諾伊大學香檳分校(UIUC)、威斯康星大學、密歇根大學、康奈爾大學、羅徹斯特大學、喬治亞理工學院、加州大學圣地亞哥分校(UCSD)、加州大學伯克利分校(UCB)、佛羅里達大學、ARM、高通(Qualcomm)、英偉達(NVIDIA)等,4篇來自于亞洲:清華大學、首爾國立大學(SNU)和新加坡國立大學(NUS),2篇來自于歐洲加泰羅尼亞理工大學(UPC)。

本屆大會對于DNN推理階段的加速優化呈現多樣化,以DNN推理加速的10篇論文為例,3篇針對稀疏網絡(解決自動語音識別系統中由于網絡裁剪導致的分類置信度下降和執行時間增長的問題;通過預測零狀態輸出神經元從而去除與其相關的冗余計算)、3篇針對低比特量化網絡(利用數據量化后狀態有限的特性從而共享重復的神經元激活狀態和權重參數狀態,達到減小計算的目的;設計支持量化比特數可變的加速器方案,提高對量化網絡支持的通用性)、2篇進行SRAM緩存計算(Processing in SRAM)、1篇進行eDRAM刷新優化(對于生命周期較短的數據不進行刷新,從而極大降低功耗)、1篇面向FPGA數據中心(提升數據中心對于用戶推理需求的響應時間)。

2、機器學習與系統得到深入探討

機器學習與系統設計之間的關系也在此次大會中進行了深入的探討,主要包括兩個方向:1)為機器學習應用構建加速系統;2)使用機器學習方法加速系統設計。大會第一天keynote由Kim Hazelwood介紹Facebook在第一個技術方向的嘗試和探索。Kim認為除計算瓶頸外,存儲瓶頸和軟件瓶頸也是系統構建時要考慮的關鍵因素。AIDArchworkshop討論了第二個技術方向。DanielSchanwz 教授和Cliff Young介紹了體系結構領域中使用機器學習方法來優化系統設計,以及軟硬件聯合優化的重要性和可能性。

3、基礎框架和模擬器

DNN加速器模擬:來自Gerogia Tech和NVIDIA Research的團隊在這次ISCA tutorial公布了兩個支持快速高效DNN加速器設計的工具:MAESTRO和MAERI。MAESTRO是針對不同卷積dataflow的分析工具。用戶可以通過改變loop-ordering,loop unrolling, spatial tiling和temporal tiling來模擬不同的dataflow,并且能在用戶定義的處理單元數目和緩存大小下估計運行時間和能耗。參數化和模塊化的DNN加速器生成器MAERI可以輸出RTL,并且通過ASIC或者FPGA設計流程估計性能功耗和面積。目前MAERI支持卷積,LSTM,pooling,和全連接層,已經完整的DNN模型運行。

GPU模型。AMD Research在gem5中擴展了APU模型。該模型使用基于GCN gen3ISA 的GPU時序并且支持開源Radeon OpenCompute Platform (ROCm)。用戶可以在gem5APU 模擬器上運行C++,OpenMP,HIP,和OpenCL編寫的應用,包括傳統的GPU workloads和機器學習應用。由于APU中GPU直接與主存交互,針對GPU的訪存優化得以更方便在gem5中驗證。除此之外,來自康奈爾大學的研究人員在workshop中展示了在gem5中基于RISC-V的多核心模擬器。

4、其他方向

對于編程語言的動態功能以及系統進行從體系結構層面進行支持,在今年ISCA的論文中受到了廣泛的關注。在編程語言的動態功能支持上,來自UCB的Martin Maas等人展示了針對Java內存管理中垃圾回收的硬件優化。對于系統層面的支持,本次ISCA錄用文章的關注點仍然在內存,包括內存模型,虛擬內存,內存一致性,內存持久性(Memory Persistence)。

除此之外,新型互連架構也受到了一定程度的關注,這些互連架構有一些關注于芯片間的互連,另一些則關注分布式系統中的網絡互聯。最后,關于資源分配,一個傳統操作系統最關鍵的任務之一,來自UIUC的Josep Torrellas教授等人提出了基于健壯控制理論(Robust Control Theory)的分層資源控制方法,極大提升資源分配的效率。

綜上所述,在今年ISCA中,從體系結構對于操作系統以及編程語言的支持,尤其是內存系統的支持,仍然有廣泛的關注。這其中的許多研究,都圍繞著基于加速器的異構系統以及基于持久性內存的系統所帶來的問題。我們期待這些研究對于實際的新興架構部署能提供強有力幫助。

-

摩爾定律

+關注

關注

4文章

632瀏覽量

78938 -

軟硬件協同

+關注

關注

0文章

5瀏覽量

6319 -

神經網絡加速器

+關注

關注

0文章

13瀏覽量

3596

原文標題:圖靈獎得主展望新黃金時代,拿什么拯救摩爾定律?

文章出處:【微信號:AI_era,微信公眾號:新智元】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

AI時代的存儲墻,哪種存算方案才能打破?

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

“自我實現的預言”摩爾定律,如何繼續引領創新

半導體行業能否走出低谷,中國影響幾何?

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

英特爾CEO基辛格:摩爾定律放緩,仍能制造萬億晶體

英特爾CEO基辛格:摩爾定律仍具生命力,且仍在推動創新

后摩爾定律時代,Chiplet落地進展和重點企業布局

“超越摩爾”新進展,2023 SITRI DAY發布“MEMS標準工藝模塊”和“90nm硅光集成工藝”

如何走出摩爾定律困境?摩爾定律領域的困境與研究方向詳細概述

如何走出摩爾定律困境?摩爾定律領域的困境與研究方向詳細概述

評論