為什么E-MOSFET的閾值電壓隨著半導(dǎo)體襯底摻雜濃度的提高而增大?而隨著溫度的升高而下降?

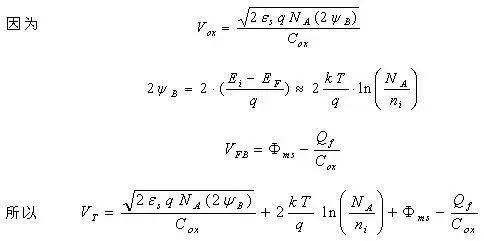

E-MOSFET的閾值電壓就是使半導(dǎo)體表面產(chǎn)生反型層(導(dǎo)電溝道)所需要加的柵極電壓。對(duì)于n溝道E-MOSFET,當(dāng)柵電壓使得p型半導(dǎo)體表面能帶向下彎曲到表面勢(shì)ψs≥2ψB時(shí),即可認(rèn)為半導(dǎo)體表面強(qiáng)反型,因?yàn)檫@時(shí)反型層中的少數(shù)載流子(電子)濃度就等于體內(nèi)的多數(shù)載流子濃度(~摻雜濃度);這里的ψB是半導(dǎo)體Fermi勢(shì),即半導(dǎo)體禁帶中央與Fermi能級(jí)之差。閾值電壓VT包含有三個(gè)部分的電壓(不考慮襯偏電壓時(shí)):柵氧化層上的電壓降Vox;半導(dǎo)體表面附近的電壓降2ΨB:抵消MOS系統(tǒng)中各種電荷影響的電壓降——平帶電壓VF。

在閾值電壓的表示式中,與摻雜濃度和溫度有關(guān)的因素主要是半導(dǎo)體Fermi勢(shì)ψB。當(dāng)p型半導(dǎo)體襯底的摻雜濃度NA提高時(shí),半導(dǎo)體Fermi能級(jí)趨向于價(jià)帶頂變化,則半導(dǎo)體Fermi勢(shì)ψB增大,從而就使得更加難以達(dá)到ψs≥2ψB的反型層產(chǎn)生條件,所以閾值電壓增大。

當(dāng)溫度T升高時(shí),半導(dǎo)體Fermi能級(jí)將趨向于禁帶中央變化,則半導(dǎo)體Fermi勢(shì)ψB減小,從而導(dǎo)致更加容易達(dá)到ψs≥2ψB的反型層產(chǎn)生條件,所以閾值電壓降低。

(2)為什么E-MOSFET的源-漏電流在溝道夾斷之后變得更大、并且是飽和的(即與源-漏電壓無(wú)關(guān))?

【答】E-MOSFET的溝道夾斷是指柵極電壓大于閾值電壓、出現(xiàn)了溝道之后,源-漏電壓使得溝道在漏極端夾斷的一種狀態(tài)。實(shí)際上,溝道在一端夾斷并不等于完全沒(méi)有溝道。當(dāng)柵電壓小于閾值電壓時(shí),則完全沒(méi)有溝道,這是不導(dǎo)電的狀態(tài)——截止?fàn)顟B(tài)。而溝道的夾斷區(qū)由于是耗盡區(qū),增加的源-漏電壓也主要是降落在夾斷區(qū),則夾斷區(qū)中存在很強(qiáng)的電場(chǎng),只要有載流子到達(dá)夾斷區(qū)的邊緣,即可被電場(chǎng)拉過(guò)、從漏極輸出,因此夾斷區(qū)不但不阻止載流子通過(guò),而相反地卻能夠很好地導(dǎo)電,所以有溝道、并且溝道在一端夾斷的狀態(tài),是一種很好的導(dǎo)電狀態(tài),則溝道夾斷之后的輸出源-漏電流最大。

E-MOSFET的溝道在漏極端夾斷以后,由于夾斷區(qū)基本上是耗盡區(qū),則再進(jìn)一步增加的源-漏電壓,即將主要是降落在夾斷區(qū),這就使得未被夾斷的溝道——剩余溝道的長(zhǎng)度基本上保持不變;而在溝道夾斷之后的源-漏電流主要是決定于剩余溝道的長(zhǎng)度,所以這時(shí)的源-漏電流也就基本上不隨源-漏電壓而變化——輸出電流飽和。

(3)為什么短溝道E-MOSFET的飽和源-漏電流并不完全飽和?

對(duì)于短溝道MOSFET,引起輸出源-漏電流飽和的原因基本上有兩種:一種是溝道夾斷所導(dǎo)致的電流飽和;另一種是速度飽和所導(dǎo)致的電流飽和。

對(duì)于溝道夾斷的飽和,因?yàn)閵A斷區(qū)的長(zhǎng)度會(huì)隨著其上電壓的增大而有所增大,則使得剩余溝道的長(zhǎng)度也將隨著源-漏電壓而減短,從而就會(huì)引起源-漏電流相應(yīng)地隨著源-漏電壓而有所增大——輸出電流不完全飽和。不過(guò),這種電流不飽的程度與溝道長(zhǎng)度有關(guān):對(duì)于長(zhǎng)溝道MOSFET,這種夾斷區(qū)長(zhǎng)度隨源-漏電壓的變化量,相對(duì)于整個(gè)溝道長(zhǎng)度而言,可以忽略,所以這時(shí)溝道夾斷之后的源-漏電流近似為“飽和”的;但是對(duì)于短溝道MOSFET,這種夾斷區(qū)長(zhǎng)度隨源-漏電壓的變化量,相對(duì)于整個(gè)溝道長(zhǎng)度而言,不能忽略,所以溝道夾斷之后的源-漏電流將會(huì)明顯地隨著源-漏電壓的增大而增加——不飽和。

對(duì)于速度飽和所引起的電流飽和情況,一般說(shuō)來(lái),當(dāng)電場(chǎng)很強(qiáng)、載流子速度飽和之后,再進(jìn)一步增大源-漏電壓,也不會(huì)使電流增大。因此,這時(shí)的飽和電流原則上是與源-漏電壓無(wú)關(guān)的。

對(duì)于短溝道MOSFET,還有一個(gè)導(dǎo)致電流不飽和的重要原因,即所謂DIBL(漏極感應(yīng)源端勢(shì)壘降低)效應(yīng)。因?yàn)樵磪^(qū)與溝道之間總是存在一個(gè)高低結(jié)所造成的勢(shì)壘,當(dāng)源-漏電壓越高,就將使得該勢(shì)壘越低,則通過(guò)溝道的源-漏電流越大,因此輸出電流不會(huì)飽和。

總之,導(dǎo)致短溝道MOSFET電流不飽和的因素主要有溝道長(zhǎng)度調(diào)制效應(yīng)和DIBL效應(yīng)。

(4)為什么E-MOSFET的飽和源-漏電流與飽和電壓之間具有平方的關(guān)系?

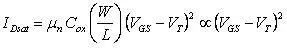

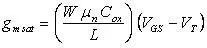

【答】增強(qiáng)型MOSFET(E-MOSFET)的飽和源-漏電流表示式為

飽和電壓(VGS-VT)就是溝道夾斷時(shí)的源-漏電壓。在MOSFET的轉(zhuǎn)移特性(IDsat~VGS)曲線上,E-MOSFET的飽和源-漏電流IDsat與飽和電壓(VGS-VT)的關(guān)系即呈現(xiàn)為拋物線。導(dǎo)致出現(xiàn)這種平方關(guān)系的原因有二:

①溝道寬度越大,飽和源-漏電流越大,飽和電壓也就越高;

②電流飽和就對(duì)應(yīng)于溝道夾斷,而夾斷區(qū)即為耗盡層,其寬度與電壓之間存在著平方根的關(guān)系,這就導(dǎo)致以上的平方結(jié)果。正因?yàn)镸OSFET具有如此平方的電流-電壓關(guān)系,所以常稱其為平方率器件。

(5)為什么一般MOSFET的飽和源-漏電流具有負(fù)的溫度系數(shù)?

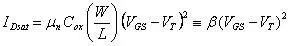

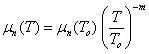

【答】MOSFET的飽和源-漏電流可表示為

在此關(guān)系中,因?yàn)椴牧?a target="_blank">參數(shù)和器件結(jié)構(gòu)參數(shù)均與溫度的關(guān)系不大,則與溫度有關(guān)的因素主要有二:閾值電壓VT和載流子遷移率μn。

由于MOSFET的閾值電壓VT具有負(fù)的溫度系數(shù),所以,隨著溫度的升高,就使得MOSFET的輸出飽和源-漏電流隨之增大,即導(dǎo)致電流具有正的溫度系數(shù)。

而載流子遷移率μn,在室溫附近一般將隨著溫度的升高而下降(主要是晶格振動(dòng)散射起作用):

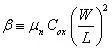

式中To=300K,m=1.5~2.0。遷移率的這種溫度特性即導(dǎo)致MOSFET的增益因子

也具有負(fù)的溫度系數(shù)。從而,隨著溫度的升高,遷移率的下降就會(huì)導(dǎo)致MOSFET的輸出源-漏電流減小,即電流具有負(fù)的溫度系數(shù)。

綜合以上閾值電壓和載流子遷移率這兩種因素的不同影響,則根據(jù)MOSFET飽和電流的表示式即可得知:

①當(dāng)飽和電壓(VGS-VT)較大(即VGS>>VT)時(shí),閾值電壓溫度關(guān)系的影響可以忽略,則輸出源-漏電流的溫度特性將主要決定于載流子遷移率的溫度關(guān)系,即具有負(fù)的溫度系數(shù)(溫度升高,IDS下降);

②當(dāng)飽和電壓(VGS-VT)較小(即VGS~VT)時(shí),則輸出源-漏電流的溫度特性將主要決定于閾值電壓的溫度關(guān)系,從而具有正的溫度系數(shù)(溫度升高,IDS也增大)。

而對(duì)于一般的MOSFET,為了獲得較大的跨導(dǎo),往往把飽和電壓(VGS-VT)選取得較大,因此可以不考慮閾值電壓的影響,于是飽和源-漏電流通常都具有負(fù)的溫度系數(shù)。也因此,一般的MOSFET都具有一定的自我保護(hù)的功能,則可以把多個(gè)管芯直接并聯(lián)起來(lái),也不會(huì)出現(xiàn)因電流分配不均勻而引起的失效;利用這種并聯(lián)管芯的辦法即可方便地達(dá)到增大器件輸出電流的目的(實(shí)際上,功率MOSFET就是采用這種措施來(lái)實(shí)現(xiàn)大電流的)。

(6)為什么MOSFET的飽和區(qū)跨導(dǎo)大于線性區(qū)的跨導(dǎo)?

【答】飽和區(qū)與線性區(qū)都是出現(xiàn)了溝道的狀態(tài),但是它們的根本差別就在于溝道是否被夾斷。電壓對(duì)溝道寬度的影響是:柵極電壓將使溝道寬度均勻地發(fā)生變化,源-漏電壓將使溝道寬度不均勻地發(fā)生變化(則會(huì)導(dǎo)致溝道首先在漏極端夾斷)。

在線性區(qū)時(shí),由于源-漏電壓較低,則整個(gè)溝道的寬度從頭到尾變化不大,這時(shí)柵極電壓控制溝道導(dǎo)電的能力相對(duì)地較差一些,于是跨導(dǎo)較小。同時(shí),隨著源-漏電壓的增大,溝道寬度的變化增大,使得漏端處的溝道寬度變小,則柵極電壓控制溝道導(dǎo)電的能力增強(qiáng),跨導(dǎo)增大。

而在飽和區(qū)時(shí),源-漏電壓較高,溝道夾斷,即在漏極端處的溝道寬度為0,于是柵極電壓控制溝道導(dǎo)電的能力很強(qiáng)(微小的柵極電壓即可控制溝道的導(dǎo)通與截止),所以這時(shí)的跨導(dǎo)很大。因此,飽和區(qū)跨導(dǎo)大于線性區(qū)跨導(dǎo)。

可見,溝道越是接近夾斷,柵極的控制能力就越強(qiáng),則跨導(dǎo)也就越大;溝道完全夾斷后,電流飽和,則跨導(dǎo)達(dá)到最大——飽和跨導(dǎo)。

(7)為什么MOSFET的飽和跨導(dǎo)一般與飽和電壓成正比?但為什么有時(shí)又與飽和電壓成反比?

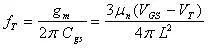

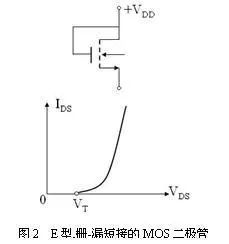

【答】①在源-漏電壓VDS一定時(shí):由E-MOSFET的飽和電流IDsat對(duì)柵電壓的微分,即可得到飽和跨導(dǎo)gmsat與飽和電壓(VGS-VT)成正比:

這種正比關(guān)系的得來(lái),是由于飽和電壓越高,就意味著溝道越不容易夾斷,則導(dǎo)電溝道厚度必然較大,因此在同樣?xùn)艠O電壓下的輸出源-漏電流就越大,從而跨導(dǎo)也就越大。

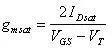

②在飽和電流IDsat一定時(shí):飽和跨導(dǎo)gmsat卻與飽和電壓(VGS-VT)成反比:

這是由于飽和電壓越高,就意味著溝道越難以?shī)A斷,則柵極的控制能力就越小,即跨導(dǎo)越小。

總之,在源-漏電壓一定時(shí),飽和跨導(dǎo)與飽和電壓成正比,而在源-漏電流一定時(shí),飽和跨導(dǎo)與飽和電壓成反比。

這種相反的比例關(guān)系,在其他場(chǎng)合也存在著,例如功耗P與電阻R的關(guān)系:當(dāng)電流一定時(shí),功耗與電阻成正比(P=IV=I2R);當(dāng)電壓一定時(shí),功耗與電阻成反比(P=IV=V2/R)。

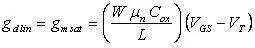

(8)為什么MOSFET的線性區(qū)源-漏電導(dǎo)等于飽和區(qū)的跨導(dǎo)(柵極跨導(dǎo))?

【答】MOSFET的線性區(qū)源-漏電導(dǎo)gdlin和飽和區(qū)的柵極跨導(dǎo)gmsat,都是表征電壓對(duì)溝道導(dǎo)電、即對(duì)源-漏電流控制能力大小的性能參數(shù)。

在線性區(qū)時(shí),溝道未夾斷,但源-漏電壓將使溝道寬度不均勻;這時(shí)源-漏電壓的變化,源-漏電導(dǎo)gdlin即表征著在溝道未夾斷情況下、源-漏電壓對(duì)源-漏電流的控制能力,這種控制就是通過(guò)溝道寬度發(fā)生不均勻變化而起作用的。

而飽和區(qū)的柵極跨導(dǎo)——飽和跨導(dǎo)gmsat是表征著在溝道夾斷情況下、柵-源電壓對(duì)源-漏電流的控制能力,這時(shí)剩余溝道的寬度已經(jīng)是不均勻的,則這種控制也相當(dāng)于是通過(guò)溝道寬度發(fā)生不均勻變化而起作用的,因此這時(shí)的柵極跨導(dǎo)就等效于線性區(qū)源-漏電導(dǎo):

(9)為什么在E-MOSFET的柵-漏轉(zhuǎn)移特性上,隨著柵-源電壓的增大,首先出現(xiàn)的是飽和區(qū)電流、然后才是線性區(qū)電流?

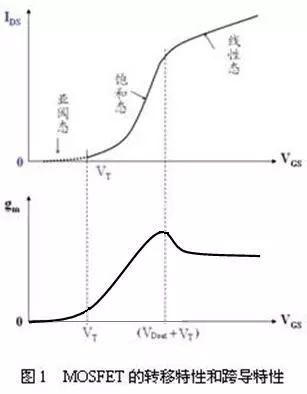

【答】E-MOSFET的柵-漏轉(zhuǎn)移特性如圖1所示。在柵-源電壓VGS小于閾值電壓VT時(shí),器件截止(沒(méi)有溝道),源-漏電流電流很小(稱為亞閾電流)。

在VGS>VT時(shí),出現(xiàn)溝道,但如果源-漏電壓VDS=0,則不會(huì)產(chǎn)生電流;只有在VGS>VT和VDS>0時(shí),才會(huì)產(chǎn)生電流,這時(shí)必然有VDS >(VGS-VT),因此MOSFET處于溝道夾斷的飽和狀態(tài),于是源-漏電流隨柵-源電壓而平方地上升。相應(yīng)地,飽和跨導(dǎo)隨柵-源電壓而線性地增大,這是由于飽和跨導(dǎo)與飽和電壓(VGS-VT)成正比的緣故。

而當(dāng)柵-源電壓進(jìn)一步增大,使得VDS<(VGS-VT)時(shí),則MOSFET又將轉(zhuǎn)變?yōu)闇系牢磰A斷的線性工作狀態(tài),于是源-漏電流隨柵-源電壓而線性地增大。這時(shí),跨導(dǎo)不再變化(與柵電壓無(wú)關(guān))。

(10)為什么MOSFET的電流放大系數(shù)截止頻率fT與跨導(dǎo)gm成正比?

【答】MOSFET的fT就是輸出電流隨著頻率的升高而下降到等于輸入電流時(shí)的頻率。器件的跨導(dǎo)gm越大,輸出的電流就越大,則輸出電流隨頻率的下降也就越慢,從而截止頻率就越大,即fT與gm有正比關(guān)系:

由于fT與gm的正比關(guān)系,就使得fT與飽和電壓(VGS-VT)也有正比關(guān)系,從而高頻率就要求較大的飽和電壓。

(11)為什么提高M(jìn)OSFET的頻率與提高增益之間存在著矛盾?

【答】MOSFET的高頻率要求它具有較大的跨導(dǎo),而在源-漏電壓一定的情況下,較大的跨導(dǎo)又要求它具有較大的飽和電壓(VGS-VT),所以高頻率也就要求有較大的飽和電壓。

因?yàn)镸OSFET的電壓增益是在源-漏電流一定的情況下、輸出電壓VDS對(duì)柵-源電壓VGS的微分,則飽和狀態(tài)的電壓增益Kvsat將要求器件具有較小的飽和電壓(VGS-VT):

這是由于在IDsat一定時(shí),飽和電壓越低,飽和跨導(dǎo)就越大,故Kvsat也就越大。

可見,提高頻率與增大電壓增益,在對(duì)于器件飽和電壓的要求上存在著矛盾。因此,在工作電流IDsat一定時(shí),為了提高電壓增益,就應(yīng)該減小(VGS-VT)和增大溝道長(zhǎng)度L。這種考慮對(duì)于高增益MOSFET具有重要的意義;但是這種減小(VGS-VT)的考慮卻對(duì)于提高截止頻率不利。

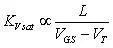

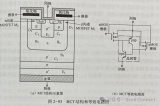

(12)為什么E-MOSFET的柵-源短接而構(gòu)成的MOS二極管存在著“閾值損失”?

【答】這種集成MOS二極管的連接方式及其伏安特性如圖2所示。因?yàn)闁艠O與漏極短接,則VGS=VDS。因此,當(dāng)電壓較小(VGS=VDS

由于VGS=VDS,所以這種二極管的輸出伏安特性將與轉(zhuǎn)移特性完全一致。因?yàn)镸OSFET的飽和輸出電流IDsat與飽和電壓(VGS-VT)之間有平方關(guān)系,所以該二極管在VGS=VDS≥VT時(shí)的輸出伏安特性為拋物線關(guān)系,并且這也就是其轉(zhuǎn)移特性的關(guān)系。

所謂閾值損失,例如在門電路中,是輸出高電平要比電源電壓低一個(gè)閾值電壓大小的一種現(xiàn)象。由E型,柵-漏短接的MOS二極管的伏安特性可以見到,當(dāng)其輸出源-漏電流IDS降低到0時(shí),其源-漏電壓VDS也相應(yīng)地降低到VT。這就意味著,這種二極管的輸出電壓最低只能下降到VT,而不能降低到0。這種“有電壓、而沒(méi)有電流”的性質(zhì),對(duì)于用作為有源負(fù)載的這種集成MOS二極管而言,就必將會(huì)造成閾值損失。

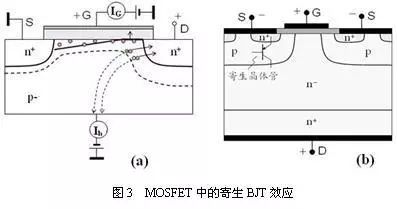

(13)為什么在MOSFET中存在有BJT的作用?這種作用有何危害?

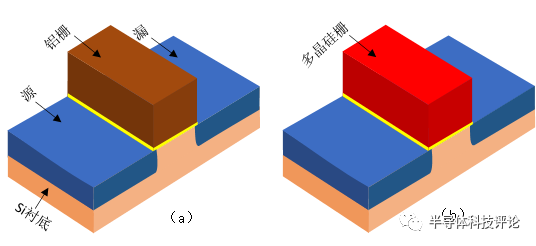

【答】①對(duì)于常規(guī)的MOSFET:如圖3(a)所示,源區(qū)、漏區(qū)和p襯底即構(gòu)成了一個(gè)npn寄生晶體管。當(dāng)溝道中的電場(chǎng)較強(qiáng)時(shí),在夾斷區(qū)附近的電子即將獲得很大的能量而成為熱電子,然后這些熱電子通過(guò)與價(jià)電子的碰撞、電離,就會(huì)形成一股流向襯底的空穴電流Ib;該過(guò)襯底電流就是寄生晶體管的基極電流,在熱電子效應(yīng)較嚴(yán)重、襯底電流較大時(shí),即可使寄生晶體管導(dǎo)通,從而破壞了MOSFET的性能。這種熱電子效應(yīng)的不良影響往往是較短溝道MOSFET的一種重要失效機(jī)理。

②對(duì)于CMOS器件:在CMOS器件的芯片中,存在著npnp的四層結(jié)構(gòu)——晶閘管。當(dāng)其中的BJT因?yàn)闊犭娮有?yīng)而導(dǎo)通時(shí),即可發(fā)生所謂“閂鎖效應(yīng)”、而導(dǎo)致器件失效。

③對(duì)于VDMOSFET:觀察圖3(b)中的結(jié)構(gòu),即可見到,當(dāng)器件正向?qū)〞r(shí),其中存在一個(gè)工作于放大狀態(tài)的寄生n-p-n晶體管(n+源區(qū)是發(fā)射區(qū),n-外延層是集電區(qū),p溝道是基區(qū))。該寄生晶體管的可能導(dǎo)電通道是與MOSFET的ID相并聯(lián)的,故在VDMOSFET工作時(shí),必須要注意防止寄生晶體管導(dǎo)通;否則,寄生晶體管的導(dǎo)通就可能引起二次擊穿,使得功率MOSFET完全失去功能。

為了避免VDMOSFET在正向工作時(shí)、其中寄生n-p-n晶體管的導(dǎo)通,可以設(shè)法使寄生晶體管的電流放大系數(shù)變得很小、甚至減至為0——采用“陰極短路技術(shù)”,即把寄生晶體管的發(fā)射極與基極短接起來(lái),工藝上就通過(guò)把發(fā)射區(qū)(源極區(qū))的金屬電極延伸到溝道體區(qū)的表面上來(lái)實(shí)現(xiàn)。因?yàn)檫@種陰極短路結(jié)構(gòu)截?cái)嗔税l(fā)射極注入載流子的功能,所以能夠防止寄生晶體管的導(dǎo)通。

對(duì)于VDMOSFET,在采用了陰極短路結(jié)構(gòu)之后,實(shí)際上又恰恰在器件內(nèi)部形成了一個(gè)p-n-n+二極管,這個(gè)二極管與VDMOSFET是反向并聯(lián)的,這也就順便地在VDMOSFET中設(shè)置了一個(gè)阻尼二極管(續(xù)流二極管),該二極管對(duì)于泄放反向電動(dòng)勢(shì)、防止主體晶體管的擊穿具有重要作用。

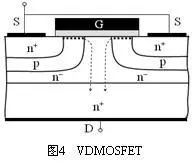

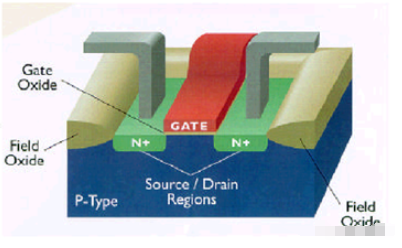

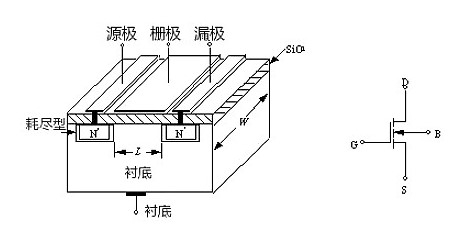

(14)為什么在VDMOSFET中存在有JFET的作用?有何不良影響?

【答】如圖4所示,源-漏電流是從芯片表面向下流動(dòng)的,并在電流通路的兩側(cè)是pn結(jié),因此這種電流輸運(yùn)的過(guò)程,從工作原理上來(lái)看,就相當(dāng)于是一個(gè)寄生JFET。從而可以把VDMOSFET等效為一個(gè)MOSFET與一個(gè)寄生JFET的串聯(lián)組合,其中很大部分n-漂移區(qū)就相當(dāng)于是寄生JFET的溝道。

由于JFET的輸出交流電阻非常大,同時(shí)也因?yàn)檩^高的源-漏電壓而具有很大的輸出直流電阻,所以就使得VDMOSFET的導(dǎo)通電阻大大增加,因此n-漂移區(qū)的厚度和摻雜濃度對(duì)整個(gè)器件性能的影響都較大。

為了消除VDMOSFET中寄生JFET的影響,以降低導(dǎo)通電阻,就必須在結(jié)構(gòu)上加以改變,由此發(fā)展出了V形槽柵、U形槽柵和溝槽(Trench)柵等結(jié)構(gòu)的MOSFET。

(15)IGBT和MCT都是MOS柵極控制的功率場(chǎng)效應(yīng)晶體管,為什么說(shuō)它們是兩種完全不同的器件?

【答】IGBT(絕緣柵雙極型場(chǎng)效應(yīng)晶體管)和MCT(MOS控制晶閘管)的共同點(diǎn)主要有:

①都是MOS柵極控制的器件,則具有功率場(chǎng)效應(yīng)晶體管的優(yōu)點(diǎn);

②在結(jié)構(gòu)上,其中都存在著四層、三結(jié)的晶閘管結(jié)構(gòu),因此在一定條件下會(huì)出現(xiàn)陽(yáng)極電流閂鎖效應(yīng);

③它們都可以采用多個(gè)元胞并聯(lián)的結(jié)構(gòu),因此可以獲得很大的工作電流;

③它們都是有兩種載流子參與工作的器件,因此都是雙極型的場(chǎng)效應(yīng)晶體管,導(dǎo)通電阻低,但開關(guān)速度也相對(duì)地要比MOSFET的低。

IGBT和MCT的最大不同點(diǎn)就在于它們的工作狀態(tài)和性質(zhì)不相同,因此說(shuō)它們是兩種完全不同的器件:

①IGBT的工作電流主要是通過(guò)MOS溝道的電流,而其中的晶閘管電流是需要極力避免的(IGBT的最大工作電流——擎住電流就是其中晶閘管不導(dǎo)通時(shí)的電流),因此從本質(zhì)上來(lái)看,IGBT基本上是一種MOSFET,因此IGBT具有MOS器件的許多優(yōu)點(diǎn),例如較強(qiáng)的柵極的控制能力和較低的驅(qū)動(dòng)功率(因?yàn)橛泻艽蟮妮斎腚娮韬洼^小的輸入電容之故)。

而MCT與IGBT的恰恰相反,它的工作電流主要是晶閘管電流,至于MOS溝道的電流,則主要是起著觸發(fā)晶閘管導(dǎo)通或者關(guān)斷的作用,不是MCT的主要工作電流,因此從本質(zhì)上來(lái)看,MCT基本上是一種晶閘管——雙極型器件,從而MCT具有導(dǎo)通電阻很低、耐壓很高、功率容量很大的優(yōu)點(diǎn)。

②IGBT雖然在本質(zhì)上是一種MOS器件,但又不同于一般的MOSFET,因?yàn)镮GBT在導(dǎo)通工作時(shí),有少數(shù)載流子注入到高阻的耐壓層(漂移區(qū)),可以產(chǎn)生電導(dǎo)調(diào)制,則它的導(dǎo)通電阻較小,增大了器件的電流容量(電流密度要比VDMOSFET的高2~3倍);同時(shí)由于高阻耐壓層的引入而提高了工作電壓。因此IGBT的功率容量很大。只是IGBT的開關(guān)速度,由于少數(shù)載流子的引入而相應(yīng)地有所降低。

③雖然MCT本質(zhì)上是一種晶閘管,而且MOS柵極可以關(guān)斷陽(yáng)極電流,但MCT又不同于一般的可關(guān)斷晶閘管(GTO)。因?yàn)镸CT實(shí)際上是一種把單極型的MOSFET與雙極型的晶閘管組合而成的復(fù)合型器件,也是一種所謂Bi-MOS器件,所以它具有MOS器件和雙極型器件二者的長(zhǎng)處:較強(qiáng)的柵極控制能力,較低的驅(qū)動(dòng)功率,較高的開關(guān)速度,較大功率容量。

-

MOSFET

+關(guān)注

關(guān)注

146文章

7099瀏覽量

212762 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27048瀏覽量

216436 -

IGBT

+關(guān)注

關(guān)注

1265文章

3762瀏覽量

248349 -

MOS

+關(guān)注

關(guān)注

32文章

1247瀏覽量

93506

原文標(biāo)題:15個(gè)MOS器件的重要特性

文章出處:【微信號(hào):eet-china,微信公眾號(hào):電子工程專輯】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MOS晶體管的靜態(tài)特性(一)

MOS管和IGBT是什么?有哪些區(qū)別?

MOS管的隔離作用解析

淺析MOS管的電壓特性

分析MOS管器件電路符號(hào)的詳情

基于深亞微米MOS器件溝道的熱噪聲淺析

MOS半導(dǎo)體器件原理下載

MOS器件的發(fā)展及各項(xiàng)技術(shù)的分析與介紹

關(guān)于MOS器件的發(fā)展與挑戰(zhàn)分析介紹

MOS門控晶閘管的工作原理解析

MOS器件深度解析 MOS器件有哪些重要特性

MOS器件深度解析 MOS器件有哪些重要特性

評(píng)論