0 引言

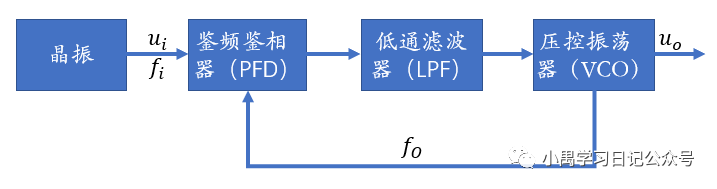

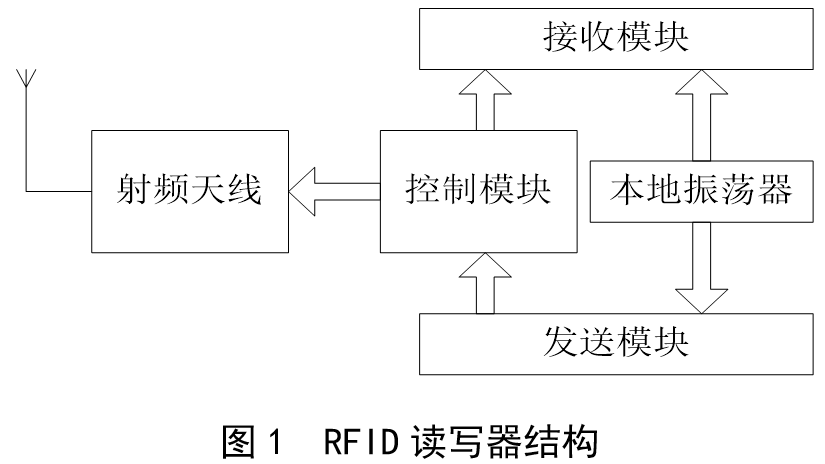

電荷泵鎖相環(Charge Pump Phase Locked Loop,CPPLL)因其易集成、低功耗、大動態捕獲范圍和小靜態相位誤差等優點而廣泛應用于偵測、導航、雷達、通信等設備中[1-3],其性能直接決定系統各項指標的好壞。典型CPPLL頻率合成器由鑒頻鑒相器(Phase Frequency Detector,PFD)、電荷泵(CP)、環路濾波器(LPF)、壓控振蕩器(VCO)和可編程分頻器(DIV)組成,如圖1所示。

PFD是CPPLL的核心部件之一,完成輸入參考信號與反饋信號(即VCO經DIV分頻后的信號)頻率和相位的檢測[4],產生后級CP充放電電流的開關控制信號。在該控制信號作用下,CP對LPF充放電,使VCO的調諧電壓發生相應的變化,進而改變VCO的諧振頻率。VCO振蕩輸出信號經DIV分頻后參與鑒頻鑒相,由此構成閉環反饋系統,實現鎖相倍頻功能。通常PFD存在死區效應[5],鑒相死區將造成鎖相環輸出相位抖動,惡化雜散和相噪特性,而減小甚至消除死區效應的主要辦法是改進其復位電路,增加延時單元,增大復位延時treset。但treset增大會使鑒相范圍減小,捕獲速度變慢[6]。

為此,本文基于TSMC 0.18 μm RF CMOS工藝,設計了一款具有數控延時單元的PFD,既消除了死區效應,又能保證良好的鑒相范圍和捕獲速度。同時,采用基于傳輸門和反相器的數控結構,擴展性和移植性強,對工藝、電壓、溫度等參數的變化不敏感,具有較強的適應性。

1 PFD的工作原理

圖1中所示PFD是一種典型的三態數字鑒頻鑒相器結構,因其電路簡單而被廣泛應用。該PFD由兩個D觸發器和一個與非門組成[4],實現輸入參考信號REF和反饋信號FB頻率和相位的比較,輸出與之匹配的UP和DN信號,控制電荷泵的工作狀態(充電、放電或保持)。

假設該PFD初始狀態時,REF和FB都為低電平,當REF上升沿先到來時,由其驅動的D觸發器被觸發,UP變為高電平。當FB上升沿到來時,由其驅動的D觸發器被觸發,DN變為高電平。此時UP和DN均為高電平,與非門產生復位信號,將兩個D觸發器復位,UP和DN均變為低電平。上述過程為REF相位超前時的PFD的工作情形,由類似分析,可得REF相位滯后時PFD的工作情形。可得,該PFD存在4種工作狀態,即UP和DN分別為00、01、10和11。其中11是一個瞬時狀態,是被禁止的,一旦出現,D觸發器會因復位而迅速進入00狀態,狀態轉換關系見圖2。

根據對PFD工作原理的分析,可以預見其工作波形如圖3所示。當REF頻率高于FB頻率時,UP輸出為不同脈寬的不規則脈沖信號,DN輸出保持低電平,且頻差越大,UP的均值越大。在UP信號作用下,CP充電支路間斷性開啟,使調諧電壓升高,從而使VCO頻率往高端調諧,因此REF和FB信號的頻差減小。此階段為PFD的鑒頻過程。當REF和FB信號的頻差減小為零時,PFD進入鑒相工作狀態。假設此時REF頻率等于FB頻率且相位超前,則UP輸出脈寬正比于兩者相位差的周期性脈沖信號,DN輸出保持低電平,UP信號作用又使PFD進入鑒頻工作狀態。在CPPLL頻率合成器未鎖定時,PFD不停地在鑒頻和鑒相工作狀態之間動態調整,直至達到頻率合成器鎖定,此時REF和FB信號的頻率相同,相位同步,從而保證了VCO輸出的頻率和相位穩定。REF頻率低于FB頻率以及兩者頻率相同時,REF相位滯后FB相位情況的工作過程與上述過程類似。

2 PFD電路設計與仿真

2.1 PFD的死區效應

上節著重分析了PFD的工作原理,并得到了其理想工作波形見圖3。當輸入參考信號REF與反饋信號FB的相位差很小時,UP或DN的脈沖寬度非常窄。由于結點電容的存在,會使得這個窄脈沖無法升到足夠高的電平,從而無法正常開啟電荷泵。即當PFD的輸入相位差Δφ小于某個特定值φ0時,CP沒有充放電電流存在,CPPLL已進入鎖定狀態,但FB信號相位與REF信號相位無法精確同步,VCO輸出信號存在相位抖動,導致相位噪聲和雜散特性惡化。該相位差為-φ0~φ0的區域被稱為PFD的死區[5],是PFD設計的主要關注點。

2.2 PFD的電路設計

為消除死區,需在PFD復位支路上增加延時單元,保證在輸入相位差即使為零的情況下,UP和DN依然存在一定脈寬的脈沖。但考慮到工藝、電壓、溫度等變化,難以準確給出該延時的長短。過短的延時無法有效消除死區,但過長的延時又會限制PFD的工作速度,因此需使復位延時足夠長,同時要盡可能短。基于上述考慮,本文設計了一種新型數控延時單元,通過配置3 bit控制字,實現8種不同長短的延時,靈活配置,切換延時長短,有效消除死區,優化環路性能,實際電路如圖4所示。

D觸發器采用真單相時鐘(TSPC)邏輯設計,見圖4(b),其結構簡單,速度較快,只有單相時鐘驅動,相噪特性較好,且在高頻工作條件下,具有一定的功耗優勢[7]。數控延時單元結構見圖4(c)所示,由b0、b1和b2三位高低電平控制。假設傳輸門延時為TC,兩級反相器延時為T0,則該延時單元在3位控制位為000時,獲得最短延時為3TC,而在控制位為111時,獲得最長延時為3TC+7T0。因此該延時單元的延時范圍即為3TC~3TC+7T0,步進為T0。合理設計傳輸門和反相器的尺寸,能夠獲得較優的延時。同時,該電路具有占用面積小、結構簡單、易擴展和易移植等優點。

2.3 仿真結果

該PFD基于TSMC 0.18 μm RF CMOS工藝設計,并在Cadence平臺下,采用Spectre工具進行仿真。圖5所示為未加延時單元時,PFD的實際工作波形。可見,由于邏輯門電路的延時,當輸入信號相位差很小時,存在極窄的脈沖信號,但該信號脈寬很窄,仍然可能會引起死區效應。圖6為增加數控延時單元后,b2、b1和b0從000變化到111時,兩個同頻同相輸入信號作用下,PFD的UP輸出波形,脈沖寬度隨控制位增大線性增加。圖7為b2、b1和b0為100時,不同頻輸入信號作用下,PFD的輸出波形。圖8為b2、b1和b0為100時,同頻不同相輸入信號作用下,PFD的輸出波形。仿真結果表明,本文設計的PFD在同頻同相信號作用下,PFD輸出存在一定脈寬的周期性脈沖,保證電荷泵電路開啟,可以消除死區,保證REF和FB信號達到同頻同相,通過改變控制位,能方便調節該脈沖寬度,使其保持合適的值。而在不同頻以及同頻不同相信號作用下,PFD也實現了正確的脈沖輸出,完成鑒頻鑒相功能。

3 結論

本文闡述了PFD的工作原理及其死區效應,提出了一種基于傳輸門和反相器結構的數控延時單元,并應用于PFD電路。該延時單元具有占用面積小、結構簡單、擴展性和移植性好等優點,應用前景好。仿真結果表明,所設計的PFD可以靈活控制延時長短,消除死區,實現了延時時間足夠長又盡可能短的設計目標。

-

D觸發器

+關注

關注

3文章

164瀏覽量

47738 -

鑒相器

+關注

關注

1文章

59瀏覽量

23196

發布評論請先 登錄

相關推薦

HMC3716LP4E數字鑒頻鑒相器

EV1HMC3716LP4數字鑒頻鑒相器評估板

一種用于高速鎖相環的零死區鑒頻鑒相器

利用FPGA延時鏈實現鑒相器時鐘數據恢復

隨機抖動時鑒頻鑒相器AD9548的特性

關于一種具有新型延時單元的鑒頻鑒相器的設計

關于一種具有新型延時單元的鑒頻鑒相器的設計

評論