旁路電容設計是一個比較常見的設計,但是旁路電容應該如何設計,設計多少旁路電容呢,時代的發展總是輪回的。就像《三國演義》話說天下大勢,分久必合,合久必分。

這是一個舊的布滿二極管和晶體管電腦板,執行一個簡單的DTL門功能(二極管晶體邏輯)。它大約是生產于20世紀60年代或70年代初。在我們配電設計課程中,我利用這塊電腦板提出了一個問題:你能數出這個板上有多少旁路電容么?

答案很驚人是零。為那為什么今天我們會在電路板上到處找尋位置來放置許多旁路電容,從而來降低我們電子產品的噪音呢?

現在不論是一個新的筆記本電腦或大型電腦板,我們都可以再上面找到幾百甚至幾千的電容。為了理解在短短數十年來發生的這一顯著變化的原因,我們必須研究旁路電容的作用和旁路電容是容如何工作的。

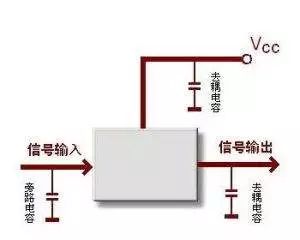

無論是模擬或數字,所有的電子電路,最終都會生成(與/或)程序交互電信號。其運作過程中,他們取自電源的供應電流不斷變化,需要根據實際運作情況來確定所需供應電流的大小。有時電路需要的電流較少,有時卻很多,這中不同需求的變化,也不斷改變著電源軌中的電流。這些不斷變化的電流流過電線以及印刷電路板上的電源和電子器件間的布線與層面,產生出電壓變化:

?V 是電壓變化, L代表在供應路徑中的電感;dI/dt隨時間發生改變的電流變化率。

小的電壓波動會被電子器件所接受,但每個電路為了保證正常工作都會有一個最高和最低限額。我們必須設法限制電源電壓的變化,否則它會因為所需電流的變化而產生變化。我們必須在電路和電源路徑上的串聯電感之間放置蓄存器。電容是一個很好的蓄存器,因為不同于電感,電容兩端的電壓(如果我們忽視它的寄生元件)將不會因為突然的電流改變而發生劇烈變化。

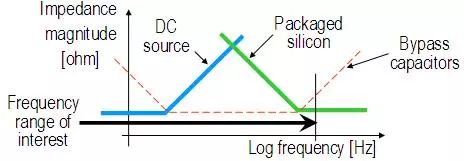

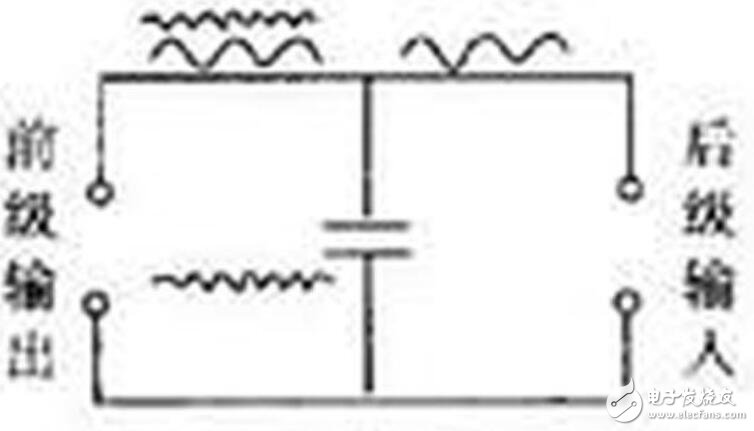

要確定我們什么樣的,以及多少電容器,比較方便的是從頻域為切入點來看問題。配電網絡 (PDN)可以以許多不同形式進行模擬,從簡單的集總等效電路,到詳細的網格模型。對于我們現在討論的,我想一個簡單的集總等效電路就夠了。

圖2中的圖表顯示了簡化的PDN等效阻抗。要創建一個熟悉Bode plot圖示,我們使用對數指標log-log在坐標軸上。請注意,為了簡單起見,該圖表只顯示阻抗值,但在以后的文章離我們會認識到,當我們使用PDN 阻抗來計算電路的表現的是很該階段是很重要的。

圖2.簡化的PDN集總等效阻抗

途中藍色的線代表了電源的阻抗,該電源可以是一個電池或電源轉換器。在低頻時候阻抗較低,但在更高頻率的時候,導線,布線,層面的連接電感最終將占據主導地位。綠色線代表了有源器件的阻抗。如果我們將該阻抗圖標對應在板封裝接口處,綠色線代表了有源器件連同封裝,以及封裝上PDN電容的阻抗。我們稱那些有源器件為“硅silicon”,但他們可以是任何類型的有源電路:在那塊舊的電腦板上有源器件是鍺晶體管。

綜上,藍色和綠色線產生了三角型的阻抗配置,并且在低頻和高頻的尾部是平坦的。如果在這個系統上不增加旁路電容,任何噪聲電流每次擊中這個三角峰值頻率時都可能會造成很多噪音。頻率軸上從左到右延伸的粗黑線是用來標明我們感興趣的頻率范圍,與 PDN阻抗有聯系的。我們感興趣的頻率范圍并不一定是連續的頻譜的一部分,特別是對連接到相同的電源電壓卻具有不同功能的復合電路來說。

如果要研究的頻率范圍不是在藍色和綠色的曲線構成的阻抗峰值所在頻率之間,那么該電路將正常工作而不需要增加旁路電容。如果電路的工作激發了阻抗峰值,那么我們需要增加旁路電容,以減少阻抗,從而降低噪音。圖標上紅色虛線代表一個旁路電容的阻抗,用來補充電源和有源器件的阻抗,也使寬頻帶的整體阻抗值變得較低。

那么,為什么在舊的電腦板上不需要旁路電容?主要是因為鍺晶體管的切換緩慢,并且時鐘頻率十分低,即短暫的開關電流不激發PDN阻抗的高阻抗部分。

今天的高速電子產品,復雜的電路功能和高時鐘頻率,大部分時間我們要關心的一個頻寬很寬的 PDN阻抗,因此,我們不能允許在源和負載阻抗之間有很高很明顯的阻抗峰值。因此,我們需要旁路電容器。如果我們快進幾十年里,我們可以很容易預測到電路板又將沒有旁路電容了。

因為,當分布式電源都足夠小,以至于我們可以把他們放置在非常接近負載的時候,則互連電感將變低,同時有源器件中的芯片和封裝電容量將更大,這樣我們將又回到電路板上不需要旁路電容的年代了。

-

旁路電容

+關注

關注

7文章

178瀏覽量

24710

原文標題:【小知識】旁路電容的前世今生

文章出處:【微信號:PCBTech,微信公眾號:EDA設計智匯館】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

旁路電容的作用與應用原理詳解

旁路電容的作用是什么

旁路電容有什么作用及用途

電容旁路作用是什么

旁路電容的發展與作用

旁路電容的發展與作用

評論