0 引言

鑒相技術是電力電子系統和測試控制中的關鍵技術之一,在儀器儀表、通信、導航定位、研究網絡相頻特性和鎖相環等測試中,經常需要測量兩列同頻信號的相位差。相較于模擬鑒相器,數字鑒相器的突出優點在于提供的鑒相范圍更寬,從而使鑒相更可靠,適用范圍也更廣。

傳統的鑒相方法主要有基于異或門的測量法和直線近似法等[1-3],這些鑒相方法鑒相范圍窄、輸入頻率低、線性度差,往往存在較大誤差。近年來,常用的數字鑒相方法有相關分析法、頻譜分析法等[4-6],其優點在于反應快和精度高,但算法相對復雜,鑒相范圍窄,輸入頻率也相對不高。AD9901在數字鑒相方面運用的相對較多,但鑒相范圍窄,同時在高頻時會出現非線性化現象[7]。本文設計了一種基于FPGA的數字鑒相器,既能消除高頻非線性,又能實現動態分頻和寬范圍鑒相。

1 系統原理與組成

數字鑒相器AD9901可實現線性相位檢測范圍,但是在高頻下AD9901會出現較為明顯的非線性化現象。這種非線性鑒相區的產生,是由于在線性檢測范圍兩端,參考信號和待測輸入信號相位接近,數字鑒相器輸出脈寬變得很窄和鑒相器擺速增大,從而導致相位增益迅速向鑒頻區(即最高和最低值處)拉近,而出現非線性化現象。其線性鑒相區間d為[8]:

由式(1)~式(3)可知,頻率越高,線性鑒相區間越窄。在高頻段通過FPGA分頻把頻率降低,可展寬線性區間,即可解決高頻非線性問題,同時鑒相范圍也大大提高。輸入信號和參考信號經過數字鑒相器系統后,即可得到不同相位差所對應的直流電壓。數字鑒相器系統原理框圖如圖1所示。

2 數字鑒相器設計

2.1 波形變換

本設計采用了超高速比較器AD8611,它的傳輸延遲只有4 ns,極大地減小了正弦波變換為方波的時間誤差,其波形變換電路如圖2所示。

2.2 FPGA分頻

通過FPGA進行可編程分頻設計,可以靈活改變分頻系數,分頻系數大且輸入頻率滿足設計需求。通過8位撥碼開關來設置分頻系數,分頻系數在1~255范圍內變化,其FPGA分頻流程圖如圖3所示。

本FPGA分頻設計可以實現任意整數分頻,其分頻原理如下:(1)偶數分頻:設計一個模N/2計數器,對輸入信號進行下降沿觸發計數,當計數值為N/2-1時輸出信號翻轉;(2)奇數分頻:采用兩個計數器分別對輸入信號進行上升沿和下降沿模N觸發計數,且各自控制產生一個N分頻的電平信號。一個計數器進行上升沿計數,當計數值為(N+1)/2時輸出信號翻轉,再當計數器清零時,再次翻轉就可得到一個占空比非50%的N分頻信號。同時另外一個計數器進行下降沿相同操作,得到另外一個N分頻信號。這兩個占空比非50%的N分頻信號進行相或運算,即可得到占空比為50%的N分頻信號。

使用ModelSim對FPGA分頻進行功能仿真,設定輸入信號頻率為10 MHz,20分頻后頻率為500 kHz;25分頻后頻率為400 kHz,分別如圖4(a)、圖4(b)所示。

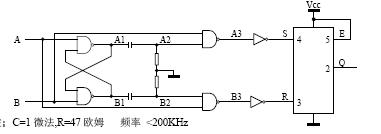

2.3 數字鑒相

AD9901能夠直接比較最高200 MHz的相位或頻率輸入信號。當輸入信號同頻率時,就工作在鑒相模式下,其數字鑒相電路如圖5所示。輸出占空比θ在-2π~0范圍內隨相位差 線性增加,其輸出占空比θ為:

線性增加,其輸出占空比θ為:

2.4 低通濾波

為了得到AD9901輸出的直流電平均值,需采用低通濾波器來消除噪聲和信號的交流分量。同時為了減小和抑制50 Hz工頻干擾的影響,設計了一個四階無源RLC巴特沃斯低通濾波器[9],其電路如圖6所示。

通過Multisim軟件對巴特沃斯低通濾波器的濾波性能進行仿真分析,其幅頻特性曲線如圖7所示。從圖中可以看出,其截止頻率大約為41 Hz,達到設計要求。

2.5 調理放大

為了調節AD9901輸出經低通濾波后的直流電平的均值范圍,采用由三級運算放大器OP07構成的信號調理放大電路,如圖8所示。第一級運放構成電壓跟隨器,對前后級電路起到隔離和緩沖作用;第二級運放構成反向加法器,起到調節零點的作用,最后一級運放構成反向比例放大器,以達到調節相位差變化時輸出電壓的變化幅度,并滿足后續相關電路處理要求。

3 測試結果與分析

測試過程中,由信號發生器產生兩路同頻同幅、不同相位差的正弦信號,其頻率為500 kHz,相位差為180°和270°情況下,用示波器觀察到AD9901的輸出波形,如圖9(a)、圖9(b)所示。

由式(4)可知,在 =-180°時,AD9901理論上輸出占空比為50%。在

=-180°時,AD9901理論上輸出占空比為50%。在 =-270°時,AD9901理論上輸出占空比為75%(AD9901有正相和倒相輸出),實測結果與理論值符合。

=-270°時,AD9901理論上輸出占空比為75%(AD9901有正相和倒相輸出),實測結果與理論值符合。

為了測試電路在0°~360°相位差范圍內線性情況,設置信號發生器輸出頻率為10 MHz,然后固定一路相位為0°,另一路相位每6°遞增至360°。未分頻和20分頻情況下,輸出電壓隨相位差變化曲線如圖10所示。由式(1)知:未分頻情況下,線性區間d=347.04°;20分頻情況下,線性區間d=359.35°。由測試數據可知,在0°~6°和354°~360°范圍內出現一定程度上的非線性。

其線性度:

其中,ΔYmax為校準曲線與擬合直線間的最大偏差,Y為滿量程輸出。由式(7)可知,未分頻情況下,線性度δ=-7.22%。FPGA進行20分頻,其線性度δ=-1.11%。由此可知,通過分頻,線性區間變寬,非線性得到明顯改善,幾乎無非線性化現象。

其中,Vo是鑒相器在不同相位差下的輸出電壓;Vo1是相位差為0°時,經AD9901和低通濾波后得到的直流輸出電壓;Vbias是通過調節電位器W1得到的電壓;Au是放大倍數,是通過調節電位器W2得到的。

4 結論

本文針對傳統鑒相器鑒相范圍窄、輸入頻率低、線性度不高等問題,提出了一種基于FPGA動態分頻和AD9901數字鑒相的方法。本設計鑒相范圍寬,輸入頻率高,能夠動態分頻,解決了高頻非線性化的問題,為后續電路進行處理提供了方便。該鑒相器適用于高頻寬范圍相位差測量中,在工程中具有一定的參考和實用價值。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601838 -

鑒相器

+關注

關注

1文章

60瀏覽量

23251

發布評論請先 登錄

相關推薦

基于FPGA的非線性校正設計方案

基于模數轉換原理的非線性校正設計

基于FPGA的高頻時鐘的分頻和分配設計

鑒相器頻率對產生信號的調頻線性度的影響

關于基于FPGA的可消除高頻非線性的動態分頻鑒相器設計

關于基于FPGA的可消除高頻非線性的動態分頻鑒相器設計

評論