Applied Materials表示,20年來首樁晶體管接點與導線的重大金屬材料變革,能解除7nm及以下晶圓制程主要的效能瓶頸,由于鎢(W)在晶體管接點的電性表現與銅(Cu)的局部終端金屬導線制程都已經逼近物理極限,成為FinFET無法完全發揮效能的瓶頸,因此芯片設計者在7nm以下能以鈷(Co)金屬取代鎢與銅,借以增進15%的芯片效能。

采用鈷可優化先進制程金屬填充情形,延續7nm以下的制程微縮

鎢和銅是目前先進制程所采用的重要金屬材料,然而鎢和銅與絕緣層附著力差,因此都需要線性層(Liner Layer)增加金屬與絕緣層間的附著力。

此外,為了避免阻止鎢及銅原子擴散至絕緣層而影響芯片電性,必須有阻擋層存在。

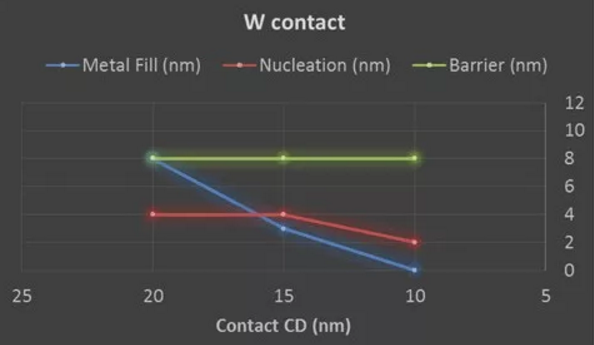

如下圖所示,隨著制程微縮至20nm以下,以鎢 contact制程為例,20nm的Contact CD中,Barrier就占了8nm,Contact中實際金屬層為12nm (金屬填充8nm+ 晶核形成 4nm),Contact直徑為10nm時,實際金屬層僅剩2nm,以此估算Contact直徑為8nm時將沒有金屬層的容納空間,此時線性層及阻擋層的厚度成了制程微縮瓶頸。

注:金屬導線及晶體管間的連接通道稱為Contact,由于Contact實際形狀是非常貼近圓柱體的圓錐體。因此Contact CD一般指的是Contact直徑

▲W Contact的金屬填充情形

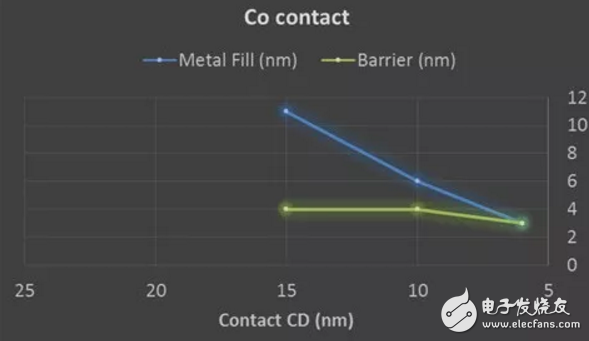

然而同樣10nm的Contact直徑若采用鈷(如下圖),其Barrier僅4nm,而實際金屬層則有6nm,相較于采用鎢更有潛力在7nm以下制程持續發展。

▲CO Contact的金屬填充情形

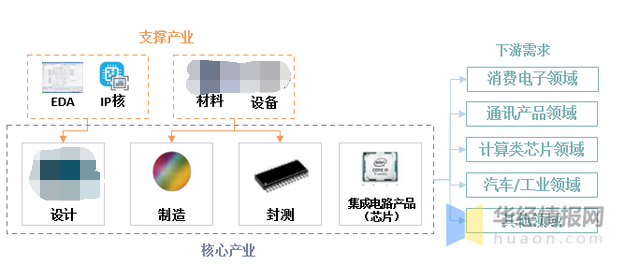

金屬材料變革將影響中國半導體設備的研發方向

目前中國半導體設備以蝕刻、薄膜及CMP的發展腳步最快,此部分將以打入主流廠商產線、取得認證并藉此建立量產數據為目標,朝向打入先進制程的前段晶體管制程之遠期目標是相當明確。

然而相較于國際主流半導體設備廠商的技術水平,中國半導體設備廠商仍是追隨者角色,因此鈷取代鎢和銅的趨勢確立,將影響中國半導體設備廠商尤其是蝕刻、薄膜及CMP的研究發展方向。

-

芯片

+關注

關注

453文章

50394瀏覽量

421788 -

半導體

+關注

關注

334文章

27006瀏覽量

216271

發布評論請先 登錄

相關推薦

中國半導體的鏡鑒之路

作為產業上游關鍵,國產半導體材料進展如何?

作為產業上游關鍵,國產半導體材料進展如何?

焊接達人必修課:探究金屬材料焊接性的六大要素

連接器的主要材料只有金屬材料嗎

焊接高手進階指南:金屬材料焊接性的影響因素全解析

用于材料領域的共聚焦顯微鏡可以看到什么?

金屬材料變革將影響中國半導體設備的研發方向

金屬材料變革將影響中國半導體設備的研發方向

評論