射頻(RF)電路板設計雖然在理論上還有很多不確定性,但RF電路板設計還是有許多可以遵循的法則。不過,在實際設計時,真正實用的技巧是當這些法則因各種限制而無法實施時,如何對它們進行折衷處理,本文將集中探討與RF電路板分區設計有關的各種問題。

01

微過孔的種類

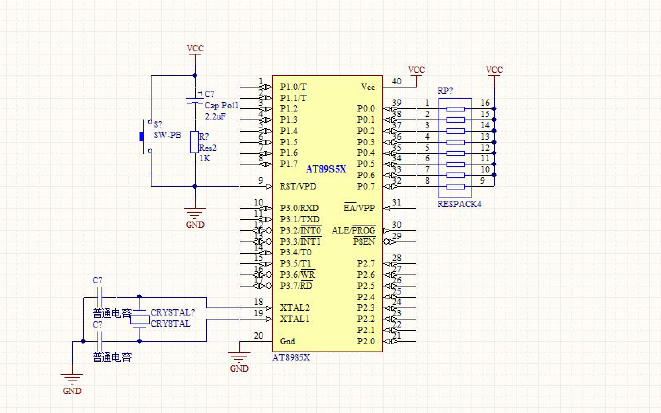

電路板上不同性質的電路必須分隔,但是又要在不產生電磁干擾的最佳情況下連接,這就需要用到微過孔(microvia)。通常微過孔直徑為0.05mm~0.20mm,這些過孔一般分為三類,即盲孔(blind via)、埋孔(bury via)和通孔(through via)。盲孔位于印刷線路板的頂層和底層表面,具有一定深度,用于表層線路和下面的內層線路的連接,孔的深度通常不超過一定的比率(孔徑)。埋孔是指位于印刷線路板內層的連接孔,它不會延伸到線路板的表面。上述兩類孔都位于線路板的內層,層壓前利用通孔成型制程完成,在過孔形成過程中可能還會重疊做好幾個內層。第三種稱為通孔,這種孔穿過整個線路板,可用于實現內部互連或作為組件的黏著定位孔。

02

采用分區技巧

在設計RF電路板時,應盡可能把高功率RF放大器(HPA)和低噪音放大器(LNA)隔離開來,簡單的說,就是讓高功率RF發射電路遠離低噪音接收電路。如果PCB板上有很多空間,那么可以很容易地做到這一點。但通常零組件很多時,PCB制造空間就會變的很小,因此這是很難達到的。可以把它們放在PCB板的兩面,或者讓它們交替工作,而不是同時工作。高功率電路有時還可包括RF緩沖器(buffer)和壓控振蕩器(VCO)。

設計分區可以分成實體分區(physical partitioning)和電氣分區(Electrical partitioning)。實體分區主要涉及零組件布局、方位和屏蔽等問題;電氣分區可以繼續分成電源分配、RF走線、敏感電路和信號、接地等分區。

03

實體分區

零組件布局是實現一個優異RF設計的關鍵,最有效的技術是首先固定位于RF路徑上的零組件,并調整其方位,使RF路徑的長度減到最小。并使RF輸入遠離RF輸出,并盡可能遠離高功率電路和低噪音電路。

最有效的電路板堆棧方法是將主接地安排在表層下的第二層,并盡可能將RF線走在表層上。將RF路徑上的過孔尺寸減到最小不僅可以減少路徑電感,而且還可以減少主接地上的虛焊點,并可減少RF能量泄漏到層疊板內其它區域的機會。

在實體空間上,像多級放大器這樣的線性電路通常足以將多個RF區之間相互隔離開來,但是雙工器、混頻器和中頻放大器總是有多個RF/IF信號相互干擾,因此必須小心地將這一影響減到最小。RF與IF走線應盡可能走十字交叉,并盡可能在它們之間隔一塊接地面積。正確的RF路徑對整塊PCB板的性能而言非常重要,這也就是為什么零組件布局通常在移動電話PCB板設計中占大部份時間的原因。

在移動電話PCB板上,通常可以將低噪音放大器電路放在PCB打樣板的某一面,而高功率放大器放在另一面,并最終藉由雙工器在同一面上將它們連接到RF天線的一端和基頻處理器的另一端。這需要一些技巧來確保RF能量不會藉由過孔,從板的一面傳遞到另一面,常用的技術是在兩面都使用盲孔。可以藉由將盲孔安排在PCB板兩面都不受RF干擾的區域,來將過孔的不利影響減到最小。

04

金屬屏蔽罩

有時,不太可能在多個電路區塊之間保留足夠的區隔,在這種情況下就必須考慮采用金屬屏蔽罩將射頻能量屏蔽在RF區域內,但金屬屏蔽罩也有副作用,例如:制造成本和裝配成本都很高。

外形不規則的金屬屏蔽罩在制造時很難保證高精密度,長方形或正方形金屬屏蔽罩又使零組件布局受到一些限制;金屬屏蔽罩不利于零組件更換和故障移位;由于金屬屏蔽罩必須焊在接地面上,而且必須與零組件保持一個適當的距離,因此需要占用寶貴的PCB板空間。

盡可能保證金屬屏蔽罩的完整非常重要,所以進入金屬屏蔽罩的數字信號線應該盡可能走內層,而且最好將信號線路層的下一層設為接地層。RF信號線可以從金屬屏蔽罩底部的小缺口和接地缺口處的布線層走線出去,不過缺口處周圍要盡可能被廣大的接地面積包圍,不同信號層上的接地可藉由多個過孔連在起。 盡管有以上的缺點,但是金屬屏蔽罩仍然非常有效,而且常常是隔離關鍵電路的唯一解決方案。

05

電源去耦電路

恰當而有效的芯片電源去耦(decouple)電路也非常重要。許多整合了線性線路的RF芯片對電源的噪音非常敏感,通常每個芯片都需要采用高達四個電容和一個隔離電感來濾除全部的電源噪音。

最小電容值通常取決于電容本身的諧振頻率和接腳電感,C4的值就是據此選擇的。C3和C2的值由于其自身接腳電感的關系而相對比較大,從而RF去耦效果要差一些,不過它們較適合于濾除較低頻率的噪音信號。RF去耦則是由電感L1完成的,它使RF信號無法從電源線耦合到芯片中。因為所有的走線都是一條潛在的既可接收也可發射RF信號的天線,所以,將射頻信號與關鍵線路、零組件隔離是必須的。

這些去耦組件的實體位置通常也很關鍵。這幾個重要組件的布局原則是:C4要盡可能靠近IC接腳并接地,C3必須最靠近C4,C2必須最靠近C3,而且IC接腳與C4的連接走線要盡可能短,這幾個組件的接地端(尤其是C4)通常應當藉由板面下第一個接地層與芯片的接地腳相連。將組件與接地層相連的過孔應該盡可能靠近PCB板上的組件焊盤,最好是使用打在焊盤上的盲孔將連接線電感減到最小,電感L1應該靠近C1。

一個集成電路或放大器常常具有一個集電極開路輸出(open collector),因此需要一個上拉電感(pullup inductor)來提供一個高阻抗RF負載和一個低阻抗直流電源,同樣的原則也適用于對這一電感的電源端進行去耦。有些芯片需要多個電源才能工作,因此可能需要兩到三套電容和電感來分別對它們進行去耦處理,如果該芯片周圍沒有足夠的空間,那么去耦效果可能不佳。尤其需要特別注意的是:電感極少平行靠在一起,因為這將形成一個空芯變壓器,并相互感應產生干擾信號,因此它們之間的距離至少要相當于其中之一的高度,或者成直角排列以使其互感減到最小。

-

緩沖器

+關注

關注

6文章

1920瀏覽量

45450 -

RF

+關注

關注

65文章

3042瀏覽量

166831 -

壓控振蕩器

+關注

關注

10文章

133瀏覽量

29279

原文標題:射頻電路板設計的幾個要點

文章出處:【微信號:murata-eetrend,微信公眾號:murata-eetrend】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RF電路板分區設計有什么問題?

探討 RF 電路板分區設計的技巧與方法

探討 RF 電路板分區設計的技巧與方法

【分享】射頻電路板設計的幾個要點

硬件電路板設計要點

印制電路板的制作教程詳細資料概述

設計射頻電路板需要注意什么問題

射頻(RF)電路板分區設計有關的各種問題資料下載

RF電路板分區設計有關的各種問題資料下載

RF電路板分區設計的5個要點詳細概述

RF電路板分區設計的5個要點詳細概述

評論