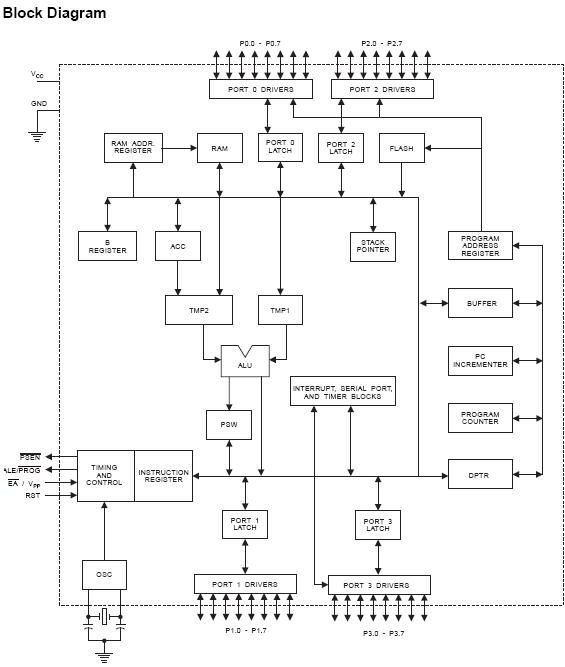

AT89C51是一種帶4K字節閃爍可編程可擦除只讀存儲器的低電壓,高性能CMOS8位微處理器,俗稱單片機。該器件采用ATMEL高密度非易失存儲器制造技術制造,與工業標準的MCS-51指令集和輸出管腳相兼容。由于將多功能8位CPU和閃爍存儲器組合在單個芯片中,ATMEL的AT89C51是一種高效微控制器,為很多嵌入式控制系統提供了一種靈活性高且價廉的方案。

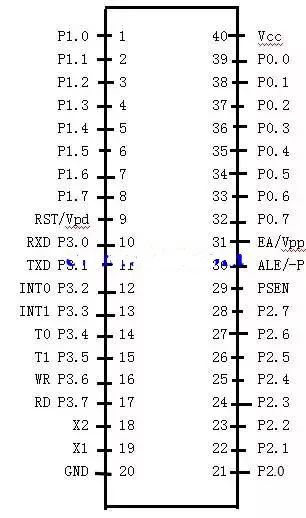

引腳說明:

VCC:供電電壓。

P0口:P0口為一個8位漏級開路雙向I/O口,每腳可吸收8TTL門電流。當P1口的管腳第一次寫1時,被定義為高阻輸入。P0能夠用于外部程序數據存儲器,它可以被定義為數據/地址的第八位。在FIASH編程時,P0 口作為原碼輸入口,當FIASH進行校驗時,P0輸出原碼,此時P0外部必須被拉高。

P1口:P1口是一個內部提供上拉電阻的8位雙向I/O口,P1口緩沖器能接收輸出4TTL門電流。P1口管腳寫入1后,被內部上拉為高,可用作輸入,P1口被外部下拉為低電平時,將輸出電流,這是由于內部上拉的緣故。在FLASH編程和校驗時,P1口作為第八位地址接收。

P2口:P2口為一個內部上拉電阻的8位雙向I/O口,P2口緩沖器可接收,輸出4個TTL門電流,當P2口被寫“1”時,其管腳被內部上拉電阻拉高,且作為輸入。并因此作為輸入時,P2口的管腳被外部拉低,將輸出電流。這是由于內部上拉的緣故。P2口當用于外部程序存儲器或16位地址外部數據存儲器進行存取時,P2口輸出地址的高八位。在給出地址“1”時,它利用內部上拉優勢,當對外部八位地址數據存儲器進行讀寫時,P2口輸出其特殊功能寄存器的內容。P2口在FLASH編程和校驗時接收高八位地址信號和控制信號。

P3口:P3口管腳是8個帶內部上拉電阻的雙向I/O口,可接收輸出4個TTL門電流。當P3口寫入“1”后,它們被內部上拉為高電平,并用作輸入。作為輸入,由于外部下拉為低電平,P3口將輸出電流(ILL)這是由于上拉的緣故。P3口也可作為AT89C51的一些特殊功能口,如下表所示:

口管腳 備選功能

P3.0 RXD(串行輸入口)P3.1 TXD(串行輸出口)P3.2 /INT0(外部中斷0)

P3.3 /INT1(外部中斷1)P3.4 T0(記時器0外部輸入)P3.5 T1(記時器1外部輸入)

P3.6 /WR(外部數據存儲器寫選通)P3.7 /RD(外部數據存儲器讀選通)

P3口同時為閃爍編程和編程校驗接收一些控制信號。89C51各部分引腳圖如下:

圖2-2 89C51引腳圖

RST:復位輸入。當振蕩器復位器件時,要保持RST腳兩個機器周期的高電平時間。

ALE/PROG:當訪問外部存儲器時,地址鎖存允許的輸出電平用于鎖存地址的地位字節。在FLASH編程期間,此引腳用于輸入編程脈沖。在平時,ALE端以不變的頻率周期輸出正脈沖信號,此頻率為振蕩器頻率的1/6。因此它可用作對外部輸出的脈沖或用于定時目的。然而要注意的是:每當用作外部數據存儲器時,將跳過一個ALE脈沖。如想禁止ALE的輸出可在SFR8EH地址上置0。此時, ALE只有在執行MOVX,MOVC指令是ALE才起作用。另外,該引腳被略微拉高。如果微處理器在外部執行狀態ALE禁止,置位無效。為使該模塊化自動打鈴系統具有更加方便和靈活性,我們對系統的硬件做了精心設計。硬件電路包括七段式數碼管驅動模塊、蜂鳴器驅動模塊、按鈕控制模塊等三大模塊。

-

單片機

+關注

關注

6032文章

44514瀏覽量

632956 -

存儲器

+關注

關注

38文章

7452瀏覽量

163598 -

引腳

+關注

關注

16文章

1181瀏覽量

50274

原文標題:3AT89C51單片機引腳說明及引腳圖

文章出處:【微信號:changxuemcu,微信公眾號:暢學單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

C51單片機AT89C51仿真圖

如何實現(電腦)PC機與單片機AT89C51的串行通信

AT89C51單片機簡介

基于AT89C51單片機的ADC0808程序

基于AT89C51單片機下的引腳說明及引腳圖

基于AT89C51單片機下的引腳說明及引腳圖

評論