握手發生在主設備和從設備之間。握手協議是主設備和從設備在握手時所遵守的共同規則。除了,B3版中的標準模式之外,B4版的Wishbone官方手冊中還新增了流水線模式。下面將依次進行介紹。

標準Wishbone協議

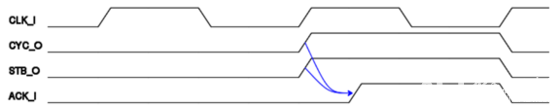

如圖7所示,當主機準備傳輸數據時,應將STB_O置位,直到從機將以下任一信號(周期結束信號)置位:ACK_I、ERR_I或者RTY_I。在每一個時鐘(CLK_I)上升沿,系統都會對周期結束信號進行采樣。當任一周期結束信號被置位時,STB_O信號就會被復位。這就讓主機和從機接口都有機會來控制數據的傳輸速率。

圖7 標準總線握手協議,異步從機

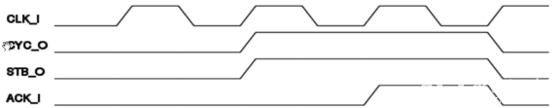

圖8 標準總線握手協議,同步從機

允許3.10:在標準模式下,如果從設備保證能夠在主設備發起操作時及時做出操作成功的響應,此時ERR_I和RTY_I信號可以不使用,ACK_O信號可以設計為STB_I和CYC_I信號的邏輯與。因此ERR_O和RTY_O信號是可選的,而ACK_O信號是必須的。在點對點連接中,甚至可以將ACK_I信號直接置高。當存在ERR_O和RTY_O信號,主設備當發現ERR_O和RTY_O信號之一有效時如何進行響應取決于主設備的設計。

注意3.25:在標準模式下,從機接口會置位一個周期結束信號來響應STB_I。然而,STB_I信號只有在CYC_I信號有效地時候才有效。

注意3.30:在總線周期期間置位ERR_I信號,會立即結束該周期,意味著從機通知主機在該周期期間發生了錯誤。當從機邏輯電路檢測到錯誤,便會置位ERR_I信號。例如,如果從機使用了奇偶校檢,當發生錯誤時,從機便會通過ERR_I做出反應。

在總線周期期間置位RTY_I信號,也會立即結束該周期,意味著從機通知主機在該周期期間發生了故障(Aborted)。該信號一般用于共享內存或者總線橋接。當本地資源處于忙狀態時,從機電路便會置位RTY_I信號。應當注意,Wishbone規范并未強制要求主機何時對RTY_I信號做出相應。

規則3.40:實際上,對于主設備,其最小配置為ACK_I、CLK_I、CYC_O、RST_I和STB_O。所有的其他信號都是可選的(optional)。

允許3.20:主機和從機接口之間可以被設計成支持ERR_I/ERR_O信號。但是Wishbone規范并未要求主機對ERR_I信號做出什么響應,用于可以根據自己的需求設計。

允許3.25:主機和從機接口之間可以被設計成支持TRY_I/TRY_O信號。但是Wishbone規范并未要求主機對TRY_I信號做出什么響應,用于可以根據自己的需求設計。

規則3.45:當從機支持ERR_O和TRY_O信號時,應保證從機同一時刻只能將三個周期結束信號的其中之一置位。

注意3.35:如果從機支持了ERR_O和RTY_O信號,而主機不支持這些信號,可能會造成系統的死鎖。

推薦3.10:通過設計INTERCON模塊可以阻止死鎖的情況發生。其中一種解決方法就是,設計一個看門狗定時器用來監控STB_O信號。當ERR_I或者RTY_I信號周期技術超出了預定義的限制時,INTERCON模塊可以被設計成將Wishbone總線連接斷開。

推薦3.15:在圖7中,從STB_O到ACK_I存在一個長組合邏輯路徑,在實際系統中很可能成為關鍵路徑。因此,在設計中應盡量保證STB_O是觸發器的直接輸出。如果從STB_O到ACK_I存在一個長組合邏輯路徑延遲不能滿足設計的時序要求,可將從設備的ACK_O經過觸發器寄存后再輸出,從而將長組合邏輯打破,但系統的吞吐量也將因此減小。

規則3.50:從機接口必須被設計成ACK_O、ERR_O和RTY_O信號的置位或復位與STB_I信號的置位或復位有關。

允許3.30:ACK_O、ERR_O和RTY_O信號的置位允許被設計成異步邏輯(例如,STB_I與ACK_O之間的組合邏輯路徑)。

注意3.40:ACK_O、ERR_O和RTY_O信號的異步置位可以保證每一個時鐘周期可以完成一次數據傳輸。進一步來說,可以簡化多主機情況下的仲裁器設計。

注意3.45:在某些場合,ACK_O、ERR_O和RTY_O信號的異步置位可能不能實現。例如,從機等待狀態早于用寄存器實現的ACK_O信號。

注意3.50:在部分高速設計場合,ACK_O、ERR_O和RTY_O信號的異步置位可能會導致不可接受的延時時間,一般是由于主機和從機之間的回路延時導致的。使用寄存器實現ACK_O、ERR_O和RTY_O信號可以顯著地減少這種回路延時。

允許3.35:在特定情況下,從機接口可能被設計成保持ACK_O信號一直處于置位狀態。例如,一個單從機,單主機,點對點的接口,從機操作根本不需要等待時間。

規則3.55:當從機接口保持ACK_I信號為置位狀態時,主機接口應當被設計為正常操作模式。

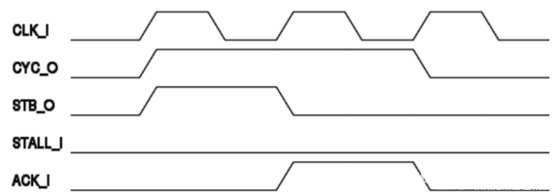

流水線Wishbone協議

在流水線模式下,握手協議主要有以下差異:

·主機在輸出下一個地址/數據 字到總線上之前,不能等待ACK_I信號;

·主機接口上的STALL_I信號用于表示從機流水線此時可以接受另一個請求。總線仲裁器應該選擇目標從機STALL_O信號,并將其告知主機。這種路徑應當被設計成非寄存式的(non-registered)。

·主機當STALL_I信號為低電平時,輸出請求。當STALL_I信號被置位時,則處于等待狀態。即,當STALL_I信號被置位,流水線不能夠產生任何請求。

·如果總線周期由N個轉換構成,則最后一個ACK_I表示轉換的終止。當接收到最后的ACK_I脈沖后,主機結束總線周期。

·只有當ACK_I信號為高電平時,讀取數據操作才是有效的。

圖9 流水線模式 單次訪問

規則3.57:在流水線模式下,當CYC_I和STB_I信號被置位后,緊接著STALL_I和WE_I信號被復位時,一個讀轉換操作開始。

規則3.58:在流水線模式下,當CYC_I、STB_I和WE_I信號被置位后,緊接著STALL_I信號被復位時,一個寫轉換操作開始。

規則3.59:在流水線模式下,完成轉換初始化后,主機必須能在任意時間接受ACK_I信號。

-

信號

+關注

關注

11文章

2780瀏覽量

76634 -

總線

+關注

關注

10文章

2868瀏覽量

87993 -

Wishbone

+關注

關注

0文章

16瀏覽量

10418

原文標題:【博文連載】Wishbone總線周期之握手協議

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

周期精確的流水線仿真模型

基于WISHBONE總線的FLASH閃存接口設計

采用單通道通訊協議設計高速異步流水線控制器STFB電路的設計

FPGA之為什么要進行流水線的設計

滾筒輸流水線故障排除方法

如何選擇合適的LED生產流水線輸送方式

嵌入式_流水線

標準Wishbone協議:流水線Wishbone協議

標準Wishbone協議:流水線Wishbone協議

評論