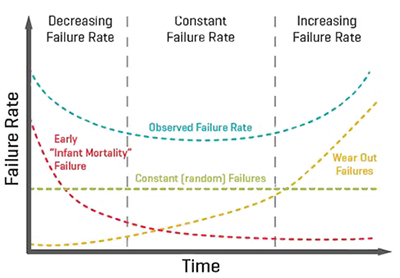

低電壓模擬電源IC、物聯網和電動汽車領域發揮著越來越重要的角色,由于工業機械和車輛的運行都需要很長的時間,這就對工業和車載中所用的IC提出了更高的可靠性要求。

提高IC的可靠性能,這是一項聽似簡單但操作起來十分棘手的工藝技術。不少半導體公司為此開發出了N通道LDMOS,它能為電機控制IC和電源管理IC提供低的RON特性和高可靠性,應用前景被廣泛看好。

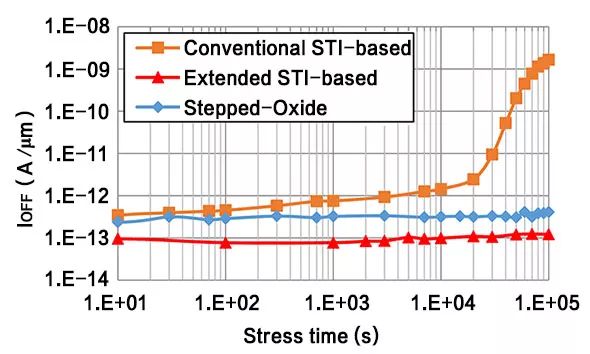

但就在這個時候,東芝的研究發現N通道LDMOS有一個負面特性,即其關斷狀態的泄漏電流(“IOFF”)因長時間使用而急劇增加。增加的IOFF有什么危害呢?它將導致電路運行故障,增加待機功耗!所以,改進N通道LDMOS的關鍵在于找到抑制IOFF的方案。

如何抑制IOFF?

在研發相關技術的過程中,東芝與其制造子公司——日本半導體擦出了強烈的火花。

東芝憑借著在晶體管設計方面的專有知識,加上日本半導體在車載模擬IC業務中所積累的工藝技術,利用TCAD仿真和實驗數據,分析了IOFF的機理,并確定了兩種可抑制IOFF增加、具有卓越容差的結構。

它們分別是具有擴展STI的結構和階梯式氧化物結構:

3個N通道LDMOS結構的截面圖

兩個新結構與傳統結構中的IOFF比較

第一種結構適合于LDMOS只占芯片總面積一小部分的模擬電路,比如電機控制IC,因為它不需要附加的工藝步驟但RON仍會增加。第二種結構更適用于LDMOS占芯片總面積較大部分的模擬電路,比如電機驅動器IC和DC-DC轉換器,因為它即便采用附加的工藝步驟仍具有較低的RON且具有成本效益。

針對以上異同,我們可以在芯片設計或應用中選擇合適的LDMOS結構。

總言之,通過TCAD仿真的階梯式氧化物結構設計優化將使得LDMOS比傳統LDMOS更有效地降低RON,從而實現更強的可靠性。LDMOS的壽命提高了5倍,大大提高了模擬電源IC的壽命。

東芝和日本半導體共同研發的這項新技術目前已被廣泛認可,并在5月16日于芝加哥舉行的2018年功率半導體器件和IC國際研討會(ISPSD 2018)上被詳細報告,它有望在明年被引入模擬電源IC中。

接下來,東芝和日本半導體在半導體工藝研發上還會擦出怎么樣的火花呢?芝子表示敲期待的!

-

東芝

+關注

關注

6文章

1393瀏覽量

121148 -

模擬電源

+關注

關注

3文章

109瀏覽量

24296

原文標題:為模擬電源IC開發的新技術,火花四射

文章出處:【微信號:toshiba_semicon,微信公眾號:東芝半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

東芝和日本半導體擦出火花,新技術為模擬電源IC提高可靠性

東芝和日本半導體擦出火花,新技術為模擬電源IC提高可靠性

評論