在高速pcb設計中,有很大一部分工作是進行噪聲預算,規劃系統各種噪聲源產生噪聲大小。這就涉及到一個非常基礎但十分重要的概念:電壓容限。

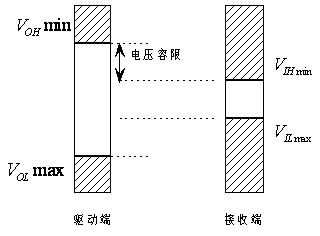

電壓容限是指驅動器的輸出與接收端輸入在最壞情況下的靈敏度之間的差值。很多器件都是輸入電壓敏感的。圖中顯示了驅動器輸出與接受器輸入電壓之間的邏輯關系。

對于驅動器端輸出高電平不低于VOHmin,輸出低電平不高于VOLmax。而對于接收端輸入來說,只要高于VIHmin,就可以保證可靠接收到邏輯1,只要低于VILmax即可保證接受到邏輯0。而如果輸入電壓位于VIHmin和VILmax之間的區域時,可能被接收電路判為1,也可能判為0,因此對于接收電路來說輸入電壓不能處于這個不定態區域。以高電平輸出和輸入關系來看,最小的輸出值和最小允許輸入值之間存在一個差值,這個值就是高電平的電壓容限。

即:高電平電壓容限=VOHmin- VIHmin。同理低電平電壓容限=VIHmin -VILmax。

電壓容限為處理電路系統中各種不理想因素提供了一個緩沖地帶,使得系統能夠在一定程度上容忍發送和接收過程中的信號畸變。電壓容限在系統噪聲預算設計中占有重要的作用,系統最終的噪聲總量不能超過電壓容限,否則,信號進入接收端的不定態區域時,系統將無法正常工作。

實際系統中總會有不理想的因素,造成信號的惡化,引入噪聲。下面幾種情況都會引入噪聲:

1、由于回路阻抗的存在,回路中必然產生壓降,導致各邏輯器件之間存在地電位差。門電路發送的信號是本地地電位上的一個固定電位,如果發送端與接收端的參考電位之間發生了偏移,那么收到的將會是另外一個電位。

2、某些邏輯系列產品的門限電平是一個溫度的函數。溫度較低的門電路到溫度較高的門電路的信號傳送可能容限減少或者負的容限值。

3、快速變化的返回信號電流,流經接地通路電感,引起邏輯器件之間的對地電壓變化。這些對地電壓差對于接收信號電位的影響就像上面所說的直流地電位差一樣。這是感性串擾的一種形式。

4、鄰近線路上的信號可能通過各自的互容或互感相互耦合,對某個指定的線路產生串擾。串擾疊加到預期的接收信號之上,可能使一個好信號偏移到鄰近開關門限。

5、振鈴、反射、長的線路使二進制信號的形狀產生扭曲。與發射端相比,接收端變化了的信號顯得更小(或更大)。容限為信號失真流出了一些容許限度。

前兩種情況在所有電子系統都會存在,無論其運行速度如何。后三種是高速系統特有的。這3個高速效應都隨被傳輸信號的大小而改變:信號返回電流越大,引起的地電位差越高。信號電壓(或電流)越大,產生的串擾越多,而且傳輸信號越大,表現出的振鈴和反射越嚴重。因此不論是低速還是高速系統,都不可避免的引入噪聲,而電壓容限給了系統調整地余地。

-

pcb

+關注

關注

4317文章

23010瀏覽量

396337 -

電壓容限

+關注

關注

1文章

4瀏覽量

6375 -

噪聲預算

+關注

關注

0文章

2瀏覽量

5926

原文標題:電壓容量設計,你知道多少!

文章出處:【微信號:PCBTech,微信公眾號:EDA設計智匯館】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電壓容限是什么?電壓容量設計需要考慮哪些因素?

電壓容限是什么?電壓容量設計需要考慮哪些因素?

評論