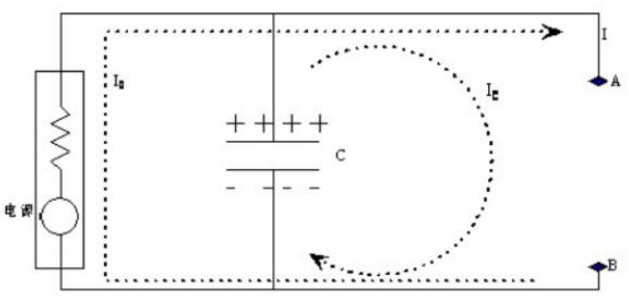

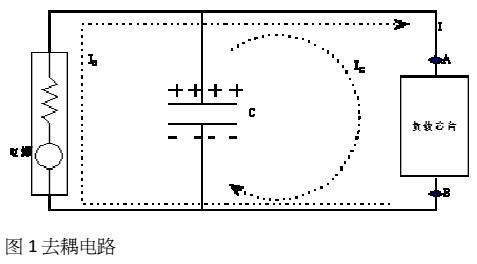

使用基于電磁場分析的設計軟件來選擇退耦電容的大小及其放置位置可將電源平面與地平面的開關噪聲減至最小。隨著信號的沿變化速度越來越快,今天的高速數字電路板設計者所遇到的問題在幾年前看來是不可想象的。對于小于1納秒的信號沿變化,PCB板上電源層與地層間的電壓在電路板的各處都不盡相同,從而影響到IC芯片的供電,導致芯片的邏輯錯誤。為了保證高速器件的正確動作,設計者應該消除這種電壓的波動,保持低阻抗的電源分配路徑。為此,你需要在電路板上增加退耦電容來將高速信號在電源層和地層上產生的噪聲降至最低。你必須知道要用多少個電容,每一個電容的容值應該是多大,并且它們放在電路板上什么位置最為合適。一方面你可能需要很多電容,而另一方面電路板上的空間是有限而寶貴的,這些細節上的考慮可能決定設計的成敗。反復試驗的設計方法既耗時又昂貴,結果往往導致過約束的設計從而增加不必要的制造成本。使用軟件工具來仿真、優化電路板設計和電路板資源的使用情況,對于要反復測試各種電路板配置方案的設計來說是一種更為實際的方法。本文以一個xDSM(密集副載波多路復用)電路板的設計為例說明此過程,該設計用于光纖/寬帶無線網絡。軟件仿真工具使用Ansoft的SIwave,SIwave基于混合全波有限元技術,可以直接從layout工具Cadence Allegro, Mentor Graphics BoardStation, Synopsys Encore和 Zuken CR-5000 Board Designer導入電路板設計。圖1是SIwave中該設計的PCB版圖。由于PCB的結構是平面的,SIwave可以有效的進行全面的分析,其分析輸出包括電路板的諧振、阻抗、選定網絡的S參數和電路的等效Spice模型。

xDSM電路板的尺寸,也就是電源層和地層的尺寸是11×7.2 英寸(28×18.3 厘米)。電源層和地層都是1.4mil厚的銅箔,中間被23.98mil厚的襯底隔開。為了理解對電路板的設計,首先考慮xDSM電路板的裸板(未安裝器件)特性。根據電路板上高速信號的上升時間,你需要了解電路板在頻域直到2GHz范圍內的特性。圖2所示為一個正弦信號激勵電路板諧振于0.54GHz時的電壓分布情況。同樣,電路板也會諧振于0.81GHz和0.97GHz以及更高的頻率。為了更好地理解,你也可以在這些頻率的諧振模式下仿真電源層與地層間電壓的分布情況。圖2所示在0.54GHz的諧振模式下,電路板的中心處電源層和地層的電壓差變化為零。對于一些更高頻率的諧振模式,情況也是如此。但并非在所有的諧振模式下都是如此,例如在1.07GHz、1.64GHz和1.96 GHz的高階諧振模式下,電路板中心處的電壓差變化是不為零的。

找到零壓差變化點有助于我們將需要在短時間內產生大量電流變化的器件放置于此。例如,如果要將一塊Xinlix的FPGA芯片放在電路板上,該芯片會在0.2納秒內產生2A的輸入電流變化。如此短時間內的大電流變化將帶來電路板的電源完整性問題,會使電路板產生各種模式的諧振,導致電源層和地層電壓的不均勻。然而,電路板中心處在某些諧振模式下具有零壓差變化的特性,因此將FPGA芯片放置于此可以避免電路板產生這些低頻的諧振模式。FPGA芯片不能激發這些低頻諧振模式,是由于從電路板的中心處將無法耦合至這些諧振模式。圖3中的紫色曲線顯示的是當位于電路板中心處的芯片從電源平面吸入電流時引起的諧振。事實上,峰值出現在高階的諧振頻率1.07GHz、1.64GHz和1.96GHz上,而不是低階的諧振頻率0.54GHz、0.81GHz和0.97GHz上,這正如我們所料。

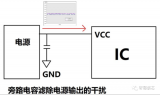

盡管器件的布局與放置的位置有助于減小電源完整性的問題,但它們并不能解決所有的問題。首先,你不能將所有的關鍵器件放在電路板的中心。通常情況下,器件放置的靈活性是有限的。其次,在任何給定的位置總有一些諧振模式會被激發。例如,圖3中綠色曲線表示當你將芯片放置在沿某一坐標軸偏移中心位置時,0.54GHz的諧振模式將被激發。成功的設計電路板的PDS(電源分配系統)的關鍵在于在合適的位置增加退耦電容,以保證電源的完整性和在足夠寬的頻率范圍內保證地彈噪聲足夠小。

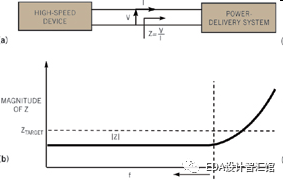

退耦電容設想FPGA在0.2納秒的上升沿 吸入2A的電流,此時電源電壓會暫時降低(壓降),而地平面電壓會暫時被拉高(地彈)。其變化幅度取決于電路板的阻抗和芯片偏置管腳處的用于提供電流的退耦電容(圖4a)。由于電流的瞬變值為2A,電壓的瞬變值由V=Z×I決定,Z是從芯片端視出的阻抗,因此,為了避免電壓的尖峰波動,在從直流到信號帶寬的頻率范圍內,Z值必須低于某一門限值。(圖4b)

在該設計中,為了保持電源完整性,電源—地的電壓波動必須保持在標準值3.3V的5%以內。因此噪聲不能大于0.05×3.3V=165 mV。可以據此按照歐姆定律計算出PDS的最大阻抗165mV/2A=82.5mΩ,圖4中虛線部分即為PDS阻抗應該滿足的目標區域。對于最低頻率,通常是1kHz或者更低的頻率——電源滿足阻抗特性的要求,電源和地層的結構通常不會破壞阻抗特性,因為它們呈現低電阻與電感特性。而當頻率高于1kHz時,電流通路的互感大。

-

電磁場

+關注

關注

0文章

790瀏覽量

47236 -

退耦電容

+關注

關注

1文章

29瀏覽量

9564 -

開關噪聲

+關注

關注

0文章

18瀏覽量

11249

原文標題:高速PCB仿真——電源完整性與地彈噪聲

文章出處:【微信號:PCBTech,微信公眾號:EDA設計智匯館】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

退耦電容的放置位置

運放為什么要使用退耦電容呢?

什么是退耦電容

如何正確降低風扇噪音

MCU退耦電容引發的EMC血案

如何正確的增加退耦電容降低生產的噪音?

如何正確的增加退耦電容降低生產的噪音?

評論