CMOS與非門電路多余輸入端的處理

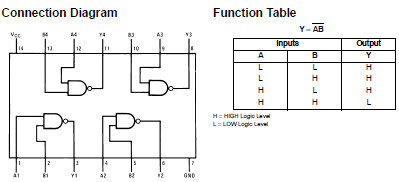

與非門電路的邏輯功能是輸入信號(hào)只要有低電平.輸出信號(hào)就是高電平.

只有當(dāng)輸入信號(hào)全部為高電平時(shí).輸出信號(hào)才是低電平。所以某輸入端輸入電平為高電平時(shí).對(duì)電路的邏輯功能并無(wú)影響.即其它使用的輸入端與輸出

端之間仍具有與或者與非邏輯功能。這樣對(duì)于CMOS與門、與非門電路的多余輸入端就應(yīng)采用高電平,即可通過限流電阻接電源。

TTL與非門電路多余輸入端的處理

對(duì)于TTL 與非門,只要電路輸入端有低電平輸入,輸出就為高電平.只有輸入端全部為高電平時(shí).輸出才為低電平。根據(jù)其邏輯功能.當(dāng)某輸入端外接高電平時(shí)耐其邏輯功能無(wú)影響.根據(jù)這一特點(diǎn)應(yīng)采用以下四種方法

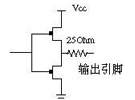

1、將多余輸入端接高電平.即通過限流電阻與電源相連接。

2、根據(jù)TTL門電路的輸入特性可知,當(dāng)外接電阻為大電阻時(shí).其輸入電壓為高電平。這樣可以把多余的輸入端懸空.此時(shí).輸入端相當(dāng)于外接高電平。

3、通過大電阻到地,這也相當(dāng)于輸入端外接高電平。

4、當(dāng)TTL門電路的工作速度不高.信號(hào)源驅(qū)動(dòng)能力較強(qiáng).多余輸入端也可與使用的輸入端并聯(lián)使用。

TTL與非門多余的輸入端比較

CMOS集成電路是一種新型的MOS集成電路,具有很多獨(dú)特的優(yōu)點(diǎn),如靜態(tài)功耗極低,允許電源電壓波動(dòng)范圍大,抗干擾能力強(qiáng),工作速度高,扇出系數(shù)大,輸出邏輯振幅大。正因?yàn)槿绱耍茫停希蛹呻娐吩诟鞣N科技領(lǐng)域中得到非常迅速而廣泛地應(yīng)用。類似于TTL門電路,CMOS集成門電路同樣會(huì)存在多余輸入端,對(duì)于多余輸入端的處理方式不同,仍然會(huì)對(duì)電路性能帶來不同的影響,而且有的影響是比較大的。

1.與門和與非門

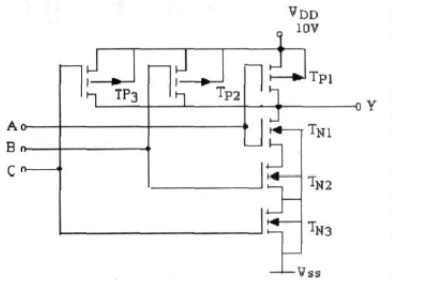

對(duì)于CMOS與非門的多余輸入端,主要的處理方法仍然是將之與有用輸入端并聯(lián)或者將之設(shè)為高電平。CMOS輸入端并聯(lián)使用時(shí),會(huì)影響CMOS電路的輸出電阻。以與非門為例(圖2),假設(shè)單個(gè)MOS管的輸出電阻為RON,輸入端并聯(lián)后,在高電平輸出時(shí),輸出電阻最小可達(dá)RON/3,輸出電阻變小。輸入端并聯(lián)還會(huì)對(duì)CMOS門電路轉(zhuǎn)折電壓(即閥值電壓)產(chǎn)生影響,使得轉(zhuǎn)折電壓變大,降低了高電平噪聲容限。因此輸入端并聯(lián)后,一方面由于輸出電阻變小而增強(qiáng)了與非門帶拉電流負(fù)載的能力,另一方面使得電壓傳輸特性右移。并聯(lián)的輸入端越多,高電平輸出時(shí)輸出電阻越小,電壓傳輸特性右移越大,高電平噪聲容限也就越小。輸入端并聯(lián),還會(huì)降低開關(guān)速度,增大前級(jí)門的功耗。并聯(lián)的輸入端越多,這些影響越嚴(yán)重。由于MOS管的柵極與其它電極之間有絕緣層相隔,因此CMOS門電路的輸入電阻很高,靜態(tài)時(shí)幾乎沒有電流,所以即使通過高達(dá)幾百kΩ的電阻接地也不能獲得高電平。綜上所述,對(duì)于CMOS與非門和與門電路的多余輸入端的處理,通過限流電阻接VDD較好。

CMOS三輸入端與非門

2.或門和或非門

對(duì)于或非門的多余輸入端,我們可以將之與有用輸入端并聯(lián)或者通過限流電阻接地。與非門多余輸入端并聯(lián)使用時(shí)遇到的問題在或非門中同樣存在。因?yàn)榛蚍情T電路中與VDD連接的三個(gè)TP管串聯(lián),與地連接的三個(gè)TN管并聯(lián),所以多余輸入端并聯(lián)后對(duì)或非門的影響剛好和與非門的相反,或非門輸入端并聯(lián)使用,使傳輸特性左移,轉(zhuǎn)折電壓減小,低電平噪聲容限減小,帶灌電流負(fù)載的能力有所增強(qiáng)[5]。

由上面分析可知,不管是TTL還是CMOS門電路的多余輸入端,我們一般都不宜采取輸入端并聯(lián)的方法來處理多余輸入端。不過在要求不高的情況下,這種處理方法卻又是最方便的。所以大家可以根據(jù)實(shí)際情況,采取最有效的處理方法。

-

TTL

+關(guān)注

關(guān)注

7文章

502瀏覽量

70126 -

輸入端

+關(guān)注

關(guān)注

0文章

34瀏覽量

11628

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

CMOS和TTL集成門電路多余輸入端的處理方法

CMOS和TTL集成門電路多余輸入端如何處理?

CMOS和TTL集成門電路多余輸入端如何處理?

TTL與非門電路及TTL與非門的技術(shù)參數(shù)

TTL與非門多余的輸入端處理方法及其比較

TTL與非門多余的輸入端處理方法及其比較

評(píng)論