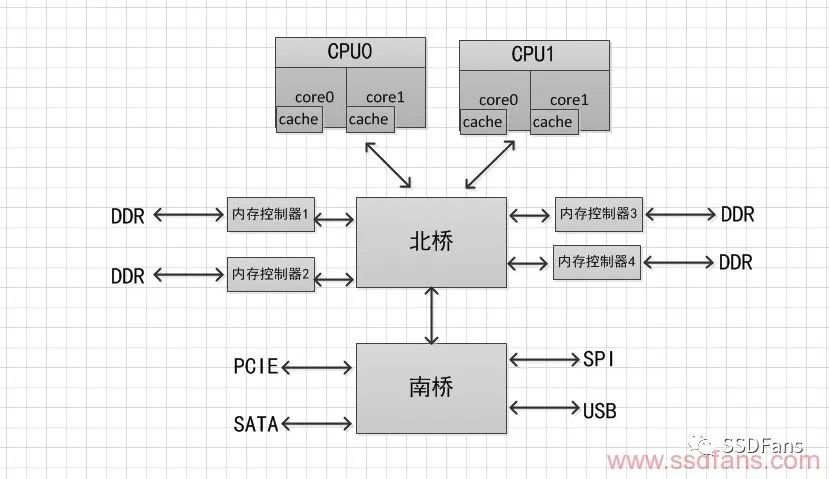

通常一個處理器包含多個核心(Core),集成 Cache 子系統(tǒng),內存子系統(tǒng)通過內部或外部總線與其通信。在經典CPU中一般有兩個常用的組件:北橋(North Bridge)和南橋(South Bridge)。它們是處理器和內存以及其他外設溝通的渠道。圖1給出了處理器、內存、南北橋以及其他總線之間的關系。

圖1

從圖一可以看到:

1)處理器訪問內存需要通過北橋。

2)處理器訪問所有的外設都需要通過北橋。

3)掛在南橋的所有設備訪問內存也需要通過北橋。

那么CPU訪問南橋上的外部設備和北橋上的DDR內存的訪問速率受CPU的主頻、Local Bus帶寬、南橋外設總線的速率、CPU取指令機制等多方面所影響。

處理器主頻和集成度在過去二十年里一直按照摩爾定律在發(fā)展,從單核到多核以及超線程。處理器的性能提高不少,同時處理器的功耗也正比于主頻的三次方在增加。因為使用的晶體管柵極材料存在漏電現象,高頻率下電子遷移顯著,勢必為導致產熱量增加,散熱帶了重大問題。CPU歡快的朝著頻率越來越高的方向發(fā)展,受到物理極限的挑戰(zhàn),又轉為核數越來越多的方向發(fā)展。由于所有CPU Core都是通過共享一個北橋來讀取內存,隨著核數如何的發(fā)展,北橋在響應時間上的性能瓶頸越來越明顯當北橋出現擁塞時,所有的設備和處理器都要癱瘓。這種系統(tǒng)設計的另外一個瓶頸體現在對內存的訪問上。不管是處理器或者顯卡,還是南橋的硬盤、網卡或者光驅,都需要頻繁訪問內存,當這些設備都爭相訪問內存時,增大了對北橋帶寬的競爭,而且北橋到內存之間也只有一條總線。

為了改善對內存的訪問瓶頸,出現了另外一種系統(tǒng)設計,內存控制器并沒有被集成在北橋中,而是被單獨隔離出來以協(xié)調北橋與某個相應的內存之間的交互。系統(tǒng)結構如圖2所示。

圖 2 所示的這種架構增加了內存的訪問帶寬,緩解了不同設備對同一內存訪問的擁塞問題,但是卻沒有改進單一北橋芯片的瓶頸的問題。

圖2

為了解決北橋北橋在響應時間上的性能瓶頸,把內存控制器(原本北橋中讀取內存的部分)也做個拆分,平分到了每個CPU上。于是NUMA(Non-Uniform Memory Access)就出現了。內存控制器集成到CPU內部,Intel第二代酷睿I系列以及將主板北橋合并到CPU內部,所以Intel第二代酷睿I系列沒有北橋,只有南橋。AMD沒有吞并北橋。順便補充一下Intel 單個socket只支持單個node,AMD 單個socket配對多個node。(Node,socket,core,thread)是NUMA中的概念,linux下查看cpu參數通過如下命令:

a)lscpu

圖3

圖3可以看出CPU是小端模式,每個CPU有一個core,每一個core有一個thread。三級cache大小,Flags查看支持的大頁內存,比如pse 代表支持2MB的內存頁,pdpe1gb代表支持1G內存頁。

b)cat /proc/cpuinfo

圖4

從圖4可以到Core ID、超線程數、Core的16進制編碼(在DPDK應用中會用到這些參數)。

NUMA設計框架如圖5所示。紅色綠色箭頭代表訪問處理器本地內存(Local memory),紅色箭頭訪問遠程內存(remote memory),即其他處理器的本地內存,需要通過額外的總線!

NUMA中,雖然內存直接attach在CPU上,但是由于內存被平均分配在了各個die上。只有當CPU訪問自身直接attach內存對應的物理地址時,才會有較短的響應時間(后稱Local Access)。而如果需要訪問其他CPU attach的內存的數據時,就需要通過inter-connect通道訪問,響應時間就相比之前變慢了(后稱Remote Access)。所以NUMA(Non-Uniform Memory Access)就此得名。

圖5

從前面分析發(fā)現,確實提高了CPU訪問內存和外設的速率,奈何CPU處理速率遠遠超過了內存的吞吐速率,這里就帶來了CPU不必要的開銷。一般來說,當CPU從DDR中取指令時,大概要花費幾百個時鐘周期,在這幾百個時鐘周期內,處理器除了等待什么也不能做。在這種環(huán)境下,才提出了Cache的概念,其目的就是為了匹配處理器和內存之間存在的巨大的速度鴻溝。

Cache 由三級組成,之所以對Cach 進行分級,也是從成本和生產工藝的角度考慮的。一級(L1)最快,但是容量最小,一級cache分為指令cache和數據cache,圖3中可以查看;三級(LLC, Last Level Cache)最慢,但是容量最大。當CPU需要訪問某個地址時候,首先在cache中目錄表中查詢是否有該內容,有就直接取指令或者數據,沒有就從DDR中取取指令或者數據。在cache有對應的數據簡稱指令命中,反之指令沒有命中。L3 cache命中,大約需要40個時鐘周期,L3 cache沒命中,一個內存讀需要140個時鐘周期。

Cache 的預取指令分為時間局部性和空間局部性。時間局部性是指程序即將用到的指令/數據可能就是目前正在使用的指令數據。因此,當前用到的指令/數據在使用完畢之后以暫時存放在Cache中,可以在將來的時候再被處理器用到。空間局部性是指程序即將用到的指/數據可能與目前正在使用的指令/數據在空間上相鄰或者相近。因此,在處理器處理當前指令/數據時,可以從內存中把相鄰區(qū)域的指令/數據讀取到Cache中,當處理器需要處理相鄰內存區(qū)域的指令/數據時,可以直接從Cache中讀取,節(jié)省訪問內存的時間。這里可以創(chuàng)建一個二維數組,然后順序橫向a[i][j]和豎向a[j][i]賦值計算時間做對比,由于a[j][i]地址是跳躍性的賦值,cache不能命中,所以消耗的時間遠遠大于連續(xù)地址的賦值。

提高CPU性能還可以采用多核并行計算,一個時鐘周期讀取N條指令。在軟件上也可以做適當的系統(tǒng)優(yōu)化和算法優(yōu)化,比如配置CPU 親和性,CPU 親和性(Core affinity)就是一個特定的任務要在某個定的 CPU 上盡量長時間地運行而不被遷移到其他處理器上的傾向性。

-

處理器

+關注

關注

68文章

19165瀏覽量

229129 -

cpu

+關注

關注

68文章

10825瀏覽量

211150

原文標題:CPU性能發(fā)展遇到的瓶頸

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

如何改進CPU性能發(fā)展瓶頸問題?

如何改進CPU性能發(fā)展瓶頸問題?

評論