芯片是什么?芯片的具體設計流程又是什么?本文探討的就是芯片在字面以外的意義,以及芯片是怎么被設計成的。

芯片

芯片,又稱微電路(microcircuit)、微芯片(microchip)、集成電路(英語:integrated circuit, IC)。是指內含集成電路的硅片,體積很小,常常是計算機或其他電子設備的一部分。

芯片,英文為Chip;芯片組為Chipset。芯片一般是指集成電路的載體,也是集成電路經過設計、制造、封裝、測試后的結果,通常是一個可以立即使用的獨立的整體。“芯片”和“集成電路”這兩個詞經常混著使用,比如在大家平常討論話題中,集成電路設計和芯片設計說的是一個意思,芯片行業、集成電路行業、IC行業往往也是一個意思。實際上,這兩個詞有聯系,也有區別。集成電路實體往往要以芯片的形式存在,因為狹義的集成電路,是強調電路本身,比如簡單到只有五個元件連接在一起形成的相移振蕩器,當它還在圖紙上呈現的時候,我們也可以叫它集成電路,當我們要拿這個小集成電路來應用的時候,那它必須以獨立的一塊實物,或者嵌入到更大的集成電路中,依托芯片來發揮他的作用;集成電路更著重電路的設計和布局布線,芯片更強調電路的集成、生產和封裝。而廣義的集成電路,當涉及到行業(區別于其他行業)時,也可以包含芯片相關的各種含義。

芯片也有它獨特的地方,廣義上,只要是使用微細加工手段制造出來的半導體片子,都可以叫做芯片,里面并不一定有電路。比如半導體光源芯片;比如機械芯片,如MEMS陀螺儀;或者生物芯片如DNA芯片。在通訊與信息技術中,當把范圍局限到硅集成電路時,芯片和集成電路的交集就是在“硅晶片上的電路”上。芯片組,則是一系列相互關聯的芯片組合,它們相互依賴,組合在一起能發揮更大的作用,比如計算機里面的處理器和南北橋芯片組,手機里面的射頻、基帶和電源管理芯片組。

芯片設計流程

芯片設計分為前端設計和后端設計,前端設計(也稱邏輯設計)和后端設計(也稱物理設計)并沒有統一嚴格的界限,涉及到與工藝有關的設計就是后端設計。

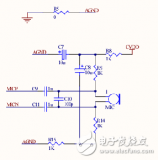

芯片的設計原理圖

芯片設計之前端設計

1. 規格制定

芯片規格,也就像功能列表一樣,是客戶向芯片設計公司(稱為Fabless,無晶圓設計公司)提出的設計要求,包括芯片需要達到的具體功能和性能方面的要求。

2. 詳細設計

Fabless根據客戶提出的規格要求,拿出設計解決方案和具體實現架構,劃分模塊功能。

3. HDL編碼

使用硬件描述語言(VHDL,Verilog HDL,業界公司一般都是使用后者)將模塊功能以代碼來描述實現,也就是將實際的硬件電路功能通過HDL語言描述出來,形成RTL(寄存器傳輸級)代碼。

4. 仿真驗證

仿真驗證就是檢驗編碼設計的正確性,檢驗的標準就是第一步制定的規格。看設計是否精確地滿足了規格中的所有要求。規格是設計正確與否的黃金標準,一切違反,不符合規格要求的,就需要重新修改設計和編碼。 設計和仿真驗證是反復迭代的過程,直到驗證結果顯示完全符合規格標準。

仿真驗證工具Synopsys的VCS,還有Cadence的NC-Verilog。

5. 邏輯綜合――Design Compiler

仿真驗證通過,進行邏輯綜合。邏輯綜合的結果就是把設計實現的HDL代碼翻譯成門級網表netlist。綜合需要設定約束條件,就是你希望綜合出來的電路在面積,時序等目標參數上達到的標準。邏輯綜合需要基于特定的綜合庫,不同的庫中,門電路基本標準單元(standard cell)的面積,時序參數是不一樣的。所以,選用的綜合庫不一樣,綜合出來的電路在時序,面積上是有差異的。一般來說,綜合完成后需要再次做仿真驗證(這個也稱為后仿真,之前的稱為前仿真)。

邏輯綜合工具Synopsys的Design Compiler。

6. STA

Static Timing Analysis(STA),靜態時序分析,這也屬于驗證范疇,它主要是在時序上對電路進行驗證,檢查電路是否存在建立時間(setup time)和保持時間(hold time)的違例(violation)。這個是數字電路基礎知識,一個寄存器出現這兩個時序違例時,是沒有辦法正確采樣數據和輸出數據的,所以以寄存器為基礎的數字芯片功能肯定會出現問題。

STA工具有Synopsys的Prime Time。

7. 形式驗證

這也是驗證范疇,它是從功能上(STA是時序上)對綜合后的網表進行驗證。常用的就是等價性檢查方法,以功能驗證后的HDL設計為參考,對比綜合后的網表功能,他們是否在功能上存在等價性。這樣做是為了保證在邏輯綜合過程中沒有改變原先HDL描述的電路功能。

形式驗證工具有Synopsys的Formality。

前端設計的流程暫時寫到這里。從設計程度上來講,前端設計的結果就是得到了芯片的門級網表電路。

芯片設計之后端設計

1. DFT

Design For Test,可測性設計。芯片內部往往都自帶測試電路,DFT的目的就是在設計的時候就考慮將來的測試。DFT的常見方法就是,在設計中插入掃描鏈,將非掃描單元(如寄存器)變為掃描單元。關于DFT,有些書上有詳細介紹,對照圖片就好理解一點。

DFT工具Synopsys的DFT Compiler

2. 布局規劃(FloorPlan)

布局規劃就是放置芯片的宏單元模塊,在總體上確定各種功能電路的擺放位置,如IP模塊,RAM,I/O引腳等等。布局規劃能直接影響芯片最終的面積。

工具為Synopsys的Astro

3. CTS

Clock Tree Synthesis,時鐘樹綜合,簡單點說就是時鐘的布線。由于時鐘信號在數字芯片的全局指揮作用,它的分布應該是對稱式的連到各個寄存器單元,從而使時鐘從同一個時鐘源到達各個寄存器時,時鐘延遲差異最小。這也是為什么時鐘信號需要單獨布線的原因。

CTS工具,Synopsys的Physical Compiler

4. 布線(Place & Route)

這里的布線就是普通信號布線了,包括各種標準單元(基本邏輯門電路)之間的走線。比如我們平常聽到的0.13um工藝,或者說90nm工藝,實際上就是這里金屬布線可以達到的最小寬度,從微觀上看就是MOS管的溝道長度。

工具Synopsys的Astro

5. 寄生參數提取

由于導線本身存在的電阻,相鄰導線之間的互感,耦合電容在芯片內部會產生信號噪聲,串擾和反射。這些效應會產生信號完整性問題,導致信號電壓波動和變化,如果嚴重就會導致信號失真錯誤。提取寄生參數進行再次的分析驗證,分析信號完整性問題是非常重要的。

工具Synopsys的Star-RCXT

6. 版圖物理驗證

對完成布線的物理版圖進行功能和時序上的驗證,驗證項目很多,如LVS(Layout Vs Schematic)驗證,簡單說,就是版圖與邏輯綜合后的門級電路圖的對比驗證;DRC(Design Rule Checking):設計規則檢查,檢查連線間距,連線寬度等是否滿足工藝要求, ERC(Electrical Rule Checking):電氣規則檢查,檢查短路和開路等電氣 規則違例;等等。

工具為Synopsys的Hercules

實際的后端流程還包括電路功耗分析,以及隨著制造工藝不斷進步產生的DFM(可制造性設計)問題,在此不說了。

物理版圖驗證完成也就是整個芯片設計階段完成,下面的就是芯片制造了。物理版圖以GDS II的文件格式交給芯片代工廠(稱為Foundry)在晶圓硅片上做出實際的電路,再進行封裝和測試,就得到了我們實際看見的芯片。

芯片設計之工藝文件

在芯片的設計重要設計環節,像綜合與時序分析,版圖繪制等都需要用到工藝庫文件,而大家往往又對工藝文件缺乏認識,所以導致想自學一些芯片設計的東西就顯得很困難。例如,沒有工藝版圖庫文件,學習版圖設計就是紙上談兵。這篇文章主要介紹一下工藝庫相關的知識。

工藝文件由芯片制造廠提供,所以概括性的了解國內和國際上有哪些芯片制造廠是很有必要的。國際上,主要有臺積電,英特爾,三星等主要半導體制造商。國內,主要有中芯國際,華潤上華,深圳方正等公司。這些公司都提供相關的工藝庫文件,但前提是要與這些公司進行合作才能獲取,這些工藝文件都屬于機密性文件。

完整工藝庫文件主要組成為:

1,模擬仿真工藝庫,主要以支持spectre和hspice這兩個軟件為主,后綴名為scs——spectre使用,lib——hspice使用。

2,模擬版圖庫文件,主要是給cadence版圖繪制軟件用,后綴名為tf,drf。

3,數字綜合庫,主要包含時序庫,基礎網表組件等相關綜合及時序分析所需要用到的庫文件。主要是用于DC軟件綜合,PT軟件時序分析用。

4,數字版圖庫,主要是給cadence encounter軟件用于自動布局布線,當然自動布局布線工具也會用到時序庫,綜合約束文件等。

5,版圖驗證庫,主要有DRC,LVS檢查。有的是專門支持calibre,有的專門支持dracula,diva等版圖檢查工具用。每一種庫文件都有相應的pdf說明文檔。

反向設計會用到1,2,5等工藝庫文件,3和4是不會用到了。正向設計(從代碼開始設計的正向設計)則所有的文件都需要用到。由于工藝文件在芯片設計中占有極重要的位置,在每一個關鍵設計環節都要用到,再加上它的機密屬性,所以網絡上很難找到完整的工藝文件對于個人學習用,EETOP上有一份cadence公開的用于個人學習的工藝庫文件可以方便大家學習,但似乎也是不完整的。

芯片設計之綜合

什么是綜合?綜合就是將RTL級verilog代碼用Design Compiler 工具 轉換/映射成用基礎門級單元表示的電路的過程。基礎門級單元也就是平時我們學的與非門,或非門,寄存器之類的,只不過,這些門級單元已經做成了標準的單元庫,我們可以直接使用軟件來調用,而不需要自己調用門級單元來搭建電路。簡單的來說,Design Compiler軟件就是做翻譯的工作——將代碼翻譯成實際電路,但又不僅僅是翻譯這么簡單,它涉及到電路的優化與時序約束,使之符合我們做制定的性能要求。 前文提到該軟件是約束驅動型軟件,那么約束從何而來?答案是,設計規格書。每一個芯片設計項目都會有一個項目規格說明書,這是在芯片設計之初,整體規劃(見前文)的步驟中要制定好的。具體詳細的約束要求需要在綜合過程中仔細的斟酌決定。 綜合的一般流程:

1,預綜合過程;

2,施加設計約束過程;

3,設計綜合過程;

4,后綜合過程。

PS,使用Design Compiler軟件一個必備的條件是要學會使用DC TCL腳本。

預綜合過程。這部分主要是準備好綜合過程所使用的庫文件(包括工藝庫、鏈接庫、符號庫、綜合庫)、設計輸入文件,設置好環境參數。

施加設計約束過程。這部分主要是用DC TCL腳本編寫約束文件。具體的約束項目可以分為三大類:

a,面積約束,定義時鐘,約束輸入/輸出路徑;

b(環境屬性),約束輸入驅動,約束輸出負載,設置工作條件(最好、典型、最差情況),設置連線負載模型;

c(高級時鐘約束),對時鐘的抖動、偏移、時鐘源延遲,同步多時鐘,異步時鐘,多周期路徑,這幾類進行細致的約束。

約束的內容具體就是這么多。一個詳細的TCL腳本約束文件基本包含上述所有的約束。后面有一個約束范文。

設計綜合過程。主要是介紹電路模塊設計規劃(以利于更好的進行約束),Design Compiler綜合優化的過程(三大優化階段,結構級,邏輯級,門級),時序分析的具體過程等綜合過程中的一些詳細信息。

后綜合過程。綜合完畢該怎么看結果,時序違反該如何解決?這就是后綜合過程所要解決的問題。在綜合之后,通過分析綜合報告,可以得知此次的電路綜合結果如何,根據不符合的要求,進行重新約束,甚至重新設計電路。在這個階段特別值得一提的是綜合預估,因為在寫綜合約束腳本的時候,需要確定約束條件,規格書一般不能夠涉及到如此細節的部分,所以需要根據實際電路進行綜合預估,這個步驟是在代碼編寫完之后,與驗證同時進行的,目的在于大致估計電路是否符合要求,此時的預綜合過程與正式的綜合過成是一樣的,但,要求會寬松許多,時序違反的要求大概為10%-15%,也就是說電路即使有10%-15%的電路不滿足時序也沒有關系。

綜合約束過程是一個反復迭代的過程,需要多次設計預估,這樣才能不斷修正時序違反。范文:

# Set the current_design #

read_verilog {counter_pad.v counter.v} //讀取設計文件

current_design Cnt10_PAD

link

set_operating_conditions -max slow -max_library slow -min fast -min_library fast //設置工作條件

set_wire_load_mode enclosed //設置連線負載模型

set_wire_load_model -name tsmc18_wl10 -library slow //設置連線負載模型

set_local_link_library {slow.db fast.db}//設置鏈接庫

set_max_area 0 //設置面積

set_max_fanout 5 [get_ports reset_n]//設置最大扇出

set_max_fanout 4 [get_ports clk] //設置最大扇出

set_max_fanout 4 [get_ports in_ena]//設置最大扇出

set_max_transition 0.3 [get_ports reset_n]//設置信號翻轉時間

set_max_transition 0.3 [get_ports clk]//設置信號翻轉時間

set_max_transition 0.5 [get_ports in_ena]//設置信號翻轉時間

create_clock [get_ports clk]-period 10 -waveform. {0 5}//創建時鐘

set_clock_latency 1[get_clocks clk]//設置時鐘源延時

set_clock_latency -source 1[get_clocks clk]

set_clock_uncertainty -setup 0.5[get_clocks clk]//設置時鐘不確定度

set_clock_uncertainty -hold 0.4[get_clocks clk]

set_dont_touch_network [get_clocks clk]//設置偽路徑,不要約束

set_clock_transition -fall 0.3 [get_clocks clk]////設置下降沿信號翻轉時間

set_clock_transition -rise 0.3 [get_clocks clk]///設置上升沿沿信號翻轉時間

set_input_delay -clock clk-max 3[get_ports in_ena]//設置輸入延時

set_output_delay -clock clk -max 4 [get_ports cnt]//設置輸出延時

set_output_delay -clock clk -min 0.5 [get_ports cnt]

set_output_delay -clock clk-max 4[get_ports carry_ena]

set_output_delay -clock clk-min 0.5[get_ports carry_ena]

compile//編譯

report_timing -delay max > ./reports/pad_setup_rt.rpt//報告最大時序延時

report_timing -delay min > ./reports/pad_hold_rt.rpt//報告最小時序延時

report_constraint -verbose > ./reports/pad_rc.rpt

report_qor > ./reports/pad_rq.rpt

remove_unconnected_ports -blast_buses [get_cells -hierarchical *]

set bus_inference_style. {%s[%d]}

set bus_naming_style. {%s[%d]}

set hdlout_internal_busses true

change_names -hierarchy -rule verilog

define_name_rules name_rule -allowed {a-z A-Z 0-9 _} -max_length 255 -type cell

define_name_rules name_rule -allowed {a-z A-Z 0-9 _[]} -max_length 255 -type net

define_name_rules name_rule -map {{"\\*cell\\*" "cell"}}

define_name_rules name_rule -case_insensitive

change_names -hierarchy -rules name_rule

write -format verilog -hier -o ./outputs/pad_counter.sv

write -format ddc -hier -o ./outputs/pad_counter.ddc

write_sdc ./outputs/pad_counter.sdc

write_sdf ./outputs/pad_counter.sdf

總結

芯片設計的過程中是十分復雜,本文也是簡單的將芯片設計流程梳理一遍,復雜的就不再贅述了。

-

芯片

+關注

關注

454文章

50430瀏覽量

421890 -

原理圖

+關注

關注

1294文章

6312瀏覽量

232982

發布評論請先 登錄

相關推薦

芯片設計流程 芯片的設計原理圖

芯片設計流程 芯片的設計原理圖

芯片設計流程 芯片的設計原理圖

評論