隨著技術的發展,數字信號的時鐘頻率越來越高,電路系統對于信號的建立、保持時間、時鐘抖動等要素提出越來越高的要求。EMI,即電磁干擾,是指電路系統通過傳導或者輻射的方式,對于周邊電路系統產生的影響。EMI會引起電路性能的降低,嚴重的話,可能導致整個系統失效。在實際操作中,相關機構頒布電磁兼容的規范,確保上市的電子產品滿足規范要求。

時鐘信號常常是電路系統中頻率最高和邊沿最陡的信號,多數EMI問題的產生和時鐘信號有關。

降低EMI的方法有許多種,包括屏蔽、濾波、隔離、鐵氧體磁環、信號邊沿控制以及在PCB中增加電源和GND層等等。在應用中可以靈活使用以上方法,其中屏蔽是相對簡單的機械學方法,成本較高,不適用于手持和便攜式設備;濾波和信號邊沿控制對于低頻信號有效,不適合當前廣泛應用的高速信號。另外,使用EMI/RFI濾波器這些被動元器件,會增加成本;通過LAYOUT技巧降低EMI顯然比較費時,而且因設計的不同,手段也不盡相同。

展頻時鐘(Spread Spectrum Clocking)是另一種有效降低EMI的方法,本文將簡要描述展頻時鐘發生器(Spread Spectrum Clock Generator,SSCG)是如何降低EMI的。

概述

時鐘展頻通過頻率調制的手段將集中在窄頻帶范圍內的能量分散到設定的寬頻帶范圍,通過降低時鐘在基頻和奇次諧波頻率的幅度(能量),達到降低系統電磁輻射峰值的目的。

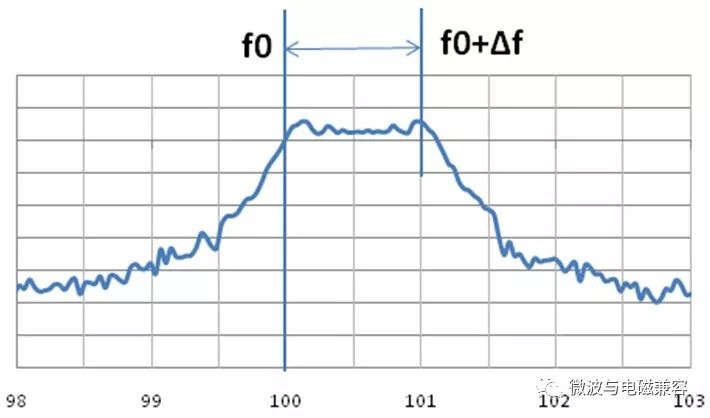

一般數字時鐘有很高的Q值,即所有能量都集中在很窄的頻率范圍內,表現為相對較高的能量峰值。在頻譜圖上容易看到在中間頻率上有很高的峰值,在奇次諧波位置有較低的峰值;SSCG通過增加時鐘帶寬的方法降低峰值能量,減小時鐘的Q值。圖1示意SSCG的工作原理。

圖1.SSCG降低EMI示意圖

時鐘展頻通過特定方式調制原始時鐘信號。Linear和Hershey Kiss(不是好時之吻巧克力哦)是常用的調制方式。

應用特點

SSCG是一種Active且低成本的解決EMI問題的方案,可以在保證時鐘信號完整性的基礎上應對更廣頻率范圍內EMI問題。相比傳統上使用Ferrite Beads和RF Chokes抑制EMI,SSCG通過時鐘內部集成電路調制頻率的手段來達到抑制EMI峰值的目的。SSCG不僅調制時鐘源,其它的同步于時鐘源的數據、地址和控制信號,在時鐘展頻的同時也一并得以調制,整體的EMI峰值都會因此減小,所以說,時鐘展頻是系統級的解決方案。這是SSCG相比其它抑制EMI措施的最大優勢。

SSCG功能可以由用戶選擇不同配置,ON或者OFF,以及不同的調制范圍等。

被動的EMI抑制器件通常也會集成ESD保護功能,是不耗電的。SSCG由于使用到展頻等集成電路功能,會消耗能量。

調制參數

時鐘展頻有三個主要的控制參數:調制速度(Modulation Rate)、調制深度(Modulation Depth)和調制方式(Modulation Profile)

1. 調制速度

調制速度(MR)是指輸出時鐘頻率 fo在設定的調制頻率范圍內的變化速度。調制速度應遠小于源時鐘的頻率 fc 以免引起時序問題(建立/保持時間等),同時應當高于人耳可識別的聲音的頻率范圍(20Hz~20KHz)以免產生噪音。在實際應用中,調制速度一般選擇30KHz~120KHz。

2. 調制深度

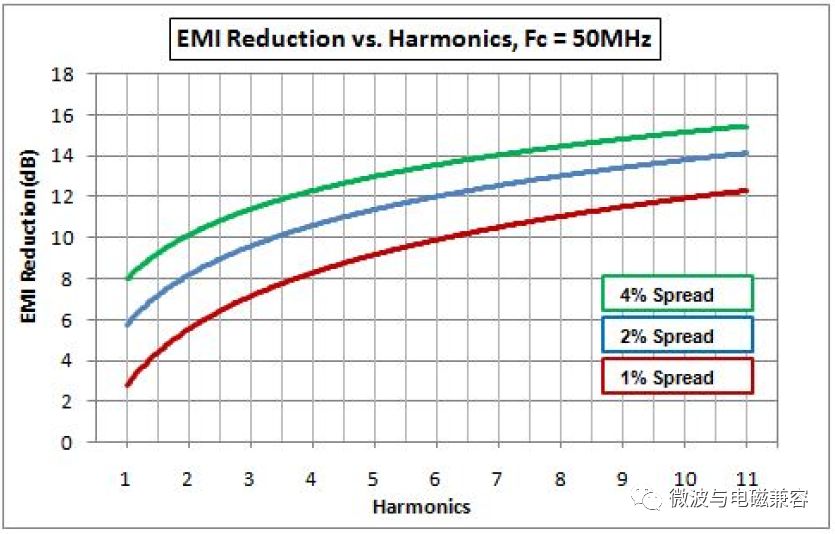

調制深度是指展頻后輸出時鐘頻率 fo以調制速度MR偏移源時鐘頻率 fc的大小。調制深度以偏移(Δf)源時鐘頻率的百分比(%)來表示。調制深度決定降低EMI峰值的大小。通常調制深度越大,EMI峰值越低。在應用時,需要合理預計系統可接受的頻率調制范圍。圖2表示在不同調制深度下,EMI峰值的對比。

圖2.調制深度對降低EMI程度的影響

在許多系統中,基頻的奇次諧波才是產生EMI問題的根源,SSCG不僅衰減基頻的EMI輻射,同時也抑制奇次諧波上的能量輻射,而且相比于基頻,SSCG對于奇次諧波的衰減作用更為顯著。這是因為奇次諧波的(展頻后)頻帶范圍相比基頻的頻帶更寬(整數倍)。如圖3表征這種影響。

圖3.EMI衰減 VS 奇次諧波

3. 調制方式

調制方式(Modulation Profile)決定EMI峰值的表現形式。Linear和Hershey Kiss是SSCG常用的兩種調制方式。

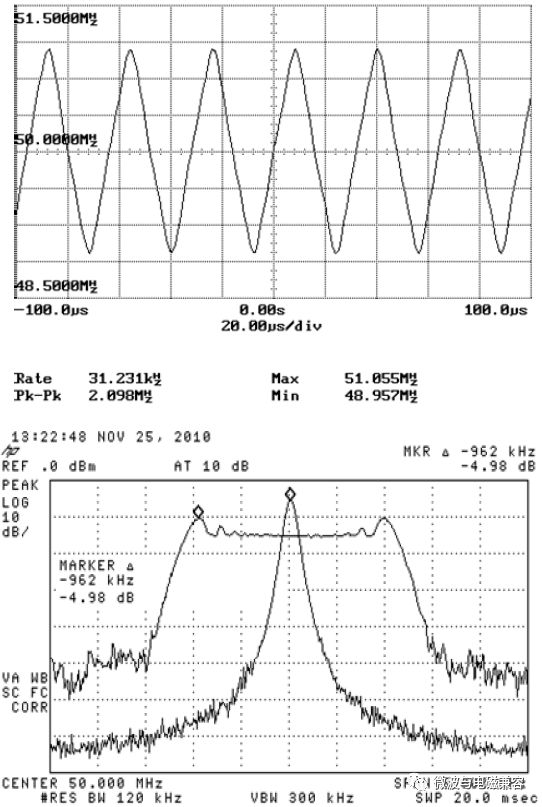

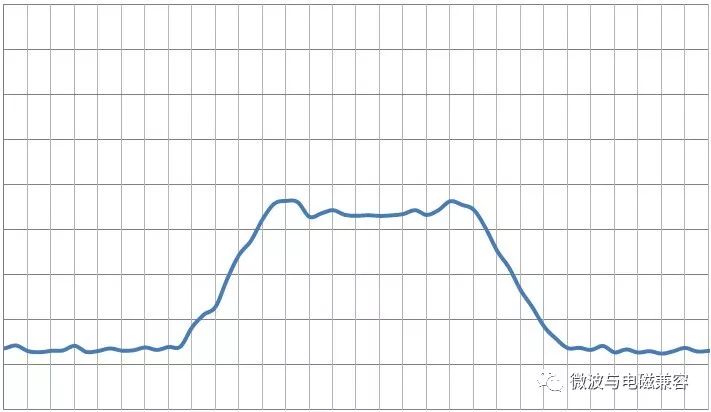

線性調制相對簡單,顧名思義,線性調制后輸出的時鐘頻率是線性變化的。這種調制方法的缺點,如圖4示,輸出頻譜旁瓣比中間頻率幅度高1-2dB,如前文討論,在任何頻率EMI的失效也就意味著整個EMI測試的失敗。旁瓣的輻射峰值可能超出SPEC范圍,設計者需要考慮到這點的影響。

圖4.線性調制方式 & 輸出頻譜

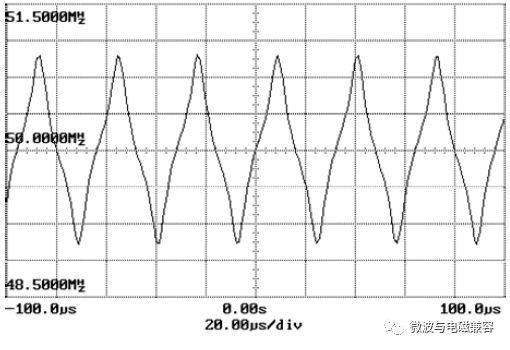

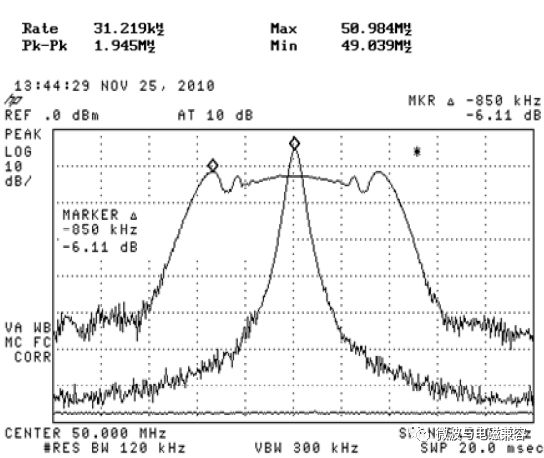

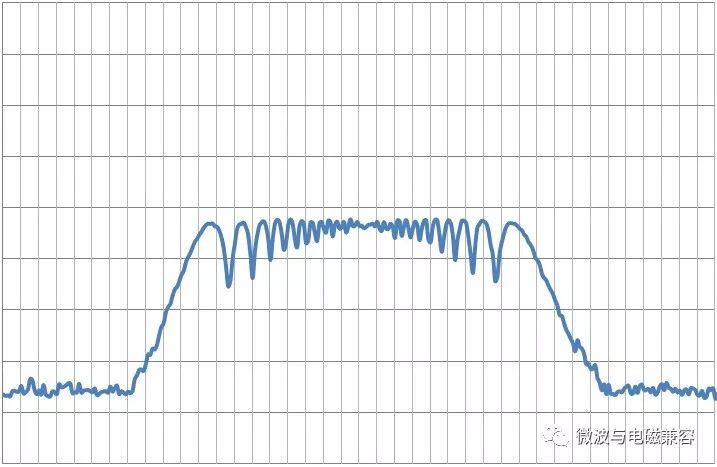

通過Hershey Kiss調制可以得到接近平整的頻譜圖,如圖5所示,Hershey Kiss調制的特點是在調制范圍的兩端,頻率變化速度更快,在調制范圍的中間值,頻率變化較慢。頻率在兩端變化的速度快,這樣信號在頻率兩端的能量得到更大的衰減,分散到中間位置。整體的表現就是整個頻譜的能量近似平坦。圖5中采用Hershey Kiss調制方式,EMI峰值更近一步衰減了1.13dB。

圖5.Hershey Kiss調制方式 & 輸出頻譜

圖6和圖7是兩種調制方式的頻譜圖。

圖6.線性調制

圖7.Hershey Kiss調制

展頻模式

按展頻時鐘相對源時鐘偏移的不同,展頻分為三類:

1. 中間展頻

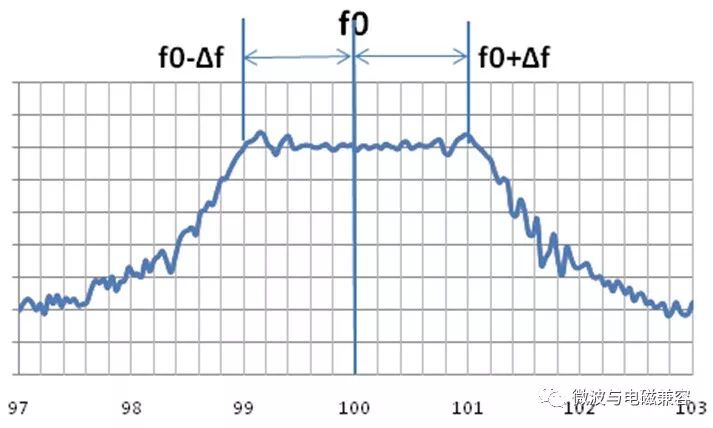

中間展頻(Centre Spread)是指展頻時鐘的平均頻率和源時鐘頻率相同的展頻方式。在未調制輸出時鐘頻率等于輸入時鐘頻率的系統中,展頻后輸出時鐘頻率 fo 按調頻方式(Linear或Hershey Kiss)決定的波形以MR速度,在(fc-Δf)到(fc+Δf)范圍內變化,即:

fo=fc ±Δf

例如,100MHz時鐘以±1%調制深度中間展頻后,輸出時鐘的變化范圍為99MHz~101MHz。

圖8和圖9表示這種展頻模式的特點,其中圖8表示輸出時鐘頻率 fo 隨時間變化的情況,圖9表示幅度(能量)在頻率范圍內分布的情況。

圖8.中間展頻(MDA)

圖9.中間展頻(Spectrum Analyzer Plot)

2. 向下展頻

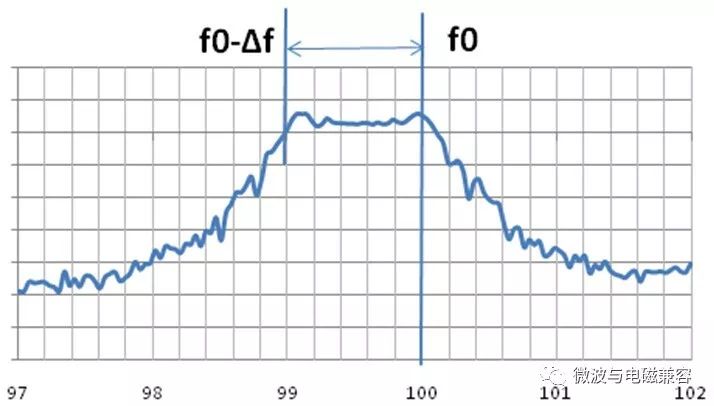

向下展頻(Down Spread)是指展頻時鐘的最高頻率等于源時鐘頻率的展頻方式。在未調制時鐘輸出頻率等于輸入時鐘頻率的系統中,展頻后輸出時鐘頻率 fo 按調頻方式(Linear或Hershey Kiss)決定的波形以MR速度,在(fc-Δf)到 fc 范圍內變化,即:

fo=fc -Δf

例如,100MHz時鐘以-1%調制深度向下展頻后,輸出時鐘的變化范圍為99MHz~100MHz。

圖10和圖11表示這種展頻模式的特點,其中圖10表示輸出時鐘頻率 fo 隨時間變化的情況,圖11表示幅度(能量)在頻率范圍內分布的情況。

圖10.向下展頻(MDA)

圖11.向下展頻(Spectrum Analyzer Plot)

3. 向上展頻

向上展頻(Up Spread)是指展頻時鐘的最低頻率等于源時鐘頻率的展頻方式。在未調制時鐘輸出頻率等于輸入時鐘頻率的系統中,展頻后輸出時鐘頻率 fo 按調頻方式(Linear或Hershey Kiss)決定的波形以MR速度,在 fc 到(fc+Δf)范圍內變化,即:

fo=fc +Δf

例如,100MHz時鐘以+1%調制深度向上展頻后,輸出時鐘的變化范圍為100MHz~101MHz。

圖12和圖13表示這種展頻模式的特點,其中圖12表示輸出時鐘頻率(fo)隨時間變化的情況,圖13表示幅度(能量)在頻率范圍內分布的情況。

圖12.向上展頻(MDA)

圖13.向上展頻(Spectrum Analyzer Plot)

注意事項

1. 時鐘抖動

時鐘展頻的一大弊端是不能用于對時鐘精度敏感的應用,如以太網和CAN總線。在選擇時鐘展頻和調制深度時,設計人員需要特別注意展頻引入額外的Jitter,并可能由此引起的建立/保持時間問題、高誤碼率和PLL失鎖問題。Jitter分為不同類別,對系統性能有不同程度的影響。

周期抖動 Period Jitter /PJ

周期抖動是指輸出時鐘相對于理想時鐘的最大偏移值。周期抖動一般是測量一段時間內(通常10,000個周期)所有的時鐘,取其中時鐘邊沿偏離的最大值(earliest and latest edge)。

周期抖動影響同步時鐘系統的時序裕量,輸出時鐘相對理想位置的偏移會對建立/保持時間造成影響。例如,100MHz時鐘在以1%調制深度向上展頻后,頻率的變化范圍是100MHz~101MHz,即時鐘周期的變化范圍是9.9ns~10ns。這樣的話,理想的展頻時鐘就有0.1ns(100ps)的周期抖動。增加調制深度(1%)或時鐘頻率(100MHz)其中任何一項,周期抖動都會線性增加,從而導致時序問題。另外,以上討論的周期抖動僅僅是由時鐘展頻引入的,還不包括設備(時鐘發生器)本身固有的Jitter,實際上展頻時鐘的Jitter應該包括這兩部分。時鐘固有Jitter可以在關閉展頻后測量出來。

長時抖動 Long-Term Jitter /LTJ

長時抖動類似于周期抖動,是指在長時間內(many cycles)輸出時鐘相對理想時鐘的最大偏移值。時鐘展頻在這方面表現更為明顯。經過長時間的變化,其時鐘信號邊緣與理想位置偏移更大。關于長時抖動比較顯著的例子是顯卡驅動顯示器,經過一段時間后,過多的長時抖動會引起像素值偏離設定值。

周期間抖動Cycle-to-Cycle Jitter /CTCJ

周期間抖動是指一個時鐘周期相對它之前時鐘周期的偏移量。在對輸入信號進行等間隔取樣的通信系統或ADC電路中,周期間抖動會造成非常不利的影響。采樣時鐘的周期間抖動會導致取樣點不準確,因而引起輸出數據錯誤。

時鐘展頻只引入非常小的周期間抖動。例如30KHz~120KHz調制速度的時鐘展頻,源時鐘的頻率至少是MR的1000倍,也就是說至少經過1000個時鐘周期,才完成一個調制周期,輸出時鐘fc相鄰周期間的差別非常小。當然,設備(時鐘發生器)本身也存在固有的周期間抖動。展頻大約只引入低于0.05%的周期間抖動進入到系統。因此展頻非常適用于需要低周期間抖動、低誤碼率和低EMI的系統。

2. 帶PLL的展頻

當展頻的時鐘輸出到下游的PLL時,注意PLL表現為低通濾波器,即允許輸入的低頻部分通過,同時衰減其中的高頻部分。展頻時鐘輸入PLL時,PLL可能出現無法鎖住頻率的問題。務必確保PLL必須能檢測展頻時鐘的頻率變化并允許展頻時鐘通過。以上取決于PLL的帶寬,如果帶寬太低,PLL可能無法可靠地偵測輸入時鐘,造成偵測偏差,給系統引入更大的Jitter。

-

emi

+關注

關注

53文章

3583瀏覽量

127377 -

時鐘頻率

+關注

關注

0文章

49瀏覽量

20325 -

數字信號

+關注

關注

2文章

958瀏覽量

47519

原文標題:20180805--用于降低EMI的時鐘展頻技術

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CDCE(L)949:支持SSC以降低EMI的靈活低功耗LVCMOS時鐘發生器數據表

展頻時鐘發生器如何降低EMI?有哪些注意事項?

展頻時鐘發生器如何降低EMI?有哪些注意事項?

評論