自動增益控制電路在通信系統領域有著非常廣泛的應用,主要用于各種接收芯片的中頻級和射頻級,實現壓縮動態范圍,抑制干擾脈沖和抗快衰落等作用。然而傳統的基于脈沖寬度調制波形輸出的AGC電路在環路穩定性上較差,收斂速度慢,外圍所需的元器件也較多,因而體積較大,這些極大地制約了AGC電路的性能。因此嘗試采用基于脈沖密度調制技術的AGC電路,以克服基于PWM技術的AGC電路的種種性能瓶頸。

1 、AGC電路概述

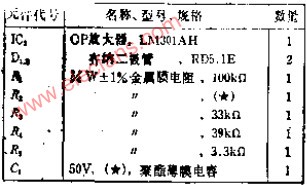

在各種通信系統中,受發射功率大小,收發距離遠近,信號在傳輸媒介中會出現明顯的衰落等因素的影響,作用在接收機輸入端的信號強度有很大的變化和起伏。然而信道解調部分只能處理幅度變化不大的信號,信號過強、過弱或忽大忽小,都會使解調失敗。所以必須要有一個AGc電路,使接收機的輸入端能處理幅度變化很大的信號,而解調部分能收到一個平穩適中的信號,以進行信道解調。AGC電路可以使振幅變化范圍非常大的輸入信號,輸出時振幅變化范圍非常小,從而保證輸入到ADC的信號位于ADC最佳的工作范圍,AGC電路的功能框圖如圖1所示。

圖1中的A/D轉換器將輸入進來的模擬信號采樣量化為數字量后,經過信號平均電平檢測器算出平均電平,該平均電平與預先設定的參考電平值V,相比較,得到平均電平誤差,將該誤差送入IIR濾波器進行平滑累加后得到與所期望的AGC增益相對應的數字量(AGC控制字),最后通過D/A轉換器送入可變增益放大器(VGA)。

在上述這些模塊中,D/A模塊有多種方案可選。由于該模塊涉及到制造工藝和系統的外圍電路,而且D/A轉換器必須占用一定空間及消耗一定量的功率,因此D/A轉換器方案的選取,將對AGC甚至整個系統的性能和成本產生很大的影響。

D/A轉換器一般有下面三種方案可選:

(1)直接使用專用的D/A轉換芯片。這種方案轉換速度快,但成本太高,一般不予采用。

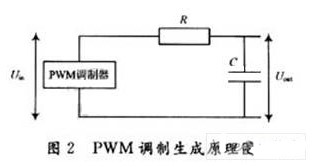

(2)脈沖寬度調制器(PWM)+RC濾波器的方案。該方案成本低廉,但是D/A轉換速度慢,AGC電路達到收斂的時間長,嚴重時會產生振蕩。該方案在對AGC環路穩定性和收斂速度要求不高的通信系統中經常被使用。

(3)脈沖密度調制(PDM)+RC濾波器的方案。該方案可以克服PWM波的諸多缺點,但成本較高,適用于對控制要求較高的系統。

2 、PDM與PWM的原理及比較

2.1 PWM理論及其特點

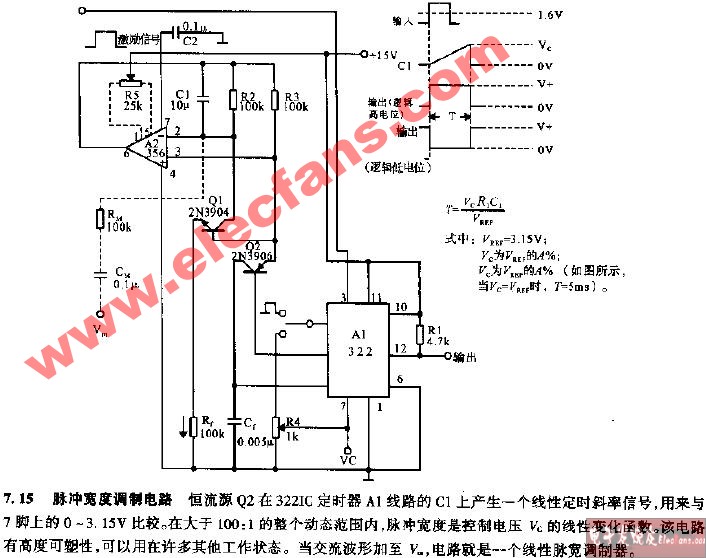

PWM是一種通過改變高低電平的比值來得到不同輸出電壓的調制方式。該調制輸出周期為T,占空比為N/M(N,M必須是整數)的方波。

如圖2所示,電容C上的電壓就是PWM的輸出電壓Uout,在RC值足夠大時,Uout=Uin·(N/M)。PWM的精度與M有著很大的關系。當M=2時,只有0,1/2和2/2三種電壓輸出;而到M=256時,就有0,1/256,2/256,3/256,…,256/256一共257種電壓輸出。M的大小取決于VGA的精度。一般來說,VGA能達到10位以上的精度,就是說M的取值要在1 024以上。隨著M的增大,RC的值也將相應增加,否則Uout就會呈現出明顯的鋸齒狀波形,使增益波動,惡化解調性能。但是如果讓RC增大,在增加元器件成本的同時,還會使Uout對IIR濾波器產生的數字量變化響應變慢,延長AGC收斂時間,甚至造成AGC的振蕩,這在AGC電路的設計中是嚴格禁止的。

2.2 PDM原理

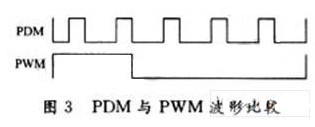

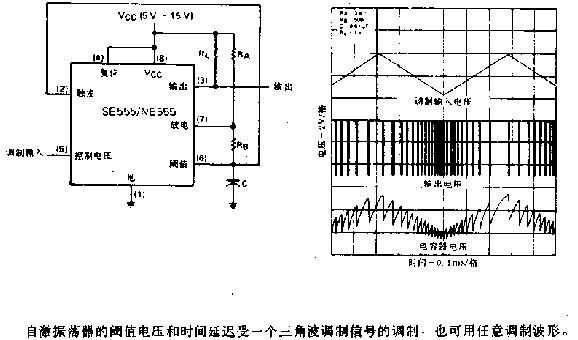

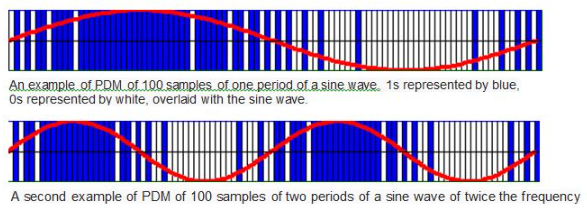

PWM的周期T是固定的,改變的是高低電平的占空比;而PDM的脈沖寬度(高電平寬度)是固定的,改變的是脈沖的密集程度,脈沖密集,Uout就越高;脈沖稀疏,則Uout就越低。圖3給出電壓為5/16時的PDM與PWM波形。

可見,PDM相當于在時域上被打散的PWM。由于PDM的高低電平分布較為均勻,因此在R,C值較小的系統里,也可以濾除高頻交流分量,從而克服PWM的缺點。

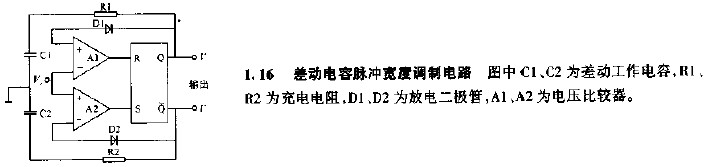

2.3 PDM的實現

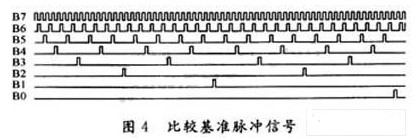

假設PDM的脈沖周期為△T,將時鐘信號送入N位計數器,實現0,1,…,2N-1的計數。在計數的單個脈沖周期△T里,將計數結果各個位上的邏輯值經過一系列邏輯操作,實現N位比較基準脈沖信號,分別為B0,B1,B2,…,B(N-1)。在每一個△T里,都只有一個位上有邏輯“1”,其他位上均為邏輯“0”。同時將輸出的N位數據與該比較基準脈沖信號B0,B1,B2,…,B(N-1)進行逐位與操作,再將各個位上的結果相或,便得到△T內的調制結果。

對于N位的信號,周期為T=2N×△T。對于8位數字信號,PDM調制結果為:

PDMout=B7&D7+B6&D6+B5&D5+B4&D4+B3&D3+B2&D2+B1&D1+B0&D0

其中,B0~B7為比較基準脈沖信號的低位到高位,而D0~D7為數字信號的低位到高位。

如圖4所示,就是8位的PDM比較基準脈沖信號。其中,B7~B0的波形分別對應10000000B,01000000B,00100000B,…,00000001B的PDM調制方波。

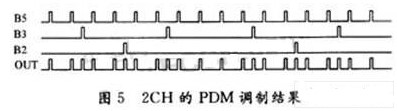

例如,對十六進制數2CH進行PDM調制。2CH對應的二進制數為“00101100”。其中,B5,B3,B2為“1”,其他各位均為“0”,經過逐位邏輯操作得:

PDMout=B7&0+B6&0+B5&1+B4&0+B3&1+B2&1+B1&0+B0&0=B5+B3+B2

經過一個周期的調制,使得到圖5所示的PDM調制信號。這樣8位的數字信號就轉化為1位的脈沖信號。

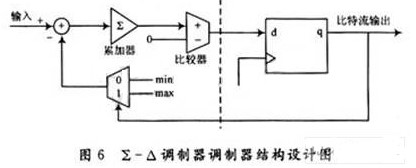

在實際工程應用中,通常在系統中使用一個∑-△調制器來產生PDM波形。∑-△調制器的結構如圖6所示。

寄存器輸出的比特流中高電平的密度代表了輸入信號的幅度。如果圖6中虛線左側部分是模擬電路,輸入的是模擬信號,那么單位時間內輸出比特流中1的個數就反映了輸入模擬信號的幅度,實現A/D轉換功能。如果虛線左側部分是數字電路,輸人的是若干比特寬的數字量,那么對輸出的比特流進行低通濾波后,就得到了相應的電壓,實現的是D/A轉換功能。本AGC電路中使用的是∑-△調制器的D/A功能,并且輸入范圍為0~1 023,可實現足夠精確的D/A轉換。

3 、PDM與PWM的仿真比較

3.1 PDM與PWM收斂時間仿真比較

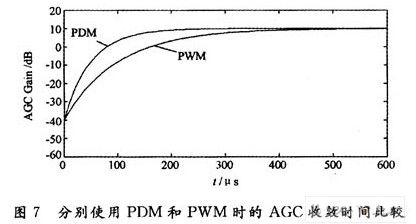

圖7是用Matlab對PDM和PWM進行的仿真對比。其中,電路參數:VGA增益為15 dB/V,R=100 Ω,C=0.1μF,AGC工作時鐘為10 MHz。

從圖7中可以看出,在相同的R,C條件下,使用PDM調制的AGC電路,在收斂時間上小于使用PWM調制的AGC電路。

3.2 PDM與PWM環路穩定性仿真比較

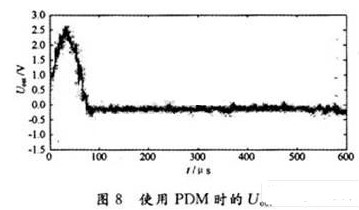

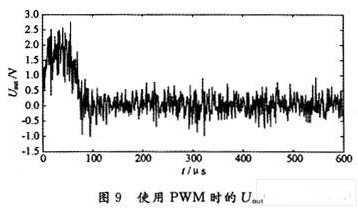

從圖8和圖9中可以看出,在相同的R,C條件下,使用PDM調制的AGC電路,Uout的抖動小于使用PWM調制的AGC電路,環路穩定性明顯較好。

4、結 語

本文通過PDM和傳統的PWM兩種調制方式的比較,最終得出使用PDM調制方式來充當AGC電路的D/A轉換器,從而控制前端VGA的增益的方案。該方案相對于PWM方案具有更短的AGC收斂時間和更穩定的環路特性。通過Matlab仿真驗證,表明了該方案的可行性。

-

放大器

+關注

關注

143文章

13554瀏覽量

213145 -

PWM

+關注

關注

114文章

5153瀏覽量

213456 -

通信系統

+關注

關注

6文章

1176瀏覽量

53290

發布評論請先 登錄

相關推薦

寬帶大動態AGC電路設計

基于脈沖密度調制技術的AGC性能的電路設計

基于脈沖密度調制技術的AGC性能的電路設計

評論