隨著無線通信頻帶資源的日益緊張,無線通信主要包括微波通信和衛星通信。微波是一種無線電波,它傳送的距離一般只有幾十千米。但微波的頻帶很寬,通信容量很大。微波通信每隔幾十千米要建一個微波中繼站。衛星通信是利用通信衛星作為中繼站在地面上兩個或多個地球站之間或移動體之間建立微波通信聯系。四相相移鍵控信號簡稱"QPSK".它分為絕對相移和相對相移兩種。由于絕對相移方式存在相位模糊問題,所以在實際中主要采用相對移相方式QDPSK.它具有一系列獨特的優點,目前已經廣泛應用于無線通信中,成為現代通信中一種十分重要的調制解調方式。在數字信號的調制方式中QPSK四相移鍵控是目前最常用的一種衛星數字信號調制方式,它具有較高的頻譜利用率、較強的抗干擾性、在電路上實現也較為簡單。

基帶信號是原始的電信號,一般是指基本的信號波形,在數字通信中則指相應的電脈沖。在無線遙測遙控系統和無線電技術中調制就是用基帶信號控制高頻載波的參數(振幅、頻率和相位),使這些參數隨基帶信號變化。用來控制高頻載波參數的基帶信號稱為調制信號。未調制的高頻電振蕩稱為載波(可以是正弦波,也可以是非正弦波,如方波、脈沖序列等)。

1 QDPSK調制解調的原理

在實際的調諧解調電路中,采用的是非相干載波解調,本振信號與發射端的載波信號存在頻率偏差和相位抖動,因而解調出來的模擬I、Q基帶信號是帶有載波誤差的信號。這樣的模擬基帶信號即使采用定時準確的時鐘進行取樣判決,得到的數字信號也不是原來發射端的調制信號,誤差的積累將導致抽樣判決后的誤碼率增大,因此數字QPSK解調電路要對載波誤差進行補償,減少非相干載波解調帶來的影響。此外,ADC的取樣時鐘也不是從信號中提取的,當取樣時鐘與輸入的數據不同步時,取樣將不在最佳取樣時刻進行所得到的取樣值的統計信噪比就不是最高,誤碼率就高,因此,在電路中還需要恢復出一個與輸入符號率同步的時鐘,來校正固定取樣帶來的樣點誤差,并且準確的位定時信息可為數字解調后的信道糾錯解碼提供正確的時鐘。校正辦法是由定時恢復和載波恢復模塊通過某種算法產生定時和載波誤差,插值或抽取器在定時和載波誤差信號的控制下,對A/D轉換后的取樣值進行抽取或插值濾波,得到信號在最佳取樣點的值,不同芯片采用的算法不盡相同,例如可以采用據輔助法(DA)載波相位和定時相位聯合估計的最大似然算法。

2PSK信號與2ASK信號的時域表達式在形式上是完全相同的,所不同的只是兩者基帶信號s(t)的構成,一個由雙極性NRZ碼組成,另一個由單極性NRZ碼組成。因此,求2PSK信號的功率譜密度時,也可采用與求2ASK信號功率譜密度相同的方法。

在2PSK(二進制絕對移相鍵控)信號相干解調過程中會產生180°相位模糊,同樣,對QPSK信號相干解調也會產生相位模糊問題,并且是0°、90°、180°和270°等4個相位模糊。因此,在實際中更實用的是四相相對移相調制,即QDPSK方式。

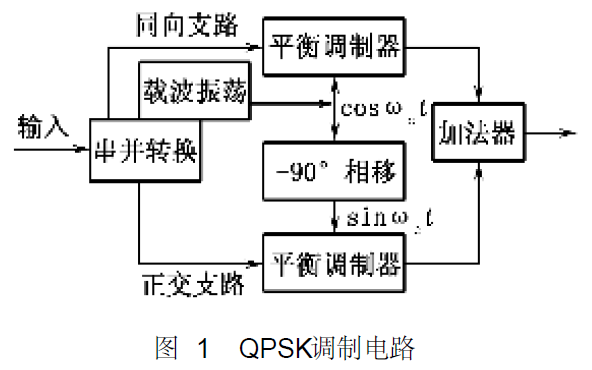

QDPSK信號是利用前后碼元之間的相對相位變化來表示數字信息。實現四相差分移相調制的方法有正交調幅法和相位選擇法。相位選擇法QDPSK調制器具有硬件實現簡單、價格低等優點,被廣泛采用,并且這種調制器非常適合數字電路實現。圖1為用相位選擇法產生QDPSK信號的組成框圖。

圖1中首先把二進制數據流經串/并變換,割裂成并列的2行,每串數據的速率是原數據速率的一半;然后對2路信號進行差分編碼;四相載波發生器分別送出調相所需的4種不同相位的載波。按照串/并變換器輸出的雙比特碼元的不同,邏輯選相電路輸出相位的載波。

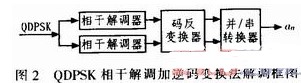

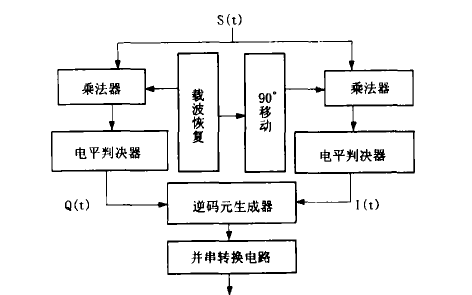

QDPSK的解調有相干解調加碼反變換法(極性比較法)和差分相干解調(相位比較法)。QDPSK相干解調加碼反變換法解調框圖如圖2所示。

圖2所示解調原理是:對QDPSK信號進行相干解調,恢復出2路相對碼,經過碼反變換器變換為2路絕對碼,再經過并/串轉換器,從而恢復出發送的數字信息。在解調過程中,由于載波相位模糊性的影響,使得解調出的相對碼也可能發生倒置,但經差分澤碼(碼反變換)得到的絕對碼不會發生任何倒置的現象,從而解決了載波相位模糊性的問題。

2 基于CPLD的QDPSK調制解調電路

2.1 QDPSK調制電路

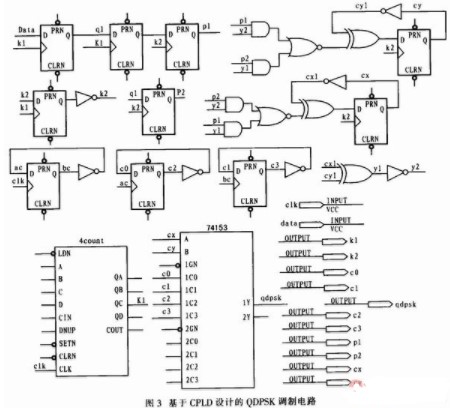

基于CPLD的QDPSK調制電路如圖3所示。

圖3所示QDPSK調制電路引腳關系為:引腳k1表示數據時鐘clk經過計數器4count的八分頻輸出,引腳k2表示數據時鐘k1的二分頻輸出,引腳ac和bc表示數據時鐘clk的二分頻輸出和二分頻反相輸出,引腳c0和c2表示數據時鐘ac的二分頻輸出和二分頻反相輸出,引腳c1和c3表示數據時鐘bc的二分頻輸出和二分頻反相輸出,c0、c1、c2和c3組成四相載波。引腳cx和cy表示信碼數據串并轉換后,在同步時鐘的作用下差分編碼后的輸出,引腳qdpsk表示輸入的信碼數據在同步時鐘的作用下四相差分移相鍵控信號輸出。

圖3所示電路器件均可從MAX+PLUSⅡ器件庫中調用。其中二分頻電路涮用1個D觸發器和1個非門組成;串并轉換電路調用4個D觸發器組成;差分編碼電路調用2個二異或門、2個D觸發器、4個2與門、2個或非門和2個非門組成:四相選相電路調用1個74153組成。調制電路在MAX+PLUSⅡ平臺上編譯、仿真通過后,打包產生qdpskb組件。

2.2 QDPSK解調電路

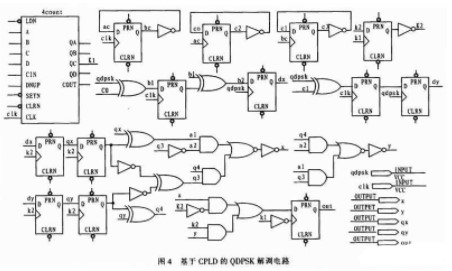

基于CPLD設計的QDPSK解調電路如圖4所示。

CPLD(Complex Programmable Logic Device)復雜可編程邏輯器件,是從PAL和GAL器件發展出來的器件,相對而言規模大,結構復雜,屬于大規模集成電路范圍。是一種用戶根據各自需要而自行構造邏輯功能的數字集成電路。其基本設計方法是借助集成開發軟件平臺,用原理圖、硬件描述語言等方法,生成相應的目標文件,通過下載電纜("在系統"編程)將代碼傳送到目標芯片中,實現設計的數字系統。

圖4所示QDPSK解調電路引腳關系為:引腳clk表示恢復的數據時鐘,引腳k1表示數據時鐘clk經過計數器4count的八分頻輸出,引腳k2表示數據時鐘k1的二分頻輸出,引腳ac和bc表示數據時鐘clk的二分頻輸出和二分頻反相輸出,引腳c0和c2表示數據時鐘ac的二分頻輸出和二分頻反相輸出,引腳c1和c3表示數據時鐘bc的二分頻輸出和二分頻反相輸出,c0、c1、c2和c3組成四相載波。引腳qdpsk表示四相差分移相鍵控信號輸入,引腳qx和qy表示四相差分移相鍵控信號的相干解調輸出。引腳x和y表示相干解調輸出在同步時鐘的作用下差分譯碼后的輸出,引腳out表示信碼差分譯碼后經并串轉換恢復的信碼數據輸出。

電路器件從MAX+PLUSⅡ器件庫中調用。其中二分頻電路調用1個D觸發器和1個非門組成;相干解調電路調用3個異或門、6個D觸發器組成;差分譯碼電路調用2個D觸發器、3個異或門、5個非門、4個與門和2個或非門組成;并串轉換電路調用2個非門、2個與門、1個或門和1個D觸發器組成。

2.3 利用CPLD設計的QDPSK調制解調電路

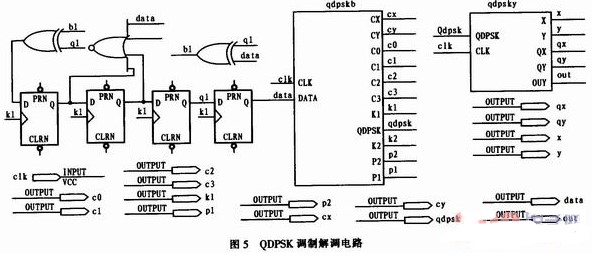

將設計的QDPSK調制電路"qdpskb"組件和解調電路"qdpsky"組件連接在一起,為了仿真實驗方便,信碼數據輸入采用四級偽隨機碼電路--從MAX+PLUSⅡ器件庫中調用4個D觸發器、2個異或門和1個四或非門,解調電路中位定時恢復電路產生的數據時鐘直接采用qdpsk調制電路數據時鐘,調制解調電路直接相連,組成的QDPSK調制解調電路如圖5所示。

QDPSK調制解調電路的引腳關系為:引腳clk表示數據時鐘輸入,引腳k1表示數據時鐘clk的八分頻輸出,引腳data表示四級偽隨機碼電路數據輸出,引腳c0、c1、c2、c3表示四相載波。引腳p1和p2表示信碼數據data在時鐘的作用下串并轉換后的輸出,引腳cx和cy表示差分編碼后的輸出,引腳qdpsk表示四相差分移相鍵控信號輸出。引腳qx和qy表示四相差分移相鍵控信號的相干解調輸出,引腳x和y表示差分譯碼后的輸出,引腳out表示信碼差分譯碼后經并串轉換恢復的信碼數據輸出。

3 實驗結果

利用MAX+PLUSⅡ開發工具建立波形輸入文件,在File菜單里面選擇New打開新建文件類型對話框,選擇Waveform Editor File項,單擊"OK".在波形編輯器窗口的Name下單擊鼠標右鍵,出現浮動的菜單,選擇Enter Nodesfrom SNF…可以打開"從SNF文件輸入觀測點"的對話框。在Type區選擇Input和Output,在默認的情況下是打開的,單擊"List"按鈕,可在Available Nodes&Groups區看到設計文件中使用的輸入/輸出信號,單擊"=>"按鈕可以將這些信號選擇到Selected N0des&Groups區。單擊"OK"按鈕,關閉對話框即可看到波形編輯窗口,將此波形文件保存為默認名。在波形文件中添加輸入/輸出信號名后,就可以開始對輸入信號建立波形了。QDPSK調制解調電路仿真波形如圖6所示。

圖6中"clk"表示輸入時鐘,"c0"、"c1"、"c2"、"c3"表示四相載波。"k1"表示數據時鐘clk的八分頻輸出,"data"表示

四級偽隨機碼電路數據輸出,"p1"、"p2"表示信碼數據data串并轉換后的輸出,"cx"、"cy"表示信碼數據串并轉換后差分編碼的輸出,"qdpsk"表示輸入的信碼數據四相差分移相鍵控信號輸出。"qx"、"qy"表示四相差分移相鍵控信號的相干解調輸出,"x"、"y"表示相干解調輸出后差分譯碼輸出,"out"表示信碼差分譯碼后經并串轉換恢復的信碼數據輸出。

仿真結果表明:QDPSK調制電路能正確選相,解調電路輸出數據在延時約5.2μs后,與QDPSK調制輸入數據完全一致。

將綜合后生成的網表文件通過ByteBlaste下載電纜,以在線配置的方式下載到CPLD器件EPM7128SLC84-15中,從而完成了器件的編程。上電后,在輸入端加入數據時鐘,用數字存儲示波器測試調制解調電路輸出,實測結果完全正確,表明達到了設計要求。

4 結論

本文利用CPLD器件,設計出的QDPSK調制解調電路,利用了EDA技術中的MAX+PLUSⅡ作為開發工具,將設計的電路圖綜合成網表文件寫入其中,制成ASIC芯片。其突出優點是自頂向下設計,查找和修改錯誤方便,同時先仿真,正確后再下載測試并應用,具有較大的靈活性;調制和解調放在一塊芯片上,集成度非常高;解調電路輸出數據延時約5.2μs,數據速率快。本文提出的QDPSK調制解調電路,已應用于小型數據傳輸系統中。

-

cpld

+關注

關注

32文章

1247瀏覽量

169220 -

無線通信

+關注

關注

58文章

4520瀏覽量

143417 -

eda

+關注

關注

71文章

2709瀏覽量

172899

發布評論請先 登錄

相關推薦

什么是EDA技術?

基于VHDL方式實現了QPSK數字調制解調電路的設計

基于F PGA的QPS K調制解調電路設計與實現

基于CPLD的QDPSK調制解調電路設計

EDA(CPLD/FPGA)技術概述

基于FPGA的QDPSK調制器的設計

FPGA與CPLD實現UART

gmsk調制解調matlab如何實現_兩種gmsk調制解調方式的實現

如何使用SystemView實現4QDPSK調制技術

如何使用軟件無線電實現QDPSK調制解調算法的硬件

基于CPLD器件和EDA技術實現QDPSK調制解調電路的設計

基于CPLD器件和EDA技術實現QDPSK調制解調電路的設計

評論