1 概述

雷達數據形成分機具有數據量大、傳輸速率高、幀格式固定等特點。目前用于雷達數據傳輸的一般有PCI總線和網卡,其中32位的PCI接口數據傳輸速率最大可以達到133Mbit/s,而目前廣泛采用的以太網卡的最大傳輸速率達到100Mbit/s,雖然這兩者的傳輸速度完全可以滿足要求,但是它們存在安裝繁瑣,受計算機插槽數量和地址、中斷資源限制等弱點.USB(Universal Serial Bus)是一種通用串行總線,具有即插即用、可熱插拔,使用方便、成本低的特點,其USB1.0能提供12Mbps的全速速率或1.5Mbps的低速速率,而USB2.0 則可以支持480Mbps的高速傳輸速率。因此,在高速數據傳輸、記錄及顯示系統中,考慮到需要方便靈活地與計算機通信,可采用USB通訊方式來對雷達數據形成分機進行檢測。

2 設計方案

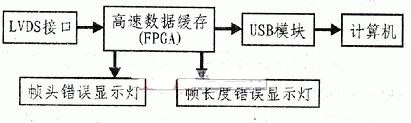

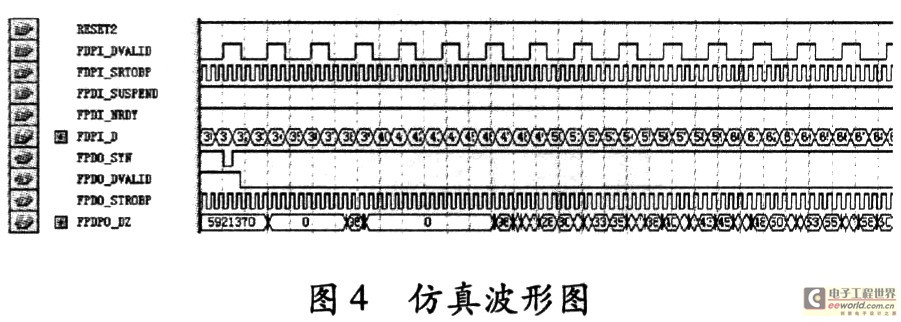

整個系統主要由低電壓差分信號(LVDS)接口電路、基于FPGA的高速數據緩存、判斷數據錯誤模塊、USB傳輸模塊和計算機組成,其系統結構框圖如圖1所示。當低電壓差分信號接口電路把接收的雷達數據形成分機數據送入FPGA緩存后,該信息便可通過USB接口進行傳輸、記錄并在計算機上顯示。該系統由低電壓差分信號驅動芯片DS90LV31(發送器)、 DS90LV32(接收器)、控制芯片XC2V500、USB控制芯片C8051F320、總線驅動器芯片74HC244組成。

3 系統功能及硬件實現

本系統主要由低電壓差分信號傳輸接口、FPGA功能模塊和USB傳輸模塊三部分構成。

3.1 低電壓差分信號傳輸接口

低電壓差分信號LVDS(Low Voltage Differential Signal)標準是一種用于高速數據傳輸的物理層接口標準。由于電壓信號擺幅較低,而且可提供電流模式驅動輸出,因此LVDS 技術只產生極低的噪音,而且功耗也極低,甚至不論頻率高低,功耗幾乎不變;此外,由于LVDS是以差分方式傳送數據,因此不易受共模噪音影響。由于具有超高速(1.4Gb/s)串行傳輸、低功耗及低電磁輻射的特性,低電壓差分信號傳輸是在銅介質上實現千兆位級高速通信的優先方案,可用于服務器、可堆壘集線器、無線基站、ATM交換機及高分辨率顯示等,也可用于通信系統的設計。美國國家半導體公司的DS90LV31和DS90LV32是高性能的CMOS低功耗、低電壓差分信號驅動器,采用3.3V供電,可支持大于400Mbps的數據率,滿足ANSI/TIA/EIA-644標準。其中DS90LV31可實現四路低電壓TTL信號轉低電壓差分信號,而DS90LV32則可實現四路低電壓差分信號轉低電壓TTL信號。

3.2 FPGA功能模塊

本設計采用Xilinx公司的FPGA Field Pro-grammable gate array,現場可編程門陣列 芯片XC2V500來實現高速數據緩存.XC2V500屬于Vir-tex-II系列,是一種高密度、高性能的FPGA.XC2V500可通過JTAG接口實現在線編程;它采用0.15m和0.12m混合工藝設計;內核電壓為1.5V,低功耗;可支持多種接口標準;內部時鐘頻率可達420MHz;采用專門的在系統可編程PROM芯片18V04進行配置。

FPGA的主要功能是高速數據緩存及判斷傳輸數據幀頭錯誤、幀長度錯誤,具體說明如下:

(1)高速數據緩存

雷達數據形成分機以10MHz的頻率,每秒發送2000~3000幀、每幀6400字節的數據,將如此高速、大量的數據進行準確無誤的緩存是本系統的技術難點之一。本方案將數據形成分機送過來的數據先放在FPGA的異步FIFO?First In First Out 存儲器里,FIFO存儲器同時要有與數據形成分機及USB的接口,且兩接口操作互不干涉,以提高數據吞吐率。根據FIFO存儲器的Full和Empty標志可判斷存儲器全滿或空.FIFO存儲器的特點是:不需要地址尋址,可簡化控制信號;數據寫入和讀出不依賴于數據速率,可以慢寫快讀、也可快寫滿讀;進行數據寬度和存儲深度的擴展不會增加額外的時間延遲,因此滿足了上述要求。

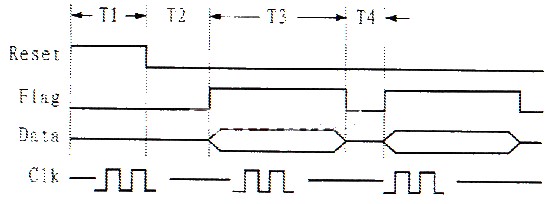

數據形成分機發送的數據包括16 Bit并行數據信號Data、數據有效標志信號Flag、時鐘信號Clk及復位信號Reset.圖2為數據形成分機與FPGA數據傳輸接口時序圖。其中Reset為清零信號,除T1時間外均保持低電平;Flag信號高電平持續時間為320μs;Clk為10MHz的讀時鐘.FPGA接收到數據形成分機發來的數據有效標志信號Flag后,將首先確定數據幀頭,然后以10MHz的時鐘頻率Clk讀16 Bit并行數據信號Data并存儲在FIFO存儲器中,以等待USB控制芯片取走。

(2)判斷幀數據錯誤

數據形成分機發送過來的每幀數據的幀頭、幀長度是固定的.FPGA對接收的每一幀數據都需要判斷幀頭及幀長度是否錯誤。每出現一次錯誤,FP-GA會對其進行一次累加,對應產生一個脈沖,然后將其用74HC244驅動后分別接LED顯示燈,就可以二進制方式顯示錯誤次數。

3.3 USB傳輸模塊

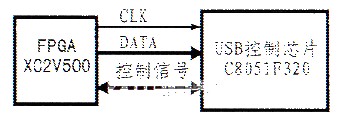

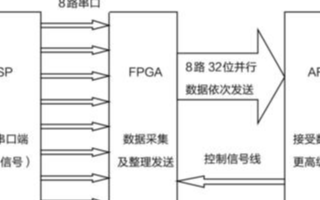

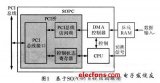

通過USB傳輸模塊可把存在FIFO存儲器里的數據傳送給計算機并記錄下來,本設計采用Cygnal公司的C8051F系列USB控制芯片C8051F320.C8051F320是將微控制器和USB控制器集成在一起的芯片,完全符合USB1.1規范,最大傳輸速度可達12Mbps.C0801F320的運行指令采用流水線結構,機器周期由標準8051的12個系統時鐘周期降為一個系統時鐘周期,處理能力大大提高。它還內嵌JTAG調試電路,可在系統編程和調試等.FPGA與C8051F320之間的具體連接控制框圖如圖3所示。

當PC機向C8051F320發出接收數據的命令后,C8051F320便可給FPGA發控制信號,以使FPGA在下一幀數據開始時打開FIFO寫使能;數據形成分機通過寫操作不斷將數據存入FIFO存儲器。當FIFO存儲器中的數據達到一幀時,Full標志有效,向C8051F320請求中斷,并將寫使能關閉,讀使能打開;C8051F320響應中斷后將以CLK時鐘頻率讀FI-FO存儲器中的數據DATA;每讀完一幀,FIFO存儲器的讀使能關閉,寫使能打開,同時接收下一幀數據,直到PC機發停止命令或接收完要求的幀數。

4 軟件設計

C8051F320中的8051內核不但與MCS-51指令完全兼容,而且Cygnal公司的工具包還為其提供了基于Windows的USB總線驅動程序和功能驅動程序,這樣,用戶就可以從煩瑣的驅動程序開發中解脫出來,從而大大減少開發時間、風險和成本。

本系統軟件設計由兩部分組成:動態鏈接庫和應用程序。動態鏈接庫負責與內核的USB功能驅動程序通信并接收應用程序的各種操作請求,而應用程序則負責對傳輸數據進行記錄、顯示并實時顯示數據傳輸的狀態。

動態鏈接庫的工作原理如下:當它收到應用程序的數據傳輸請求后,會創建兩個線程:數據傳輸線程和記錄、顯示線程。其中數據傳輸線程負責將數據寫到應用程序要提交的內存;而記錄、顯示線程則負責給應用程序發送記錄和顯示消息。當應用程序接收到此消息后,便從它提交的內存中讀取數據并存盤和顯示。

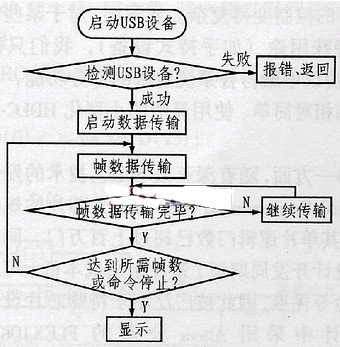

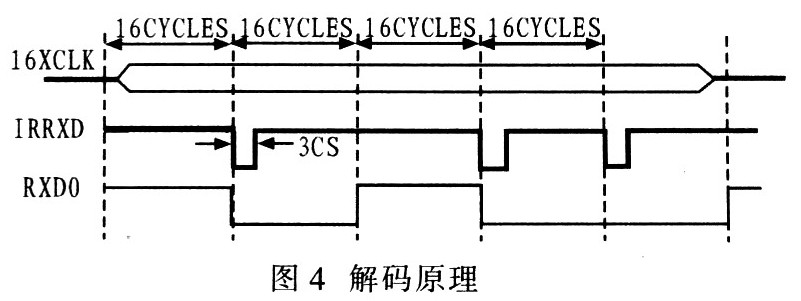

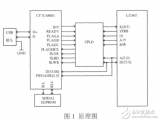

用戶態應用程序的主要功能是開啟或關閉USB設備、檢測USB設備、設置數據傳輸幀數、通過USB接口傳輸、記錄并顯示數據、實時顯示數據傳輸的狀態包括幀數、字節數等,其應用程序主流程圖如圖4所示。

本設計的應用軟件基于Windows系統,并采用VC作為軟件開發環境,這樣可以利用現有的軟件資源來縮短軟件開發周期,同時可提供一個友好、美觀清晰、操作簡單的圖形使用界面。訪問USB接口時,調用Windows API函數能及時方便地與系統的USB控制芯片進行通信,并且可以將傳輸來的數據保存并顯示在計算機上。

5 結束語

本文設計的基于FPGA和USB的高速數據傳輸、記錄系統不但具有體積小、功耗低、成本低、使用靈活方便、硬件電路簡單、可在線更新等特點;而且還充分利用了微機的資源,因而易開發且擴展性好。目前,本系統已投入實際應用之中,基本能達到高速數據傳輸、記錄及顯示的要求,具有較高的實用價值。

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598921 -

usb

+關注

關注

60文章

7773瀏覽量

262389 -

WINDOWS

+關注

關注

3文章

3503瀏覽量

87885

發布評論請先 登錄

相關推薦

基于FPGA+USB3.0接口的高速數據傳輸系統設計

高速數據傳輸PCB板設計的要點

如何使用FPGA器件和USB通訊實現高速數據傳輸顯示系統的設計

基于FPGA高速實時數據傳輸系統設計方案

基于USB2.0的紅外數據傳輸系統的設計與實現

USB2.0+FPGA實現多路數據傳輸系統

基于FPGA片上集成的高速FIFO實現緩存以及同步數據傳輸的應用

基于DSP+FPGA+ARM的架構實現高速多路數據傳輸系統的設計

如何使用FPGA器件和USB通訊實現高速數據傳輸顯示系統的設計

使用FPGA器件和USB通訊實現高速數據傳輸顯示系統的設計

使用FPGA器件和USB通訊實現高速數據傳輸顯示系統的設計

評論