引言

圖像(音頻、視頻)采集和處理是現代樓宇自動化、可視對講、電視會議以及遠程實時監控系統等應用中的核心技術。現在市面上的可視對講和安防監控產品主要是模擬通道的,且采用同軸電費傳輸。由于模擬信號的抗擾弱等問題,傳輸的距離有限并且效果不甚理想。將傳統的圖像模擬化處理改成數字化處理和傳輸,可以極大地提高圖像質量與監控效率,并且使得整個系統易于維護。

隨著嵌入式系統的不斷發展,甚至ARM或DSP的嵌入式音/視頻處理系統正逐步取代傳統的圖像處理系統,呈現強勁的發展趨勢。

1 芯片簡介

1.1 芯片基本組成及內部結構

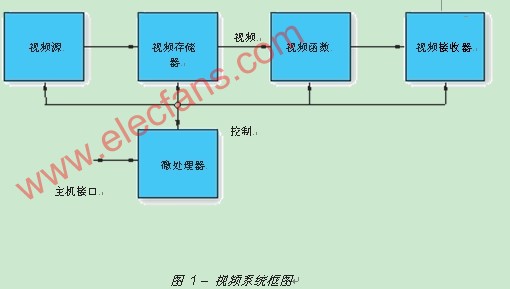

AT91M40800是Atmel公司推出的AT91 16/32位微控制器系列中具有很高性價比的一款芯片。它基于ARM7TDMI內核,內含高性能的32位RISC處理器、16位高集成度指令集、8KB片上SRAM、可編程外部總線接口(EBI)、3通道16位計數器/定時器、32個可編程I/O口、中斷控制器、2個USART(其中每個各帶2個專用外部數據控制器)、可編程看門狗定時器、主時鐘電路和DRAM時序控制電路,并配有高級節能電路;同時,可支持JTAG調試,主頻可達到40MHz。 AT91M40800內部結構模塊如圖1所示。 1.2 芯片的總體特性 AT91M40800的ARM7TDMI內核集成了嵌入式ICE接口,片內含兩大類總線:系統總線和外圍總線。系統總線連接ARM7TDMI內核與片內存儲器、外圍總線接口以及AMBA橋電路;而外圍總線由AMBA橋電路來驅動。通過可編程外部總線接口,可與片外存儲器(如Flash、ROM等)直接連接進行數據交換。具有八級優先級別的矢量中斷控制器可通過連接外圍數據控制器顯著提高音頻、視頻采集的實時性。

2 系統組成及原理

2.1 系統組成結構及芯片選擇 本系統主要由以下幾大部分組成。

(1)視頻A/D轉換部分

完成從普通CCD攝像頭采集到的模擬視頻信號到數字視頻信號的轉換,主要采用Philips公司的SAA7113芯片。SAA7113是功能強大的可編程視頻輸入處理芯片,可以同時接入4路視頻信號,使用I2C總線技術。

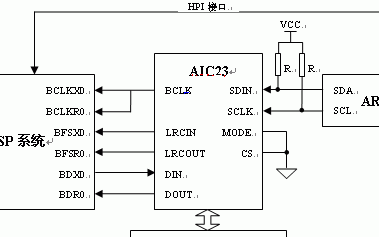

(2)音頻編解碼部分

主要實現從麥克風進入的音頻信號的編解碼,采用Philips公司的UDA1344。它將A/D和D/A轉換功能集于一身,可以對麥克風輸入的模擬聲音信號進行A/D轉換,形成串行數字音頻流。

(3)音頻視頻磁場強度處理部分

將輸入的復合音頻、視頻流進行壓縮處理,核心芯片選用***華邦電子的W99200F。該芯片具有強大的內部功能,且有多種工作模式可供選擇可供選擇,可與音頻編解碼及視頻解碼芯片實現無縫連接。

(4)邏輯門控制部分

運用FPGA進行邏輯與時序控制,采用Xilinx公司SPARTAN-IIE系列的XC2S50E邏輯控制芯片。片內集成了多種系統功能,如數字延遲鎖相環(DLL)、FIFO存儲器、變換器以及總線接口(PCI)等,可并行實現多種算法。

(5)嵌入式數據處理部分

以AT91M40800為嵌入式核心芯片,主要進行系統控制與數據處理。 (6)網絡連接部分 通過以太網控制芯片,將音頻視頻流以UDP包的形式送入網絡進行傳輸。采用Realtek公司生產的RTL8019AS作為主控制芯片。該芯片符合Ethernet II與IEEE802.3標準,采用全雙工方式,有8個中斷申請線以及16個I/O基地址可供選擇。

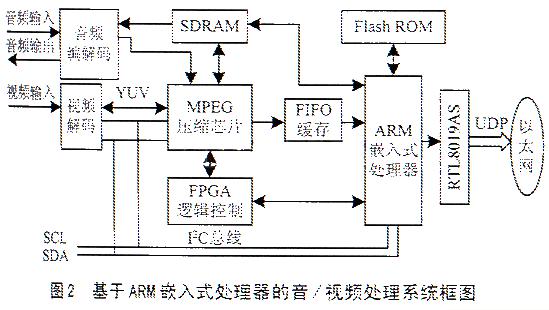

2.2系統原理框圖及工作原理

本系統原理框圖如圖2所示。 將CCD攝像頭采集到的視頻模擬信號送入A/D轉換芯片進行視頻解碼。SAA7113芯片將輸入的PAL、NISC等不同制式的模擬復位信號解碼成亮度、色度信號,輸出標準的數字視頻YUV4:2:2格式,并產生場同步參考信號VREF、行同步參考信號HREF。同時,音頻編解碼芯片UDA1344將麥克風輸入的模擬聲音信號解碼,形成的串行數字音頻流與輸出的數字視頻流復合,送入芯片W99200F進行M-PEG格式的圖像壓縮。

該芯片具有視頻預處理、圖像裁剪、運動估計單元、運動圖像補償、量化表、可變長度編碼(產生位流到SDRAM)等強大內部功能,負責將接收到的數據流進行壓縮并同步音頻、視頻信號。壓縮處理輸出的音、視頻流,通過外部緩存FIFO直接輸入AT91M40800進行整體系統數據處理。嵌入式系統初始化后,采用中斷請求方式來完成數據的采集和程序的存取,同時通過I2C總線初始化A/D轉換芯片和控制其工作狀態及工作方式。

其間,各部件的邏輯和時序控制是由FPGA來完成的,它控制中斷請求以及某些片選信號。XC2S50E內含邏輯運算、數字量監測和接口控制單元等內部資源,在與圖像壓縮芯片的接口控制中,主要完成地址發生、握手邏輯、時序控制等功能。當檢測到SAA7113芯片輸出的奇偶同步標志信號RTS0為高電平時,將此作為采集數據過程的時序起點,輸出采樣使能信號與地址選通信號;而收到像素延時結束信號,又生成相應的寫地址和寫信號。XC2S50E初始化時,置DONE為低電平,在存儲器清零時又置INIT為低,以此復位PROGRAM,將數據流輸入。

當收到嵌入式CPU采集數據的有效信號后,它控制A/D芯片采樣過程的動作;當完成了一幀數據的采集壓縮后,FPGA又向AT91M40800發出中斷請求信號并等待響應。系統數據經嵌入式處理器完成處理后,送入以太網控制芯片RTL8019AS,并最終以UDP包的形式傳送至網絡。如果網絡另一端裝備有終端機,則收到由網絡傳輸過來的數據后,可對音、視頻進行解碼,并對視頻數據進行回顯,對音頻數據進行播放。通過同樣的一個逆據進行回顯,對音頻數據進行播放。通過同樣的一個逆過程,亦可實現可視對講的功能。

3 結論與展望

基于AT91M40800芯片的嵌入式音視頻處理系統,能保證音、視頻的質量和數據處理的實時性,具有很好的可靠性和靈活性。雖然在網絡實時傳輸和系統軟件編程上還面臨一些挑戰,但是隨著嵌入式系統和圖像處理技術的不斷發展,這些都不會成為該系統推廣應用的障礙。將其應用在可視對講、遠程監控、可視IP電話等領域,將會具有廣闊的發展前景和應用市場。

-

芯片

+關注

關注

454文章

50432瀏覽量

421900 -

嵌入式

+關注

關注

5069文章

19021瀏覽量

303414 -

視頻

+關注

關注

6文章

1934瀏覽量

72818 -

監控系統

+關注

關注

21文章

3863瀏覽量

173504

發布評論請先 登錄

相關推薦

MSN音頻視頻交流過程分析

音頻視頻制作

基于AT91M40800的音頻視頻處理系統設計

基于AT91M40800 的音頻視頻處理系統設計

基于PC的可視電話音頻視頻子系統的實現

基于ARM7處理器的實時測控系統開發平臺

基于DSP的多路音視頻采集處理系統設計

全集成設計環境下的視頻處理系統開發

采用AT91m40800與μC/OS-II系統對海底大地電磁數據采集器進行改進

基于小波變換與DSP的實時音頻視頻處理系統

基于DSP和ARM的音頻處理系統設計

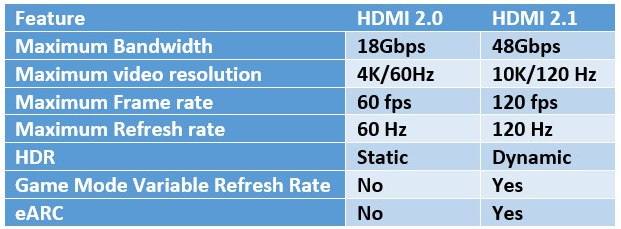

HDMI 2.1:引導 GenX 音頻視頻體驗

AT91M40800的原理構造及在音頻視頻處理系統中的應用設計

AT91M40800的原理構造及在音頻視頻處理系統中的應用設計

評論