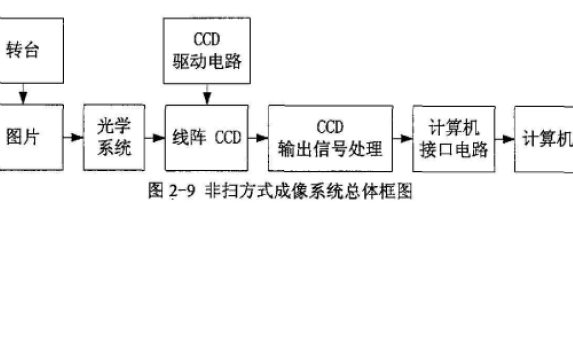

CCD驅動電路的設計是CCD應用的關鍵問題之一。由于不同廠家生產的CCD的驅動時序不盡相同,同一廠家不同型號的CCD驅動時序也不完全一樣,因此CCD用戶必須面對驅動電路的設計問題。以往采用不同功能的數字芯片搭成的驅動電路,調試困難,靈活性較差。而采用EPROM設計驅動時序,雖然設計的系統性能穩定,但是器件要工作還需要地址發生器,不但增大電路板面積,存儲的數據也不能在系統修改。本文以TCD1208AP為例,說明CCD時序發生器的設計原理,基于在系統可編程(ISP)技術和ispLSI器件實現了系統設計和仿真。ispLSI系列器件提供編程口,可直接修改其內部程序。

CCD的時序分析

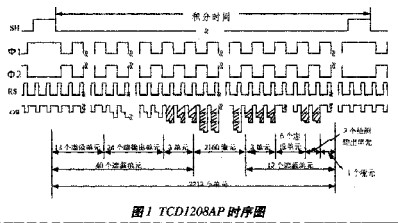

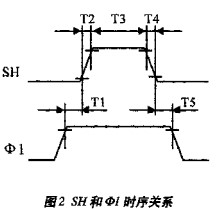

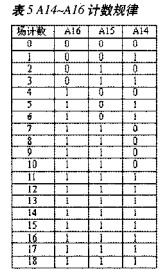

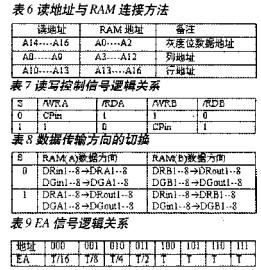

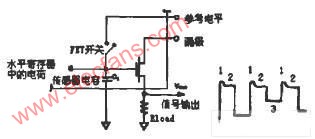

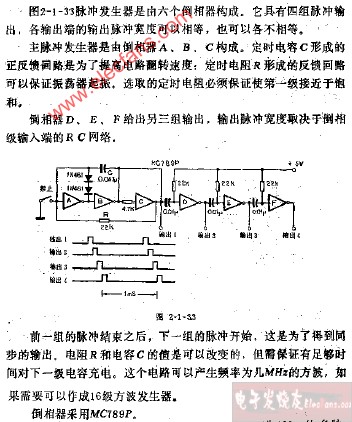

二相線陣CCD圖像傳感器TCD1208AP,時序關系如圖1所示。需要4路驅動信號,即:轉移信號SH,脈沖寬度標準值為1000ns,其周期為光信號積分時間;復位信號RS,時鐘頻率標準值為1MHz,復位一次輸出一個信號;兩相移位時鐘信號F1與F2,時鐘頻率標準值為0.5MHz。TCD1208AP是2160像元CCD,正常工作時,要輸出52個虛設單元(含暗電流信號)信號。因為該器件是兩列并行傳輸,所以在一個周期內至少要有1106個F1脈沖,即TSH》1106T1。時序圖中需要特別關注的是SH與F1、F2的關系,當SH高電平期間,CCD積累的信號電荷包通過轉移柵進入移位寄存器。這期間,移位脈沖F1、F2要求保持一個高和低的電平狀態。其中SH與F1時序關系如圖2。

ISP技術及ispLSI器件

在系統可編程打破了傳統可編程邏輯器件(PLD)的局限,使硬件設計變得象軟件一樣易于修改,從而縮短了系統的調試周期,而且不需要編程器,更不需要編程高壓。

ispLSI系列器件是Lattice公司推出的高性能大規模可編程邏輯器件,集成度在1000門到25000門之間,引腳至引腳延時最小可達3.5ns,系統工作速度最高可達180MHz。ispLSI1016由可編程宏邏輯單元組成,而每個宏邏輯單元既可以定義成組合邏輯,又可以定義成時序邏輯。它有2000個等效邏輯門,32個通用I/O單元能定義成輸入、輸出、三態或雙向端口,另外還有4個專用的時鐘輸入端。

CCD時序發生器的設計

基于ispLSI1016的設計流程

Synario軟件能夠支持ispLSI器件的設計、編譯和邏輯模擬,能夠進行原理圖輸入和ABEL-HDL硬件描述語言輸入,并且還提供了功能仿真器,可以用報告形式或波形觀察器檢查仿真結果。Synario的混合式設計輸入方式允許在同一器件的設計中同時采用原理圖、高級語言、真值表和狀態機輸入方式。基于ispLSI1016器件設計CCD時序發生器時,邏輯設計流程包括下列步驟:設計輸入、設計實現、器件編程、設計校驗等。

* 設計輸入:首先按CCD時序發生器的原理將其分成高低幾個邏輯關系層。利用模塊化的設計方法,對各部分邏輯關系使用原理圖與硬件描述語言混合進行描述。

* 設計實現:從設計輸入文件到熔絲圖文件的編譯實現。包括:邏輯、合并、映像、布局、布線、生成編程數據文件(JEDEC)。為方便設計需要,使用軟件的引腳鎖定功能將信號連接在指定的引腳上。除端口鎖定需人工干預外,所有的布局和布線過程均可自動完成。

* 器件編程:把JEDEC形式的文件傳送到器件中。ispLSI的編程和改寫由片內的狀態機控制,狀態機的輸入即為片內的5個編程接口信號。

* 設計校驗:設計校驗過程與設計過程是同步進行的,針對設計輸入、設計實現和器件編程,設計校驗可分為前仿真、后仿真和實驗驗證三個部分。在設計輸入階段,進行的功能仿真驗證邏輯功能,所以又稱功能仿真;后仿真又叫時延仿真,是在選擇了具體器件并完成布局布線后進行的定時關系仿真。

設計實現與仿真

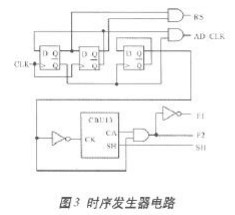

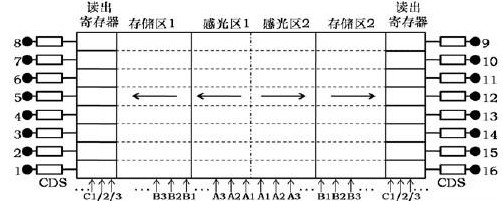

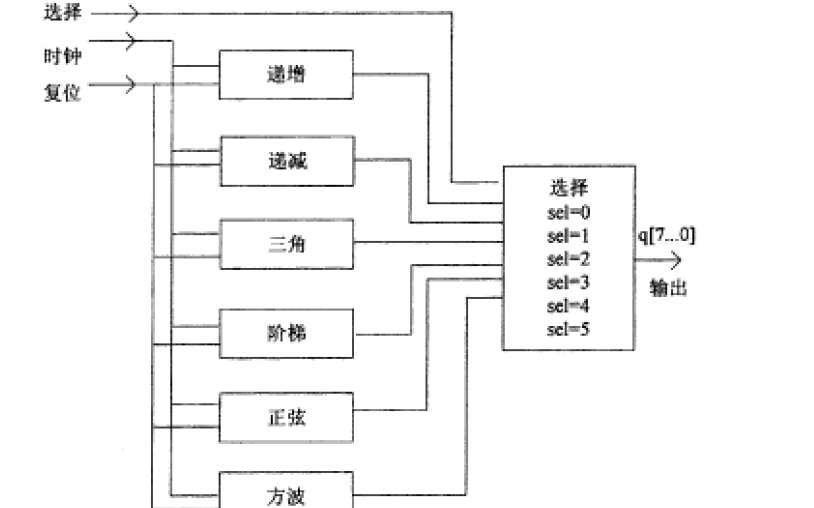

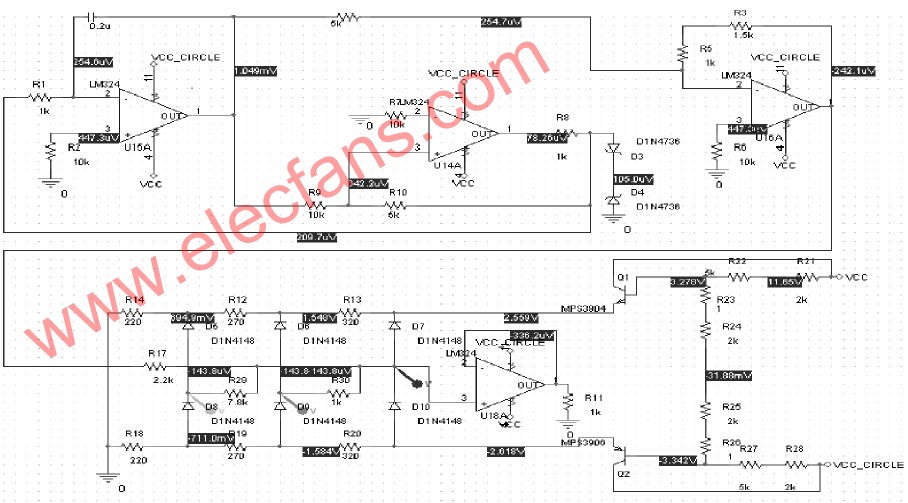

時序發生器電路如圖3所示,4MHz時鐘信號CLK經4分頻及邏輯組合電路產生頻率為1MHz的復位脈沖RS和A/D控制信號AD_CLK(采樣脈沖);再經2分頻產生0.5MHz的計數脈沖。這個計數脈沖送入計數器CBU13,CBU13是13位計數器,此模塊由ABEL-HDL硬件描述語言編寫完成。根據CCD時序分析,計數器最低計數值為1106,增加計數值就延長了積分時間;計數器計滿則產生轉移脈沖控制信號SH。CBU13的功能就是完成積分時間控制,即通過計數器輸出控制邏輯,產生SH信號和兩相移位脈沖信號的控制信號CA,信號CA與計數脈沖經過與邏輯就得到F2(F2),而F2取反就得到F1(F1)。信號CA主要是控制SH高電平時與F1(F1)的關系,如圖2所示。具體設計時,只需當計數器滿時讓組合邏輯電路產生一個持續時間為1個計數周期以上的高電平信號(其它時間為低電平),就可作為SH。另外產生一個持續時間≥2個計數脈沖周期的低電平信號,這個信號和0.5MHz的計數脈沖經過與門后就得到需要的F2。

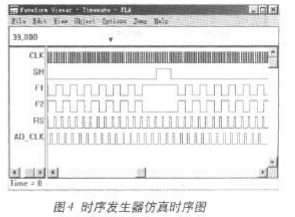

時序發生器設計完成后,經過軟件仿真,得到如圖4所示的波形,圖中所示的時序關系滿足圖1的要求。用Synario軟件設計驅動電路時,可以采用原理圖、ABEL-HDL等多種方式。設計CCD驅動電路時,先將系統劃分為不同的功能模塊,功能復雜的模塊均采用硬件描述語言設計。因為應用時只需根據具體CCD器件的要求修改積分時間等參數即可,如果采用原理圖則需修改連接線路。

結語

CCD驅動電路一般有四種設計方法,分別為存儲器驅動、IC驅動、單片機驅動、以及可編程邏輯器件驅動。采用ispLSI器件設計CCD時序發生器,使得電路由原來復雜的設計變成主要只用一片ispLSI1016來實現。獨立的單元測試與系統聯調結果均表明:采用ISP技術實現CCD時序發生器,提高了系統的集成度;系統抗干擾能力和穩定性也增強了;同時還使設計與調試周期縮短至小時數量級

-

傳感器

+關注

關注

2548文章

50698瀏覽量

752048 -

發生器

+關注

關注

4文章

1363瀏覽量

61623 -

仿真

+關注

關注

50文章

4044瀏覽量

133424

發布評論請先 登錄

相關推薦

基于FPGA與的VHDL語言驅動時序發生器與數據緩存器的一體化設計

如何完成基于FPGA技術的驅動時序發生器與數據緩存器的一體化設計?

CPLD設計的CCD信號發生器技術

基于FPGA的DDS波形信號發生器的設計

采用FPGA設計科學級CCD相機時序發生器

采用3級LFSR實現Gollmann流密碼發生器的設計并進行仿真驗證

如何使用智能函數發生器進行VHDL的設計與仿真

CCD的工作原理和幾種產生CCD驅動時序方法

ADDI9020:帶V驅動器和精密時序發生器的60 MHz CCD信號處理器數據表

采用ispLSI器件設計CCD時序發生器并進行仿真驗證

采用ispLSI器件設計CCD時序發生器并進行仿真驗證

評論