對于需要在PCB板上使用大規模FPGA器件的設計人員來說,I/O引腳分配是必須面對的眾多挑戰之一。 由于眾多原因,許多設計人員發表為大型FPGA器件和高級BGA封裝確定I/O引腳配置或布局方案越來越困難。 但是組合運用多種智能I/O規劃工具,能夠使引腳分配過程變得更輕松。

在PCB上定義FPGA器件的I/O引腳布局是一項艱巨的設計挑戰,即可能幫助設計快速完成,也有可能造成設計失敗。 在此過程中必須平衡FPGA 和 PCB兩方面的要求,同時還要并行完成兩者的設計。 如果僅僅針對PCB或FPGA進行引腳布局優化,那么可能在另一方面引起設計問題。

為了解引腳分配所引起的后果,需要以可視化形式顯示出PCB布局和FPGA物理器件引腳,以及內部FPGA I/O點和相關資源。 不幸的是,到今天為止還沒有單個工具或方法能夠同時滿足所有這些協同設計需求。

然而,可以結合不同的技術和策略來優化引腳規劃流程并積極采用Xilinx PinAhead技術等新協同設計工具來發展出一套有效的引腳分配和布局方法。 賽靈思公司在ISE軟件設計套件10.1版中包含了PinAhead。

賽靈思公司開發了一種規則驅動的方法。首先根據PCB和FPGA設計要求定義一套初始引腳布局,這樣利用與最終版本非常接近的引腳布局設計小組就可以盡可能早地開始各自的設計流程。 如果在設計流程的后期由于PCB布線或內部FPGA性能問題而需要進行調整,在采用這一方法晨這些問題通常也已經局部化了,只需要在PCB或FPGA設計中進行很小的設計修改。

步驟1: 評估設計參數

那么,從哪里開始呢? 首先應當盡早制定I/O分配策略。 但沒有優化工具或完整的網表,完成這一任務可能很困難。

首先,讓我們先回答幾個問題來確定PCB物理參數和限制:

* PCB板有幾層、走線寬度以及過孔尺寸多大?

* PCB參數對可使用的FPGA封裝類型(如BGA)有限制嗎?

* PCB上有沒有FPGA必須使用的固定接口位置? 其它芯片、連接器或布局限制?

* 哪些高速接口需要特別關注?

能否將布局策略可視化,從而保證最短互連?

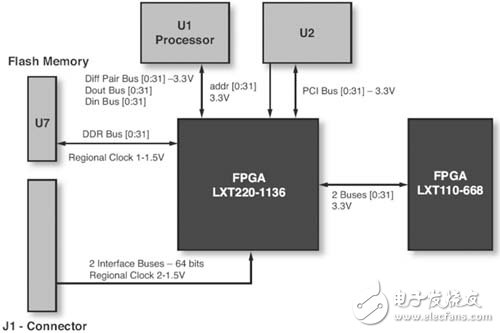

你會發現畫一張PCB布局圖很有幫助。PCB布局圖上應當包括所有主要元器件以及關鍵接口和總線,從而可以幫助確定最佳的FPGA引腳分配。 請注意將元器件畫在PCB板的實際安裝面上。 標注出需要特別關注的接口,如高速總線和差分對(圖1)。

下一步,檢查FPGA器件的布局來了解芯片上的物理資源所在。 列出設計中使用的不同電壓和時鐘,開始隔離設計需要的接口。 然后確定設計是否使用特殊的I/O接口資源,如千兆收發器(GT)、BUFR、IODELAY以及數字時鐘管理器。這些資源可能需要將有關的I/O引腳布署得盡量互相靠近。

現在需要確定設計中使用的PowerPC、DSP48和RAM16等FPGA資源的位置。 將連接到I/O組的任何相關I/O盡量置于盡相關資源最近的地方。 然后看一下能否將某些I/O信號組合到接口,這對于引腳分配很有幫助。 最后,確定FPGA的配置模式。

圖1 PCB連接圖

步驟2: 定義引腳布局要求

一旦了解了主要的FPGA接口并創建了物理布局的原型,就可以定義引腳布局了。 有些設計人員喜歡使用包含所有I/O信號數據表來保持與引腳的對應。 你可以按電壓、時鐘、接口或總線對它們進行分組。 這一方法確實非常有用,因為它可幫助你將信號組合成組,從而在分配引腳時可以按組進行。 這一階段,你還會發現為了實現最優PCB布線,有些關鍵接口必須置于器件的某個邊,或者利用外部物理引腳。

在考慮到FPGA和PCB要求并確定了主要的接口位置以后,下一步是根據所有這些條件將引腳分配給I/O組。 這也是真正開始工作的地方。 在當前的設計流程中,引腳分配時一項耗費時間的任務,在解決任何性能和信號完整性問題的過程中可能會涉及許多嘗試和錯誤。 傳統上,設計人員都是徒手畫圖來完成這項任務的,因為EDA和芯片供應商沒有提供幫助設計人員將FPGA和PCB引腳布局可視化的工具。

但現在賽靈思公司提供了相應的工具。 在ISE Foundation軟件工具10.1版本中包含的PlanAhead Lite是PlanAhead設計、分析和平面布局工具的簡化版。 其中包括的針對PCB 和 FPGA設計的PinAhead的工具使得I/O引腳配置更為容易。

這里我們不打算詳細介紹該工具的所有細節,而只是看一下如何將其用于I/O引腳分配。 如果你希望了解PinAhead的更詳細信息,包括視頻展示和教程,請訪問 www.xilinx.com/planahead。

步驟3: 利用PinAhead進行引腳分配

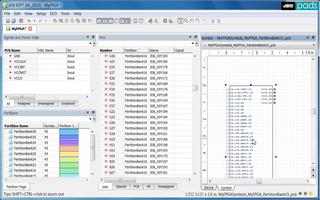

PinAhead環境提供了一組不同的視圖。利用這些視圖可以幫助完成I/O端口信息與物理封裝引腳或裸片I/O盤(Pad)的對應和分配(圖2)。

PinAhead的圖形環境與PlanAhead類似,在器件視圖中清晰地顯示出芯片上的I/O盤和相關資源,并在封裝視圖中顯示出物理器件引腳。 視圖同時顯示出I/O端口和物理引腳信息,這樣可以通過交叉選取來試探邏輯設計和物理器件資源的對應。

你可以在沒有設計網表的情況下使用PinAhead來嘗試器件資源,或者直接開始I/O引腳規劃流程。 封裝引腳視圖(“Package Pins” view)根據器件數據表列出了器件封裝技術參數,因此大多數情況下在進行引腳配置時都不再需要去參考器件數據手冊。 封裝引腳視圖以列表形式對I/O組(bank)進行了分類,因此可以同時在器件和封裝視圖中交叉選擇和高亮顯示I/O組。 視頻清晰顯示出物理引腳位置和裸片中的I/O盤的關系,從而簡化了I/O組的優化選擇。 封裝引腳視頻還顯示了I/O組中每一引腳的信息。

你可以利用PinAhead接口從頭開始創建I/O端口,也可以從CSV格式數據表、HDL源文件頭或綜合后的網絡和UCF格式約束文件中導入I/O端口。 I/O端口視圖(“I/O Ports” view)顯示出設計中定義的所有I/O端口信號,總線文件夾則顯示分組的總線和差分對信號。

你可以按不同方式對封裝引腳和I/O端口視圖進行排序。 可以切換列表視圖顯示基于分類的列表或全部列表,或者點擊鼠標對封裝引腳視圖進行排序,顯示所有可用的全局時鐘或地區時鐘引腳。 同時還可以將信息導出到CSV格式數據表,做為引腳配置的出發點。

PinAhead還提供了一個界面,支持有選擇地禁止PinAhead將I/O端口分配給某些I/O引腳、I/O引腳組或I/O組。 可以在封裝引腳、器件或封裝視圖中選擇和禁止引腳。 例如,你可以對封裝引腳視圖(Package Pins view)排序并禁止所有VREF引腳。

PinAhead允許將相關的I/O端口和總線組合為“接口”(interface)。 這樣組合使你可以將相關I/O端口做為單個實體處理,從而簡化了I/O端口管理和分配任務。 接口組合功能可以更容易地可視化顯示和管理與特定邏輯接口相關聯的所有信號。

可方便地在設計間拷貝接口,或者利用接口組合生成特定接口的PCB原理圖符號。 組合后的接口在I/O端口視圖中以可擴展文件夾的形式出現,通過在視圖中選擇I/O端口并將其拖動到接口文件夾,可以將額外的I/O端口添加到接口組合中。

當創建I/O端口時,可將其分配到封裝引腳或I/O盤(pad)。 在此之前,最好先檢查一下I/O端口的最初PCB互連草圖并與PCB設計人員協商,了解布放不同I/O端口接口的相關位置和其它需考慮的因素。 適當的總線順序和邊緣距離有PCB布線非常有幫助,可以大大節約設計時間。

通過將單個引腳、總線和接口拖動到器件或封裝視圖,可以將它們分配到I/O引腳。 利用不同的分配模式,可以將引腳組分配給選定的I/O引腳。 可用的模式包括“Place I/O Ports in an I/O Bank,” “Place I/O Ports in Area,” 以及 “Place I/O Ports Sequentially.”。

每種模式提供了將I/O端口分配到引腳的不同分配方式。 利用這些模式,可以通過鼠標光標處彈出的窗口了解你所分配的端口數量信息。 直到分配了所有選定I/O端口之前,這一模式一直保持。

器件視圖(Device view)以圖形方式顯示所有時鐘區域和時鐘相關的邏輯對象,從而使時鐘相關的I/O分配更容易、更直觀。 選擇一個時鐘區將會顯示所有I/O組、時鐘相關的資源以及與其相關的器件資源。

PlanAhead軟件試圖保證你在引腳分配時始終符合規則。 在你的指引下,PlanAhead工具將差分以端口分配給適當的引腳對。 當交互式指定I/O端口時,工具會運行規則檢查(DRC)來保證布局是合乎規則的。

工具缺省設置運行在交互DRC模式,當然你也可以選擇關閉這一模式。 工具會檢查電壓沖突、VREF引腳或I/O標準沖突,以及位于GT器件附近的噪聲敏感引腳。 當發現錯誤或問題時,工具會顯示一條提示信息(Tooltip),告訴你為什么不能夠將某個I/O端口分配給特定的引腳。

通過激活 PinAhead的 “Autoplace”命令,還可以讓其自動分配所有或任何選擇的I/O端口到封裝引腳。 Autoplace命令將會遵守所有I/O標準和差分對規則,并正確布署全局時鐘引腳。 該命令還會嘗試盡量將I/O端口組合為接口(interface)。

器件視圖(Device view)以圖形方式顯示所有時鐘區域和時鐘相關的邏輯對象,從而使時鐘相關的I/O分配更容易、更直觀。 選擇一個時鐘區將會顯示所有I/O組、時鐘相關的資源以及與其相關的器件資源。 通過可用資源與其物理關系的探索,區域時鐘規劃過程變得更容易。

還可利用PinAhead布局設計中其它與I/O相關的邏輯,如BUFG、BUFR、IODELAY、 IDELAYCTRL和DCM。 利用PlanAhead中的“Find”命令,可以方便地定位這些對象和布放點。 要想有選擇地察看的擴展邏輯和邏輯連接,請使用工具中的原理圖視圖(“Schematic” view)。

通過在PlanAhead軟件中的某個視圖中選擇特定的I/O相關邏輯并將其拖動到器件視圖(Device view)中的選定位置,就可以鎖定其布局。

PlanAhead軟件將會自動判斷,僅允許將有關邏輯放在合適的位置。 在拖動設計中的邏輯對象時,動態光標會顯示出適當的布局位置。

步驟4: 為最終核簽(Sign-Off)運行DRC和WASSO

一旦完成引腳分配,就可利用 PinAhead豐富的DRC規則來進行核簽前的DRC檢查,保證在運行PlanAhead軟件實施工具前設計是無錯的。 工具中的眾多I/O和時鐘相關規則可保證I/O布局是合法的。 可利用PlanAhead的DRC對話框來選擇相應的規則。

如果工具發現違反規則的情況,將會顯示帶有錯誤信息的DRC結果表。 選擇相應的錯誤信息可以更進一步入地了解有關情況。

PlanAhead還提供了加權平均同步轉換輸出(WASSO)分析功能,可幫助識別引腳分配引起的潛在信號完整性問題。 為工具提供PCB設計的寄生參數特性,PlanAhead軟件將會分析不同的I/O組以及其近鄰,并報告每一I/O組的利用情況和狀態。

步驟5: 導出I/O引腳分配數據

你可以將I/O端口列表和封裝引腳信息從PlanAhead軟件導出為CSV格式文件、HDL頭或UCF文件。 CSV文件包括有關器件封裝引腳的所有信息,以及與設計相關的I/O引腳分配和配置。 列表中的封裝引腳部分是數據表中定義I/O端口的很好起點。

你還可以利用該數據表自動生成設計小組開始PCB布局所需要的PCB原理圖符號。 然而,有時這些符號對于原理圖來說太長了,可能需要將它們縮短為幾個符號。 利用PinAhead中的創建的接口組可以快速做到這一點。

以原理圖符號形式提供這些I/O引腳配置為PCB設計人員開始PCB布局提供了很好的基礎。 因為如果在引腳分配的最初就考慮到PCB接口,那么最很可能與最終的引腳配置比較接近。

如果確實需要改變引腳來方便布線,那么改變也比較容易,因為需要改變的引腳可能已經在I/O組內了。 這種方法不會對FPGA設計造成太大的影響。 通過在PCB和FPGA設計人員之間傳遞修改過的引腳布局數據表或UCF文件,可以保證兩個部分之間的任何修改是同步的。

為防止信號噪聲以及支持某些FPGA功能,你還可能希望將未用的引腳或特定配置的引腳連接到VCC或GND。 賽靈思目前正在致力于在PinAhead的下一版本中提供這一功能。通過一個界面方便FPGA設計人員指導此類引腳,并在輸出的CSV數據表中包含相應的引腳連接。 這樣PCB設計人員就可以更容易識別相關引腳并正確連接之。

未來,隨著FPGA集成更復雜的功能以及使用更先進的封裝,發展可靠的FPGA和PCB引腳布局方法勢在必行。 PinAhead Lite在幫助實現基于協同設計理念的引腳布局策略方面已經能夠提供很大幫助,但我們仍然已經在致力于改進這一工具以幫助設計人員更好地應對引腳布局方面的挑戰。

圖 2 PinAhead 環境

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601861 -

pcb

+關注

關注

4317文章

23006瀏覽量

396302 -

元器件

+關注

關注

112文章

4692瀏覽量

92011

發布評論請先 登錄

相關推薦

FPGA中的I_O時序優化設計

FPGA-PCB優化技術降低制造成本

檢查FPGA的FPGA功能和I/O引腳的方法

FPGA的I/O與外設的連接擴展要點

如何獲得Virtex 5器件的實際I/O bank布局?

組合運用多種智能I/O規劃工具能使引腳分配過程變輕松

基于FPGA I/O接口的五大優勢與FPGA深層分析

如何減少器件間通信所用的I/O引腳數實現雙向通信

FPGA器件的I/O引腳布局的優化方案分析

FPGA器件的I/O引腳布局的優化方案分析

評論