1、 主要特點

CH361是一個簡便易用的PCI總線通用接口芯片。該器件在本地端提供了通用的8 位數(shù)據(jù)總線。由于其支持I/O 端口映射和擴展ROM 映射,因而可廣泛應用于制作低成本的基于PCI總線的計算機板卡,或者用于將原先基于ISA 總線的板卡移植到PCI總線上。

CH361的主要特點如下:

● 帶有通用8位主動并行接口:包括8位數(shù)據(jù)、16位地址、I/O讀和寫以及存儲器讀和寫;

● 可以設定PCI設備的設備標識(Vendor ID,Device ID,Class Code 等);

● 支持長度達240字節(jié)的I/O端口;

● 允許本地硬件地址實現(xiàn)專用I/O端口,可直接移植ISA板卡到PCI總線;

● 具有兩種I/O端口存取速度:分別為60ns和240ns;

● 支持直接映射容量為8kB或者32kB的擴展ROM(Boot ROM);

● 支持通過8kB或者32kB擴容窗口映射的、容量為64kB/128kB的擴展ROM;

● 支持擴展ROM(Boot ROM)的寫操作,同時支持存儲器SRAM和閃存Flash-Memory;

●內(nèi)置預引導Mini-Boot-ROM,可支持擴展ROM模擬;

●內(nèi)置I2C主設備接口,可掛接I2C從設備;

●支持本地設備數(shù)據(jù)等待,并可提供本地數(shù)據(jù)輸入緩存;

●內(nèi)置4μs~1ms的硬件計時單元,用于延時;

●采用80個腳的LQFP80和PQFP80兩種形式;

●采用了4項專利技術(shù)和多項專有技術(shù),低成本,簡便易用。

2、 引腳功能

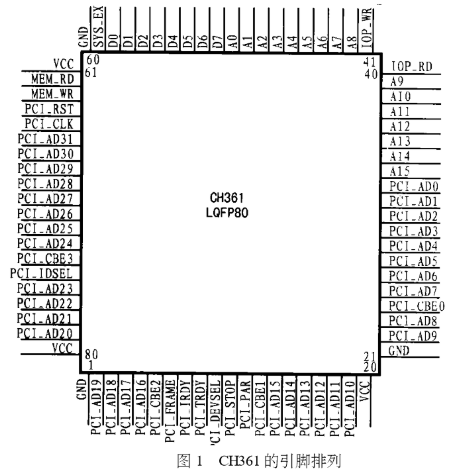

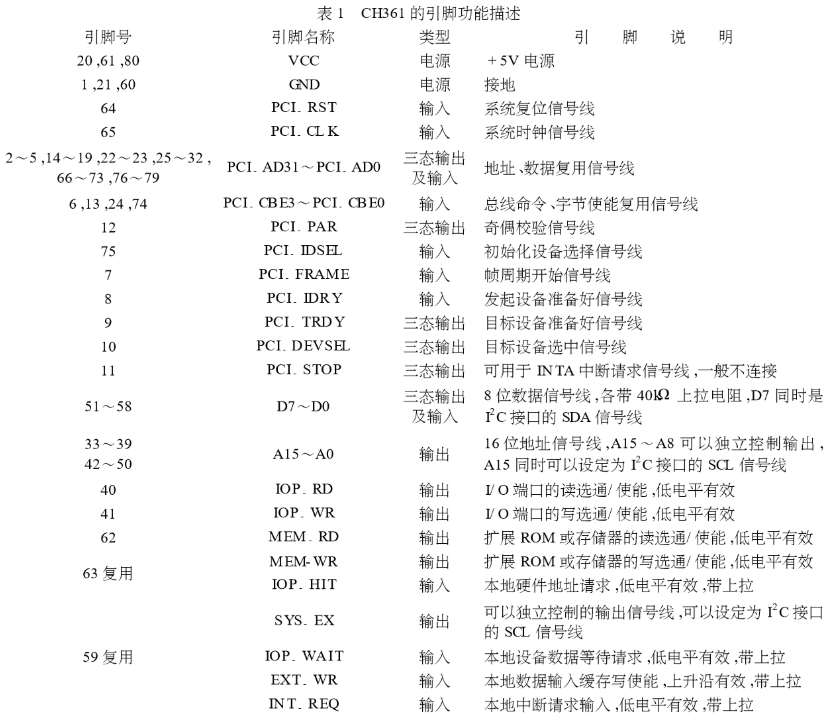

CH361接口芯片的引腳排列如圖1所示。各引腳功能如表1所列。

3、 工作模式

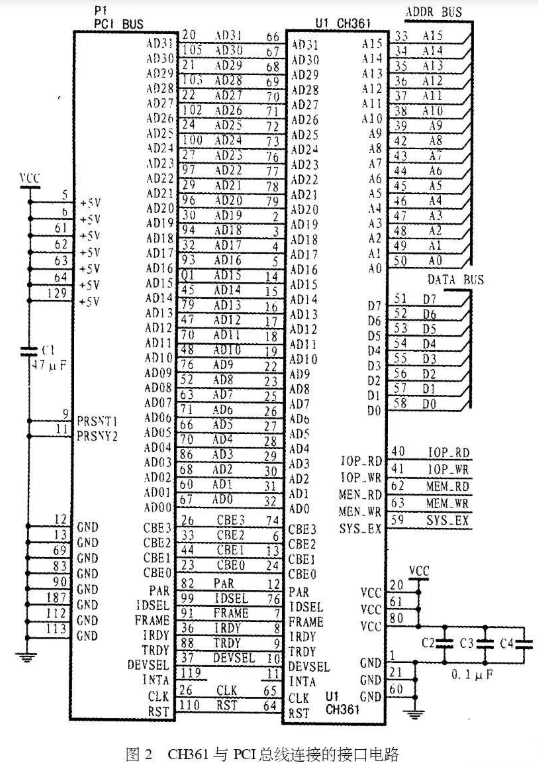

為了在不增加引腳的前提下提供更多可用功能,CH361對部分引腳進行了復用,并可通過“工作模式設定”進行功能選擇。“工作模式設定”的具體方法如下:首先將本地端8位數(shù)據(jù)信號線采用上拉或者下拉的方式設定為所需的高電平或者低電平,以便在CH361被復位后根據(jù)這些信號線的默認狀態(tài)來設定工作模式以及參數(shù);這些信號線在作為8 位數(shù)據(jù)總線被驅(qū)動時,由于一般外部設備的驅(qū)動電流不小于1mA,所以,上拉或者下拉不會影響其對數(shù)據(jù)總線的驅(qū)動;另外,CH361僅在復位后的1μs內(nèi)一次性設定工作模式及參數(shù),所以,如果外部設備的驅(qū)動能力很小或者是采用OC 集電極開路驅(qū)動,那么,系統(tǒng)僅在復位后的短時間內(nèi)實現(xiàn)下拉,而在其余時間屏蔽下拉或者轉(zhuǎn)換成上拉。表2和表3所列為設定工作模式和參數(shù)時所對應的數(shù)值(1 即高電平,0 即低電平)。[page]

4、 CH361的典型應用

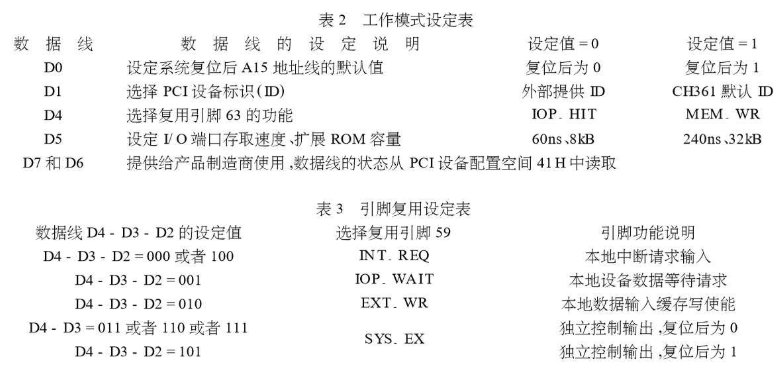

4.1 與PCI總線的連接電路

圖2所示是CH361與PCI總線進行連接的接口電路,圖中,電容C1~C4用于電源退耦,而C2~C4應分別并聯(lián)在CH361的三對電源引腳上。圖中,PCI總線的電源線引腳可以自由選擇,但數(shù)量不得少于4對.CH361屬于高頻數(shù)字電路,因此,設計PCB板需要參考PCI總線規(guī)范。

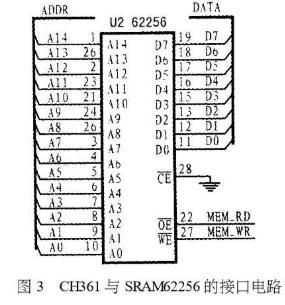

4.2 與存儲器的連接電路

圖3是CH361與SRAM62256存儲器的接口電路。圖中,CH361通過MEM_RD和MEM_WR與存儲器U2(型號是SRAM62256)連接。因為CH361只在PCI設備配置空間中提供擴展ROM基址寄存器,而計算機BIOS通常不會為SRAM設置擴展ROM基址,所以在讀寫存儲器U2前,需要設置擴展ROM基址寄存器,以將存儲器U2映射到存儲器空間。也就是說,向CH361的擴展ROM基址置入地址值0E0000001(該地址不能與其它設備的存儲器地址相沖突,最低位置1是為了啟用擴展ROM)后,U2即被映射到0E0000000H至0E0007FFFH 的地址空間,這樣,當計算機讀寫0E0001234H 地址的存儲器時,實際上就是讀寫存儲器U2的1234H地址的內(nèi)容。

如果將普通的SRAM換成雙端口SRAM,則CH361可以通過雙端口存儲器與外部的單片機或者DSP交換數(shù)據(jù).CH361使用8位數(shù)據(jù)總線,所以,向SRAM寫入數(shù)據(jù)只能以字節(jié)為單位進行,但從SRAM讀出數(shù)據(jù)則能夠以字節(jié)、字、雙字為單位進行.CH361通過存儲器與外部電路交換數(shù)據(jù)的實測速度可以達到每秒1.5M字節(jié)。

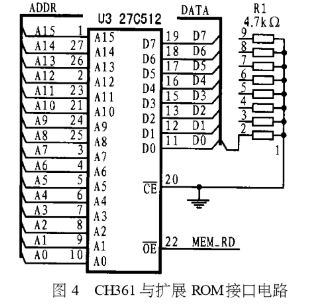

4.3 連接擴展ROM

圖4是CH361與擴展ROM的接口電路.CH361可通過MEM_RD與ROM芯片U3(型號是27C512)進行連接。它支持EPROM和閃存Flash-Memory,容量可以是32kB或者64kB.如果將SYS_EX用于A16地址線,則最大容量可達128kB.一般情況下烠H361可以直接支持32kB容量的擴展ROM(即27C256芯片的容量),也可以在擴展ROM的程序中通過控制A15地址線支持64kB容量的ROM芯片。下拉電阻R1用于CH361的工作模式設定,因為圖中的數(shù)據(jù)線D0連接了下拉電阻,所以,系統(tǒng)復位后,地址線A15為低電平以選擇U3的低32kB(地址為0000H-7FFFH),而在需要讀取U3的高32kB時(地址為8000H-0FFFFH),可以通過寫芯片控制寄存器的位0來重新設定A15地址線,SYS EX連接A16地址線時與A15的用法類似。另外,由于PCI擴展ROM中的內(nèi)容通常被BIOS復制到RAM內(nèi)存中,所以需要設置CH361的擴展ROM基址以重新將U3映射到存儲器空間.CH361的A15引腳不僅能用作地址線,還可以自由控制,例如在需要同時連接SRAM和ROM時,可通過A15切換兩者的片選.PC機中的擴展ROM相當于一個電子盤,如果在其中寫入引導程序和應用程序,那么,即使計算機沒有硬盤和操作系統(tǒng),擴展ROM中的引導程序和應用程序也能夠控制計算機以實現(xiàn)某些特定的功能。如,無硬盤PC機用于工業(yè)控制或控制作業(yè)流程等。

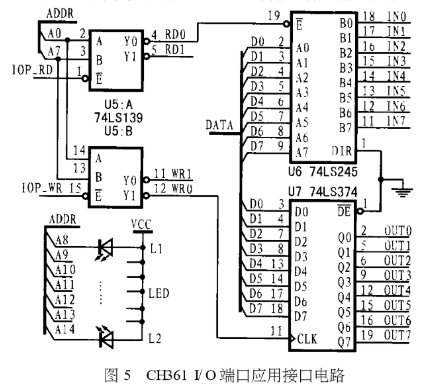

4.4 I/O端口應用

圖5是CH361 的應用接口電路。利用讀選通/使能IOP RD和寫選通/使能IOP WR可 控制74LS139的譯碼使能,然后由74LS139對地址進行譯碼即可輸出2路讀控制和2路寫控制,再經(jīng)74LS245輸入緩沖和74LS374鎖存輸出, 即可獲得2組每組8位緩沖輸入和2組每組8位鎖存輸出。如將CH361的I/O基址設定為5A00H,則讀取5A00H端口就是讀取第一組緩沖輸入,寫入5A01H端口就是寫入第二組鎖存輸出。如果CH361沒有連接擴展ROM或者存儲器,則空閑的地址線A14~A8以及A15便可直接作為輸出控制線.A15~A0地址設定寄存器在系統(tǒng)復位后為低電平,并且只能以字為單位進行讀寫。如要設定A13為高電平烝9為低電平熎淥位保持不變,則首先必須讀取該寄存器,然后將讀出數(shù)據(jù)中的位13置1、位9置0 ,最后再寫回該寄存器。圖5是一個簡單示例,CH361的輸入輸出信號與TTL/CMOS 兼容,因而可以連接ADC/DAC/MCU等芯片,由于其輸出引腳的驅(qū)動電流大于10mA,因而可以在串接限流電阻后驅(qū)動LED.此外,CH361還提供了8根地址線A7~A0以可用于I/O地址譯碼,但由于偏移地址0FFH至0F0H范圍為專用功能寄存器的地址,所以I/O地址譯碼只對偏移地址0EFH至00H范圍有效,且長度不應超過240字節(jié)。一般情況下,如果使用的I/O端口長度不超過128字節(jié),則可使用A7作為外部電路的片選線。而當偏移地址為7FH至00H范圍時,A7就可以輸出低電平有效的片選信號,如果偏移地址超過80H,A7將輸出高電平,此時,I/O端口的片選信號無效。

責任編輯:gt

-

芯片

+關注

關注

453文章

50399瀏覽量

421800 -

存儲器

+關注

關注

38文章

7452瀏覽量

163605 -

pci總線

+關注

關注

1文章

203瀏覽量

31794

發(fā)布評論請先 登錄

相關推薦

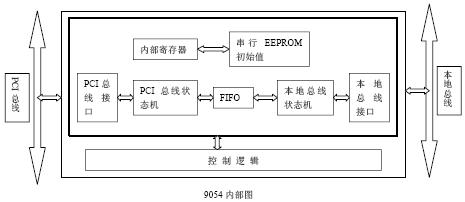

PCI總線接口芯片9054及其應用

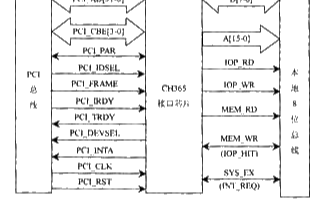

PCI 總線接口芯片CH365

采用CH365芯片實現(xiàn)PCI總線接口卡設計

基于FPGA的PCI總線接口設計

基于FPGA的PCI總線接口設計

采用CH365通用PCI接口芯片實現(xiàn)接口電路的軟硬件設計

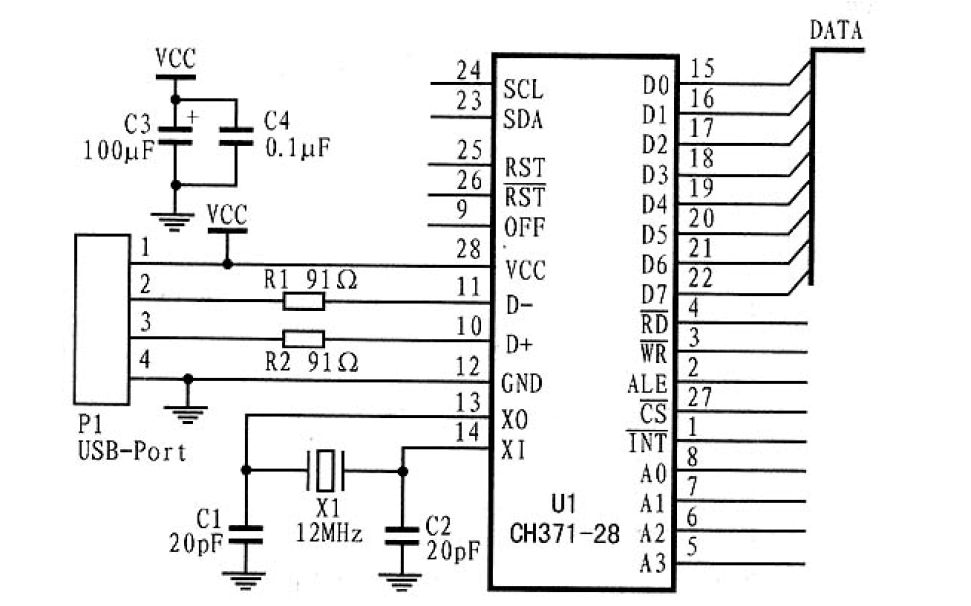

USB總線接口芯片CH371及其應用

PCI總線接口芯片CH365技術(shù)手冊

PCI總線通用接口芯片CH361的功能特點、引腳功能和典型應用

PCI總線通用接口芯片CH361的功能特點、引腳功能和典型應用

評論