近年來,紅外探測系統因其具有隱蔽性,抗干擾性,全天候工作等特點,在現代戰爭中具有重要的作用,而紅外圖像中小目標的檢測將直接影響制導系統的有效作用距離及設備的復雜程度,在紅外成像制導和預警系統中發揮著舉足輕重的作用。研究紅外輻射的產生、傳播、轉化、測量及其應用的技術科學。通常人們將其劃分為近、點擊此處添加圖片說明中、遠紅外三部分。近紅外指波長為0.75~3.0微米;中紅外指波長為3.0~20微米;遠紅外則指波長為20~1000微米。在光譜學中,波段的劃分方法尚不統一,也有人將0.75~3.0微米、3.0~40微米和40~1000微米作為近紅外、中紅外和遠紅外波段。另外,由于大氣對紅外輻射的吸收,只留下三個重要的"窗口"區,即1~3微米、3~5微米和8~13微米可讓紅外輻射通過,因而在軍事應用上,又分別將這三個波段稱為近紅外、中紅外和遠紅外。

一般說來,由于小目標距離較遠,因而在成像系統中表現為微弱特性,并且沒有形狀和結構特征或特征不明顯。同時,由于高于絕對零度的物體均有紅外輻射能力,所以自然界中的干擾源很多,很難準確地檢測出真正的目標。

本文在數學形態學Top-hat算子對于目標檢測的基礎上,設計了一種基于DSP+FPGA的圖像實時處理系統,使其能夠滿足高速采樣數據流快速存取,快速運算的要求。

1 算法基礎

1.1 形態學算法

數學形態學(Mathematical Morphology)誕生于1964年,是由法國巴黎礦業學院博士生賽拉(J. Serra)和導師馬瑟榮,在從事鐵礦核的定量巖石學分析及預測其開采價值的研究中提出"擊中/擊不中變換", 并在理論層面上第一次引入了形態學的表達式,建立了顆粒分析方法。他們的工作奠定了這門學科的理論基礎, 如擊中/擊不中變換、開閉運算、布爾模型及紋理分析器的原型等。數學形態學的基本思想是用具有一定形態的結構元素去量度和提取圖像中的對應形狀以達到對圖像分析和識別的目的。數學形態學方法是一種非線性濾波方法,它最先被用來處理二值圖像,后來被引用到灰度圖像處理。基本思想是:用一定的結構元素去度量和提取圖像中的對應形狀,去除不相干的結構,以達到圖像分析和目標識別的目的。

灰度形態學的基本運算有膨脹、腐蝕、開運算和閉運算。基于這些運算,可以推導和組合各種數學形態學使用算法。

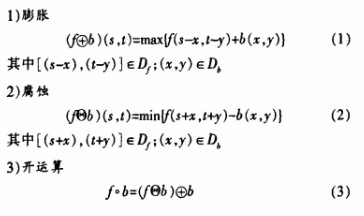

設f(x,y)為輸入圖像,b(x,y)為結構元素,其中(x,y)為圖像平面空間的坐標點,f為(x,y)點的灰度值,b為(x,y)點的結構函數值,Df和Db分別是f和b的定義域,上述4種基本運算的表達式為:

其中,開運算有些像非線性低通濾波器,但是又與低通濾波器不同,開運算可以允許高頻部分中大于結構元素的部分通過。Top-hat算子就是利用了開運算的上述性質來進行目標檢測的。

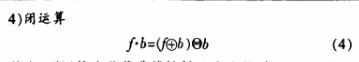

Top-hat算子的定義為:

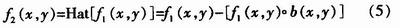

經過Top-hat處理后的圖像,目標和背景在能量上差別較大,大部分像素都集中在低灰度區,只有目標和小部分噪聲分布在高亮度區,如圖1所示,圖1(a)為原始圖像,圖1(b)為經過Top-hat處理的圖像及其直方圖統計結果。

1.2 最大類間方差法求閾值

閾值就是臨界值,在PS中的閾值,實際上是基于圖片亮度的一個黑白分界值,默認值是50%中性灰,既128,亮度高于128(<50%的灰)白既會變白,低于128(>50%的灰)的既會變黑。[可以跟濾鏡中的其它――高反差保留,再用閾值效果會更好。]

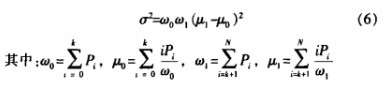

設經過處理后的圖像f2(x,y)的各灰度的集合為S={0,1,2,…,N},Pi為此集合中i出現的概率,由于圖像是由小目標和背景兩部分組成的,設這兩部分對應的灰度子集分別為:紅外背景,C0={0,1,2,…,k};目標對象,C1={k+1,k+2,…,N};則兩個類別的間方差為:

為節約程序運行時間,選取k的取值范圍為[μ+5σ…N],其中μ為整幅圖像的均值,σ為整幅圖像的平均差,直到找到使類間方差取最大值時的k值,即為最佳分割閾值th.

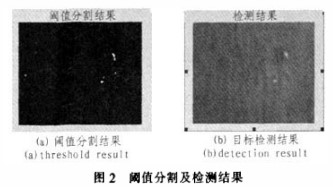

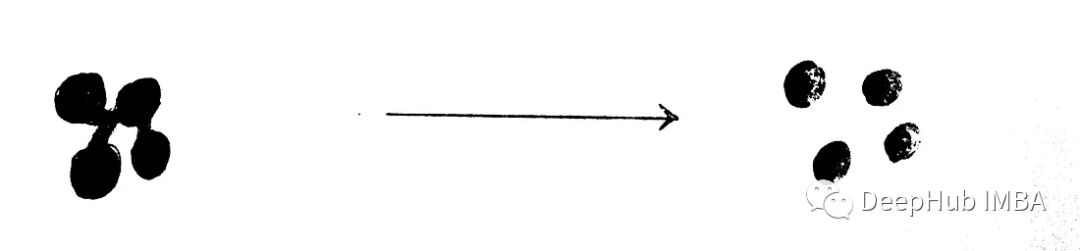

對經過Top-hat處理后的圖像,利用上述的最大類間方差法獲取閾值,利用這個閾值對圖像進行分割,最后通過判斷目標的形狀大小,以達到提取目標的效果,如圖2所示,圖2(a)為閾值分割的結果,圖2(b)為最終判斷結果。

2 硬件系統結構

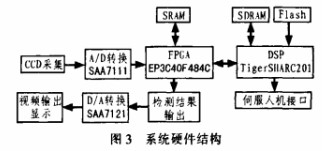

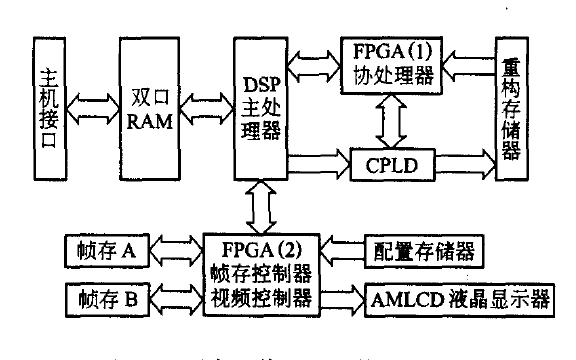

在實時視頻處理系統中,底層算法的數據量大,運算結構相對比較簡單,對速度有很高的要求,而高層處理算法控制結構復雜,數據量較底層算法少,故本文采用FPGA+DSP的結構。利用DSP實現目標檢測的算法,數字信號處理(Digital Signal Processing,簡稱DSP)是一門涉及許多學科而又廣泛應用于許多領域的新興學科。20世紀60年代以來,隨著計算機和信息技術的飛速發展,數字信號處理技術應運而生并得到迅速的發展。數字信號處理是一種通過使用數學技巧執行轉換或提取信息,來處理現實信號的方法,這些信號由數字序列表示。在過去的二十多年時間里,數字信號處理已經在通信等領域得到極為廣泛的應用,可以提高運行速度及便于調試和修改,FPGA實現整個系統的控制和圖像的基本預處理功能。整個系統的硬件結構如圖3所示。

在系統設計中,DSP采用ADI公司通用浮點型TigerSHARC201,它擁有非常高的存儲寬度,支持32位和擴展的40位浮點運算,支持8、16、32、64位定點運算。它擁有高達600 MHz的內核時鐘速率,一個周期可以執行4條指令,相當于24次16 bit定點操作或者6次浮點操作。處理器的運算流水是雙周期的,分支流水為2~6周期,鑒于此流水深度,它使用分支目標緩沖(BTB)來減少分支延遲,其兩個相同的計算單元均支持浮點和定點運算。

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。FPGA采用Altera公司的EP3C40F484C對視頻信號進行預處理和整個系統的時序控制,它具有多達24 624個邏輯單元,具有129個兼容的LV-DS通道,每個通道數據率高達640 Mb/s,還有4個可編程鎖相環和8個全局時鐘線。另外此芯片的功耗較低,全局運行時總功耗為300 mW左右。

2.1 視頻輸入和輸出模塊

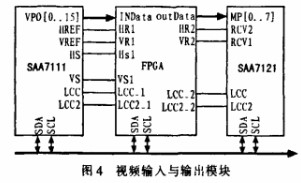

采用解碼器SAA7111將攝像頭輸出的模擬視頻信號轉換為數字信號。編碼器(encoder),是一種輸入模擬視頻信號并將它轉換為數字信號格式,以進一步壓縮和傳輸的硬件/軟件設備。像視頻的mpeg4,音頻的mp3,ac3,dts等,這些編碼器可以將原始數據壓縮存放,剛才都是常用的編碼格式,還有些專業的編碼格式,一般家庭基本不會用到。為了在家用設備或者電腦上重放這些視頻和音頻則需要用到解碼軟件,一般稱為插件。解碼器是一個重要前端控制設備。在主機的控制下,可使前端設備產生相應的動作。解碼器,國外稱其為接收器/驅動器(Receiver/Driver)或遙控設備(Telemetry),是為帶有云臺、變焦鏡頭等可控設備提供驅動電源并與控制設備如矩陣進 解碼器(Decoder)

行通訊的前端設備。通過配置SAA7111將PAL制式的模擬基帶信號轉化為CCIR-656格式的UYVY信號,并將其送入FPGA中,進行預處理。具體連接如圖4所示,VPO[0…7]沒有數據輸入,VPO[8…15]是數據輸出管腳與FPGA相連,時鐘同步信號TS201采用MDMA的方式將原始圖像信號存入SDRAM中,供目標檢測算法使用。視頻輸出模塊采用視頻編碼器SAA7121,標準的UYVY數據從FPGA的引腳輸出,送到SAA7121的數據引腳,場、行同步信號分別接到FPGA的控制引腳上,通過行、場信號的控制,就能夠輸出顯示正確的視頻圖像。在SAA7111和SAA7121工作之前,都需要對這兩個芯片進行配置,它們的配置的參數都是通過FPGA產生I2C總線來實現的。

2.2 存儲模塊

TS201的片上存儲器分為兩個部分:每個內核各使用100 KB的專用、高速L1存儲器;128 KB的大容量共享L2存儲器。通過EBIU接口外擴SDRAM和Flash兩種存儲器。選取2片MT48L32M16A2來構成SDRAM存儲器,圖像處理數據和圖像處理中間結果可存儲在SDRAM中。系統擴展64 MB的Flash,選用S29GL064M90T,主要存放DSP內核程序。

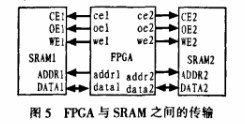

FPGA的存儲系統:選取2片IS61LV10248來構成SRAM存儲器,主要用于存儲從SAA7111傳輸到FPGA的數據,根據視頻數據的奇偶場的關系,在數據的存取過程中采用乒乓存取方式,當SRAM1存儲數據的時候,FPGA從SRAM2讀取數據,傳給SAA7121做為顯示使用,當SRAM2存儲數據的時候,FPGA從SRAM1讀取數據,傳給SAA7121做為顯示使用,同時通過對讀時鐘和讀范圍的控制,可以控制圖像的現實范圍和現實方式。具體硬件連接結構如圖5所示。

2.3 DSP雙核以及FPGA之間的通信

在本系統中,涉及到TS201兩個核之間的通信以及TS201與FPGA之間的通信。FPGA給DSP提供預處理之后的圖像數據,DSP根據提供的圖像數據進行目標檢測算法,并將檢測之后的坐標數據傳輸到FPGA,FPGA將坐標信息疊加到原始圖像后送給SAA7121顯示。常見的雙核通信主要采用中斷、輪詢兩種通信方式。中斷是利用兩個核的中斷機制來實現FPGA與DSP之間的通信;輪詢是通過在雙核的共享寄存器里設置一些信號量,供雙核通信與訪問。考慮到本系統的應用條件,采用輪詢的通信方式,DSP的異步存儲器的地址空間映射到FPGA,通過FPGA操作數據線和地址線,即可完成FPGA與DSP之間的數據交互。

2.4 系統工作流程

整個系統的工作流程為:由CCD采集視頻模擬信號,經過可編程視頻解碼處理器SAA7111解碼后輸出場同步、行同步、像素時鐘和位寬為16 bit的數字圖像信號,并將信號送入FPGA中,在FPGA中對送來的數據做緩存,預處理,再通過與TS201連接的雙向LINKPORT,把圖像數據實時地導入DSP中,在DSP中運行檢測算法,得到被檢測目標的正確坐標,DSP把目標的坐標信息返回到FPGA中,FPGA根據坐標信息在原始圖像上標示出目標的位置,最后將處理后的圖像信號傳給可編程視頻編碼器SAA7121進行編碼實現D/A轉換,輸出模擬視頻,并把檢測結果顯示在視頻顯示設備上。

3 結論

首先研究了形態學Top-hat算子,并利用Top-hat算子進行背景抑制,同時,采用最大類間方差法獲得圖像的閾值,分割背景和目標,實現小目標檢測,通過仿真實驗發現,這種方法能夠在一定程度上減少實際檢測中的虛警率,增加目標檢測的準確性。

利用DSP+FPGA的系統架構設計了實現算法的硬件平臺,這種結構在一定程度上可以滿足實時性和靈活性的要求,具有很強的通用性和可擴展性。并在設計中采用了模塊化設計,這樣的設計便于集中控制,能夠節省程序運行時間。

-

處理器

+關注

關注

68文章

19178瀏覽量

229198 -

dsp

+關注

關注

552文章

7962瀏覽量

348305 -

FPGA

+關注

關注

1626文章

21678瀏覽量

602001

發布評論請先 登錄

相關推薦

在數學形態學基礎上實現DSP和FPGA的紅外圖像檢測系統

在數學形態學基礎上實現DSP和FPGA的紅外圖像檢測系統

評論