一、軟件介紹

本系統采用了LATTICE的XP系列芯片,所用軟件為splever7.0,應用本軟件有一個新加功能,可以用FPGA的底層資源生成一個簡單CPU的框架,并且在軟件的庫里邊,有很多的模塊可以調用,例如GPIO接口,I2C接口等。本系統的設計使用的是I2C接口。

二、系統構成

圖1 系統框圖

本系統(系統框圖如圖1)是采用FPGA進行實時運算。從cmos傳感器出來的數字信號首先經過白平衡處理模塊,在這個模塊中,需要對圖象中的R、G、B的分量分別進行計算,求出他們各自的均值。一般情況下,只有當他們各自的均值為128或者129的時候,我們可以認為圖象達到了白平衡的狀態,當然有一個前提就是要對一個白色的背景取圖。如果他們的均值不相等,或者沒有達到128或者129的值時,給I2C模塊一個信號,使之對傳感器的顏色分量寄存器進行設置,直到完全為我們所期待的數值為止。

三、部分程序和接口

module send( reset_n,

clk,

vsync,

href,

data_in,

data_out);

input reset_n;

//系統復位信號

input clk;

//系統時鐘

input vsync;

//廠信號

input href;

//行信號

input [9:0]data_in;

//圖象數據

output [29:0]data_out;//色彩分量均值

reg [25:0]count_r;

always@(negedge clk or posedge posevsync)begin

if(posevsync)

count_r 《= 26‘h00000000;

else begin

if(hs_count》=10’d129&&hs_count《=10‘d640)

begin

if((pixcount》=11’d384&&pixcount《=11‘d895)&&row_odd_href)

begin

if(!row_odd_pix)

count_r 《= count_r + data_in;

else

count_r 《= count_r;

end

else

count_r 《= count_r;

end

else

count_r 《= count_r;

end

end

reg [26:0]count_g;

always@(negedge clk or posedge posevsync)begin

if(posevsync)

count_g 《= 27’h00000000;

else begin

if(hs_count》=10‘d129&&hs_count《=10’d640)

begin

if(pixcount》=11‘d384&&pixcount《=11’d895)

begin

if(row_odd_href)

begin

if(row_odd_pix)

count_g 《= count_g + data_in;

else

count_g 《= count_g;

end

else begin

if(!row_odd_pix)

count_g 《= count_g + data_in;

else

count_g 《= count_g;

end

end

else

count_g 《= count_g;

end

else

count_g 《= count_g;

end

end

reg [25:0]count_b;

always@(negedge clk or posedge posevsync)begin

if(posevsync)

count_b 《= 26‘h00000000;

else begin

if(hs_count》=10’d129&&hs_count《=10‘d640)

begin

if((pixcount》=11’d384&&pixcount《=11‘d895)&&(!row_odd_href))

begin

if(row_odd_pix)

count_b 《= count_b + data_in;

else

count_b 《= count_b;

end

else

count_b 《= count_b;

end

else

count_b 《= count_b;

end

end

reg [29:0]data_out;

always@(negedge vsync or negedge reset_n)begin

if(!reset_n)

data_out 《= 30’h0000000000;

else

data_out

《= {count_r[25:16], count_g[26:17], count_b[25:16]};

end

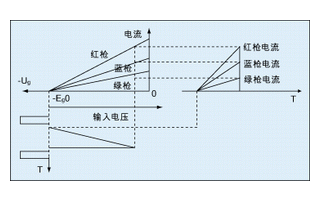

四、仿真圖形

系統的總體仿真圖如圖2

圖2 系統仿真圖

五、結論

采用FPGA對自動白平衡進行運算的一個最大的優點就是所有的操作都是實時進行,不需要先緩存一整張圖象,所以中間沒有延時,不僅運算速度快,而且圖像的相質還可以得到很好的改良。

責任編輯:gt

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601897 -

芯片

+關注

關注

454文章

50430瀏覽量

421866 -

I2C

+關注

關注

28文章

1481瀏覽量

123304

發布評論請先 登錄

相關推薦

白平衡自動測量調整儀的工作原理實現設計

USB總線轉I2C總線接口芯片

i2c接口轉串口芯片

I2C總線通信接口的CPLD實現

I2C總線在MCS51系列單片機數據采集系統中的實現

基于EasyFPGA030的I2C總線接口模塊

基于CPLD的I2C總線接口設計

采用LATTICE的XP系列芯片實現FPGA的自動白平衡系統的設計

I2C接口配置ES7243錄音芯片,MCU(STM32)收不到I2C ACK的問題

采用LATTICE XP系列芯片和I2C接口實現自動白平衡的FPGA

采用LATTICE XP系列芯片和I2C接口實現自動白平衡的FPGA

評論