本文中我們將重點放在這些經(jīng)驗豐富的專家是如何使用超低功耗的復(fù)雜可編程邏輯器件(CPLD),并從他們的嵌入式設(shè)計中的I/O子系統(tǒng)節(jié)省每個微瓦的方法。

從事便攜式或手持產(chǎn)品設(shè)計的工程師都明白對于如今的設(shè)計,最大限度地降低功耗是必不可少的要求。但是,只有經(jīng)驗豐富的工程師理解盡可能地延長系統(tǒng)的電池壽命的那些微妙但又重要的細(xì)節(jié)。

我們首先來了解在嵌入式設(shè)計中如何降低CPLD的功耗、電路板的面積和元器件成本。下一步,我們將看到在待機模式下如何盡量降低CPLD的功耗,不僅要仔細(xì)地選擇器件,而且還要選擇一個合適的總線駐留方案。器件工作期間,我們對節(jié)省功耗的探討將包括選擇邏輯門、智能I/O設(shè)計和精密的電源電壓管理技術(shù)。

嵌入式工程師青睞的器件CPLD

盡管在最先進(jìn)的新興應(yīng)用中它們特別受歡迎,CPLD的成本低,體積小和低功耗的特性使他們成為幾乎所有的手持式或便攜式設(shè)計的首選。在這些應(yīng)用中,它們常用來整合邏輯功能,擴展主處理器的I/O功能和監(jiān)控關(guān)鍵的輸入,從而使處理器有更多的時間處于低功耗睡眠模式。

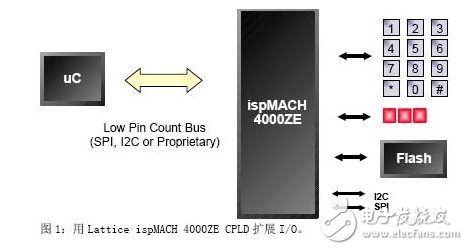

用作I/O的擴展器件時,像ispMACH 4000ZE這樣的CPLD器件(圖1)給予簡單的嵌入式處理器額外的信號線和處理功能,他們能夠支持顯示器、按鈕、發(fā)光二極管,串行或并行I/O,或 存儲 接口。設(shè)計人員還經(jīng)常利用它們作為設(shè)計中通用處理器和更多的專業(yè)芯片組之間的緩沖,還能用于其他的應(yīng)用,如智能手機、GPS系統(tǒng),遠(yuǎn)程工業(yè)傳感器和數(shù)碼攝像機。

圖1:用LattICe ispMACH 4000ZE CPLD擴展I/O.

待機功耗的基本知識

掌握CPLD功耗的第一步是了解器件在工作時的情況和待機(也稱為靜態(tài))時的狀態(tài)。由于許多CPLD在大部分時間是處于待機狀態(tài),我們首先會仔細(xì)考察這個經(jīng)常被誤解的模式。

加電壓至器件輸入部分,但其內(nèi)部邏輯還沒有被時鐘控制,此時CPLD是處于待機狀態(tài)。在此狀態(tài)下,因為它的泄漏和偏置電流(雖然大大低于實際的操作),CPLD仍然有一些功耗。泄漏電流隨溫度、工作電壓和制造工藝而變化。

負(fù)載產(chǎn)生了可編程邏輯器件內(nèi)的偏置電流,如內(nèi)部振蕩器、I/O的上拉/下拉電路和其他固定開銷,而不管器件的邏輯功能是否正在使用。與泄漏電流不一樣,在一定的溫度和電壓范圍內(nèi)偏置電流是相對穩(wěn)定的,它們可以用合適的內(nèi)部配置所控制。

用明智的方法管理泄漏電流

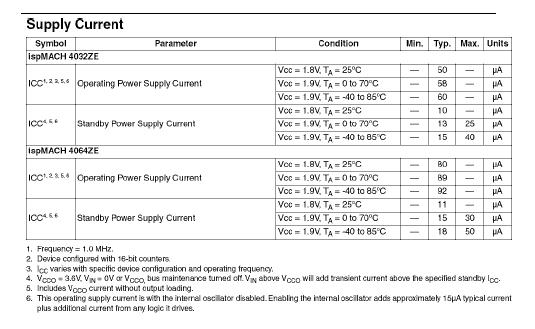

由于可編程邏輯器件的泄漏電流主要取決于它是怎樣制造的,第一步就是要密切關(guān)注候選器件制造商提供的數(shù)據(jù)手冊的規(guī)范。只是簡單地購買廣告所述的低功耗器件并不能保證如你期望設(shè)計中達(dá)到的指標(biāo)完全一樣。經(jīng)驗豐富的設(shè)計師明白尋找“典型”和“最大”電流之間的實際關(guān)系需要根據(jù)具體的應(yīng)用(圖2)做出解釋。在許多應(yīng)用中,數(shù)據(jù)手冊中列出的所謂典型電流中提供了一個非常有用的CPLD汲取電流的近似值。然而,有幾個問題需要加以探討,以確保對設(shè)計的估計和實際功耗保持相對接近。

圖2:供給電流規(guī)范

首先需要考慮的事項是CPLD占整個系統(tǒng)功耗的比例。如果這是一小部分,比如說5%~10%,即使最壞的情況將引起整個功耗有相對較小的變化。如果CPLD需要20%或以上的功耗預(yù)算,也許是開始根據(jù)額定待機電流考慮偏置設(shè)計的時候了,額定待機電流接近數(shù)據(jù)手冊中列出的最大電流。您還應(yīng)該考慮設(shè)計中CPLD(以及其他器件)的數(shù)量。由于電路板上元器件數(shù)量的增加,總功耗接近總的典型額定電流的概率也隨之增加。最后,如果您的產(chǎn)品以驅(qū)動它至最壞情況的功耗級別為目標(biāo),那么您需要考慮潛在影響:較高的功耗會縮短產(chǎn)品的壽命嗎?它是否會成為火災(zāi)的隱患?

如果您仔細(xì)察看圖2中的數(shù)據(jù),你可能注意到,待機功耗還根據(jù)工作溫度和VCC(電源電壓)而變化。這是因為CPLD的漏電流會隨溫度升高而增加。事實上,使您的設(shè)計完美將改善其待機功耗。由于漏電流與Vcc密切相關(guān),保持電源電壓盡可能的低可以節(jié)省更多的功耗。由于仔細(xì)的電源電壓管理能夠節(jié)省更多的動態(tài)功耗,在涉及運作功耗管理時,我們會對這個方面進(jìn)行探討。

設(shè)置偏置電流

通過選擇合適的器件可以控制CPLD的泄漏電流,現(xiàn)在到了運用你的工程技能調(diào)整偏置電流的時候了。用來管理偏置電流的技術(shù)大致分為兩種類型:

確保CPLD的待機配置不與上拉/下拉或相關(guān)的其他器件所用的總線駐留技術(shù)相沖突;動態(tài)控制內(nèi)部功能塊(如振蕩器),使他們只開啟所需要的部分。具體取決于所使用的CPLD,這是增加更多的待機時間到設(shè)計中的好方法。

并行駐留101方案

在許多設(shè)計中,嵌入式主處理器可以使用自己的總線駐留方案,以保持在總線或I/O上所需的邏輯電平,所以你只須為CPLD的待機模式做準(zhǔn)備,確保其激活總線的管理功能被禁用。在其他應(yīng)用中,總線上其他地方的上拉或下拉電路也可以緩解在待機期間CPLD必須管理總線的情況。

但是,不需要CPLD做任何事情并不意味著你也不需要做任何事情。花些時間驗證只有一個設(shè)備驅(qū)動總線是一個重要的任務(wù),因為單個引腳上的邏輯沖突可導(dǎo)致待機功耗為整個芯片標(biāo)稱值10uA 閑置功耗的2~15倍。

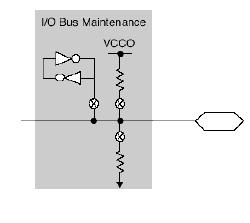

在主總線駐留機制無法使用情況下,可以使用上拉/下拉,以及在大多數(shù)現(xiàn)代的CPLD中擁有的總線保持功能。如同大多數(shù)同類器件,萊迪思的ispMACH 4000ZE CPLD的I/O引腳都配備了可選的上拉和下拉電阻,在待機狀態(tài)(圖3)可提供合適的邏輯電平。4000ZE系列還配備了節(jié)省功耗的總線保持功能(也稱為總線保持):一種弱激活驅(qū)動電路可設(shè)置為激活或零,同時產(chǎn)生比簡單的電阻器消耗小得多的功耗。一點忠告:雖然總線保持功能可大大節(jié)省功耗,但必須肯定它是唯一的在線有源器件,否則會有吸入大電流的風(fēng)險。

圖3:CPLD的總線管理選擇

動態(tài)功耗管理

設(shè)計人員需要關(guān)注兩種類型的動態(tài)功耗。運行功耗預(yù)算的第一部分是CPLD需要實際工作時的那部分。管理策略的其他部分涉及關(guān)掉輸入至此刻不需要的CPLD的部分,阻止它們切換,或在可能的情況下將它們?nèi)筷P(guān)閉。

精密的電源管理

雖然CPLD邏輯的許多部分很可能被連續(xù)使用,在有意義的時間段內(nèi)不能禁用,因此使用低電源電壓仍然可以節(jié)省功耗。由于功耗是電壓平方的函數(shù),用1%的精確開關(guān)穩(wěn)壓器,可讓設(shè)計運行于CPLD工作范圍的下限,您可以節(jié)省相當(dāng)多的功耗。例如,如果一個標(biāo)稱值為1.8V的CPLD工作在1.65V,它大約少消耗30%的功耗,這還不包括在較低VCC的情況下泄漏電流的減少。

選擇邏輯門

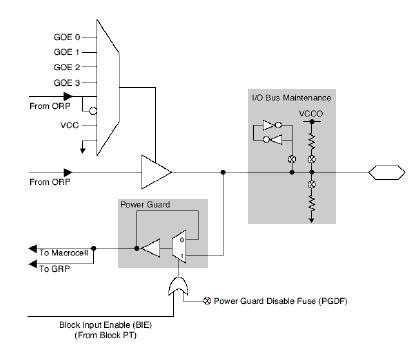

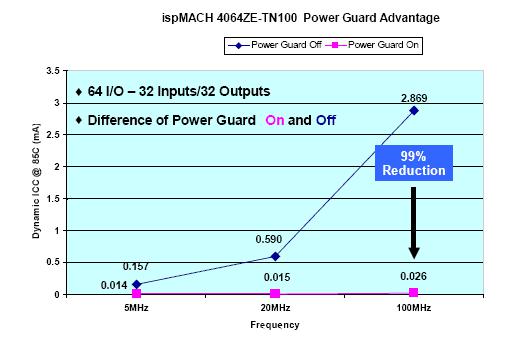

如同大多數(shù)的CPLD,ispMACH 4000ZE具有一個功能(萊迪思稱為“Power Guard” 功耗衛(wèi)士),當(dāng)它們不需要相關(guān)的邏輯時,可禁用單獨的輸入。主機處理器、其他的外部邏輯,或CPLD的其他部分可以使用器件的塊輸入使能線,以保持CPLD的邏輯選定的塊被時鐘控制(圖4)。例如,如果CPLD的某個部分被用作解碼器電路,只有該功能正在使用時,主處理器可以使它能工作,使之能夠在其余的時間保持休眠狀態(tài)。

圖4:Power Guard電路

根據(jù)實際的應(yīng)用使用LattICe的Power Guard或其他方法來禁用時鐘至選定的CPLD的輸入引腳,這樣可以大大降低動態(tài)功耗。尤其是如果邏輯信號的時鐘頻率超過30兆赫時,這些方法特別有用。圖5說明了可以用選擇邏輯時鐘技術(shù)實現(xiàn)潛在的節(jié)省功耗的方法。

圖5:Power Guard 節(jié)省的功耗

針對低功耗的I/O設(shè)計

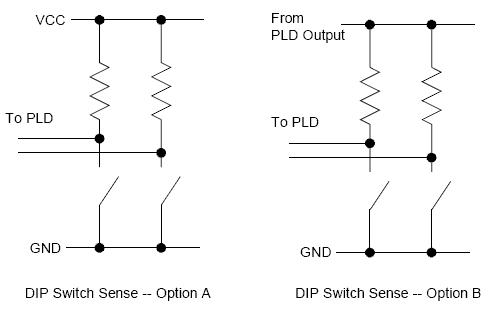

除了使用已經(jīng)闡述的技術(shù),目前大部分項目給予精明的工程師更多節(jié)省多余的微瓦功耗的機會-如果他們愿意關(guān)注潛伏在許多設(shè)計中的微小能源汲取部分。一個好的例子是無處不在的為開關(guān)提供讀出電壓的上拉電阻,以及連接到CPLD的輸入線(圖6)。通過使用CPLD的輸出,或其他控制線至電源電壓到讀出線,只有當(dāng)他們被讀取時,并且讀出線接地時,設(shè)計人員方可去除這個小而穩(wěn)定的電流。

圖6:無源和有源功率開關(guān)讀出線

其他提示

配置可編程邏輯器件的JTAG接口引腳為浮動狀態(tài),以避免漏電流。保持VCCO的I / O電平高于VCC.越接近這個電壓,吸收的電流越多。在可能的情況下,使用轉(zhuǎn)換率慢的I/O.

結(jié)語

大多數(shù)基于CPLD設(shè)計至少包括一些未引起注意的角落,在這些地方潛伏著耗能大戶,他們悄悄地汲取電池的能量。幸運的是,認(rèn)真實施一些重要的原則可以制止這些討厭的寄生部分。當(dāng)選擇CPLD和其他元件時,注意其靜態(tài)和動態(tài)功耗等級:他們隨供電電壓、溫度和工作頻率而變化。同樣要注意“最小”、“最大”和“典型”功耗指標(biāo),它們將影響你的設(shè)計。盡量減少CPLD的偏置電流,確保其待機配置不與其他與之相連的器件相沖突,關(guān)閉任何不必要的內(nèi)部功能。

-

電源

+關(guān)注

關(guān)注

184文章

17605瀏覽量

249560 -

cpld

+關(guān)注

關(guān)注

32文章

1247瀏覽量

169226 -

嵌入式

+關(guān)注

關(guān)注

5072文章

19026瀏覽量

303516

發(fā)布評論請先 登錄

相關(guān)推薦

嵌入式系統(tǒng)中的低功耗設(shè)計

基于嵌入式DSP系統(tǒng)的低功耗優(yōu)化設(shè)計

怎么才能在嵌入式設(shè)計中降低CPLD的功耗?

怎么降低嵌入式芯片的功耗?

嵌入式手持終端電源管理系統(tǒng)有什么功能?

嵌入式設(shè)計降低硬件功耗的方法

在嵌入式Linux平臺下的功耗管理技術(shù)

嵌入式低功耗電源管理框架的設(shè)計資料分享

嵌入式系統(tǒng)中的電源管理是什么

什么是嵌入式技術(shù)

在嵌入式設(shè)計中降低CPLD的功耗

嵌入式系統(tǒng)設(shè)計中的低功耗技術(shù)

嵌入式linux功耗優(yōu)化,嵌入式Linux功耗管理技術(shù)設(shè)計與實現(xiàn)

在嵌入式設(shè)計中如何降低CPLD的功耗與電源電壓管理技術(shù)分析

在嵌入式設(shè)計中如何降低CPLD的功耗與電源電壓管理技術(shù)分析

評論