隨著芯片技術的發展,FPGA的容量已經達到上百萬門級,從而使FPGA成為設計的選擇之一。Altera公司的FPGA芯片EPXA10應用SOPC技術,集高密度邏輯(FPGA)、存儲器(SRAM)及嵌入式處理器(ARM)于單片可編程邏輯器件上,實現了RISC和FPGA的完美結合。本文使用EPXA10芯片,利用片上的ARM微處理器對MPEG-2傳輸流進行解碼,得到必要的解碼參數,實現了將傳輸流分成視頻流和音頻流的解復用。

EPAX10器件簡要介紹

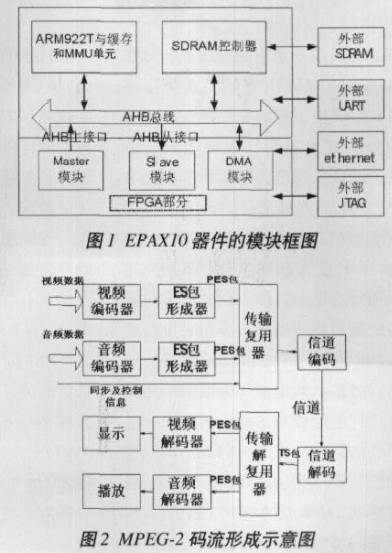

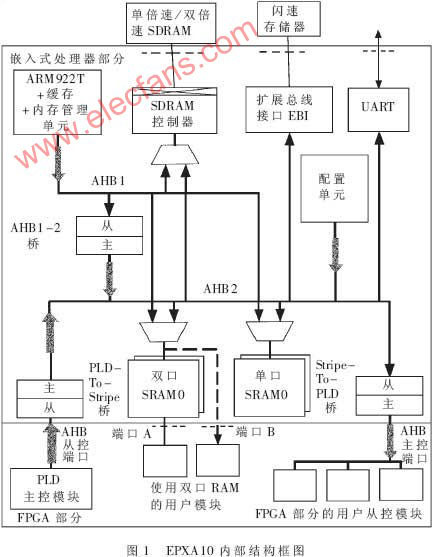

ALTERA公司的EPXA10器件單片集成了ARM硬核,百萬門級的FPGA,以及SDRAM存儲器的接口。它將FPGA和ARM處理器完美結合在一起,是一個典型的SOPC結構。

其中ARM處理器是32位的ARM922T,工作頻率可以達到200MHz,具有8K的數據緩存和8K的指令緩存。通過板上的JTAG接口,可以實現斷點調試功能。

片上的百萬門級FPGA可用于實現用戶自定義的邏輯。它通過AHB總線和ARM處理器相互連接。為了更加靈活的使用,FPGA用戶自定義邏輯可以定義為主模塊(master),在總線通信時處于發起端;或是定義為從模塊(slave),在總線通信時處于接收端。FPGA器件內部有3M大小的存儲器,同時集成了SDRAM控制器。在FPGA開發板上可以外接128M的SDRAM,為了便于內部FPGA和外部SDRAM大數據量的交換,用戶還可以定義自己的DMA模塊,用于訪問外部SDRAM。通過UART、網卡接口、JTAG接口,FPGA可以很方便地同外部計算機通信、下載程序,及調試程序等。

MPEG-2傳輸流解復用原理

MPEG-2傳輸流簡要介紹

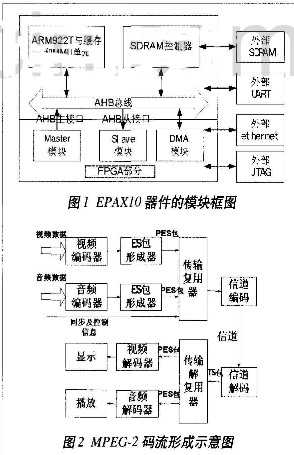

作為數字視頻壓縮技術的國際通用標準,MPEG-2標準于1994年被運動圖像專家組制定出來,分成系統層、視頻壓縮層和音頻壓縮層。系統層主要用來描述音、視頻的數據復用和音、視頻的同步方式。在系統層定義了TS(傳輸流)和PS(節目流)兩種形式的碼流。PS通常用于相對無錯的環境,例如DVD中,其長度為2048字節;TS通常用于相對有錯的環境,例如數字電視的地面廣播傳輸中,分組長度規定為188字節。TS流和PS流都是由編碼后的基本數據流(ES)根據一定的格式打包形成PES包,再加入一些系統信息而構成的,碼流形成過程如圖2所示。根據MPEG-2協議,在發送端,基本流的PES打包由音/視頻編碼器完成,復用器接收編碼端的音、視頻數據流以及輔助數據流,按照一定的復用方法將其交織成為單一的TS流。為了實現音、視頻同步,在碼流中還必須加入各種時間的標志和系統的控制信息。接收端和發送端正好相反。

傳輸流及其PSI表

傳輸流TS的結構長度為188字節,分成包頭和包負荷兩部分。包頭主要包括同步字節和PID以及其他的信息,同步字節用來指示一個TS包開始(0x47),PID表示TS包的類型。例如一個節目里的音頻PES包,在轉換成為TS包后會具備同樣的PID,這樣,接收端只需要接收具有此PID的TS包,就可以將該節目的音頻解出來了。包負荷是包的實際內容,根據具體情況,可以放置PES包或PSI包。傳輸流由一個或者多個節目構成,而每一個節目由視頻流、音頻流、私有信息流以及其他的數據包構成。

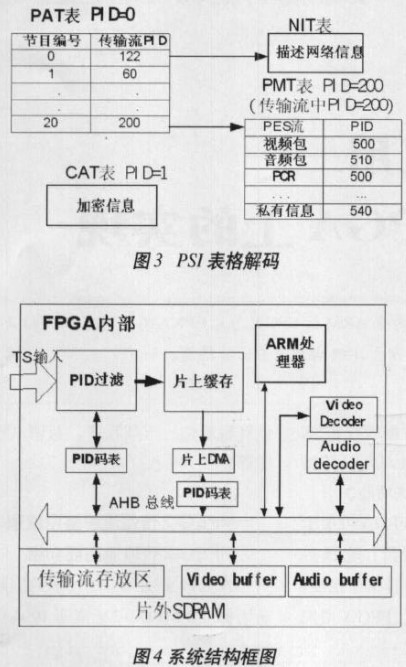

PSI包在傳輸流解復用中占據重要地位,它通過四個表格來定義碼流的結構,分別是節目關聯表(PAT)、節目映射表(PMT)、條件接收表(CAT)和網絡信息表(NIT)。其中最為關鍵的部分是PAT表和PMT表。

PAT表是PSI信息的索引表,PID值固定為0。在PAT表中列出了該傳輸碼流中所有節目的PMT表的PID值。如果接收方希望接收其中的一個節目,即可根據這個PID值解出對應于該節目的PMT表,從中可以查詢到與該節目相關的所有音頻流、視頻流,以及私有信息的PID,在接收時就可以只接收具有這些PID值的包。

PAT表的PID值為0,根據PAT表可以得到各個節目對應的PID值,如節目0,PID=122,對應NIT網絡信息表;節目1,PID=60;節目20,PID=200等。如果希望看節目20,就根據200這個PID值得到節目20對應的PMT表,再進一步查到節目20的視頻、音頻及私有信息包對應的PID值,分別為500、510和540。解有這些PID值的傳輸包就可以解出音頻和視頻的PES包,最終解出音頻流和視頻流。CAT表的PID值固定為1,用來傳遞加密信息,不在本文的討論范圍內。

在MPEG-2系統層解碼時,需要由一個解復用器按照上述的原理對PSI表進行處理,同時將各個音、視頻基本流從傳輸流中分離出來,送入對應的解碼器中,所以解復用器在MPEG-2解碼中占據重要的地位。

解復用系統的具體實現

本文設計的是DVB的SDTV系統集成解碼芯片,視頻解碼最高支持MPEG-2的MP@ML,分辨率為720×576,實時解碼;音頻解碼滿足AC-3標準。

從前面的部分可知,解復用器需要承擔將數據分流的工作,所以數據處理量相當大,很多解復用器都采用DSP或者專用ASIC進行處理。本文中,有別與以往的結構,利用EPXA10的片上ARM處理器,以及片上內嵌的SDRAM控制器和DMA控制器的特性,來實現對MPEG-2的傳輸流進行解復用,同時由硬件完成對PID包過濾的任務。所有的數據分解過程都由系統軟件來完成,因此在數據處理方面更加靈活,保證了系統對于MPEG-2傳輸流解碼的靈活性,同時避免了語法上的不兼容。

系統硬件由PID過濾、片上緩存及DMA等構成;系統軟件部分由ARM實現。片外SDRAM用來存放數據。音/視頻解碼模塊使用硬件實現,在本文中不涉及到相關內容。

系統硬件的功能是:當外部的8位傳輸流數據輸入到FPGA上時,根據傳輸流包頭進行同步,并將同步好的數據送入到PID過濾器。如果在傳輸過程中有錯誤,也就是包頭中有sequence-error-code=1,就丟棄這個包;如果沒有,則檢查PID碼表的數據,如果在碼表中有這個PID值,那么就將這個傳輸流的包送入到FPGA的片上緩存中;否則就丟棄這個包。PID過濾器工作完成后,數據送入FPGA片上緩存部分,為了加快數據處理速度,使用DMA將緩存中的數據傳輸到片上SDRAM對應的傳輸流緩沖區。

如果片外SDRAM的傳輸流緩存中有未處理的包,則取出該包,判斷PID的值。如果PID=0,表示當前的包是PAT,那么就對該包進行解析,根據選定的節目號,確定需要解碼的PMT包的PID,再更新FPGA上PID碼表中PMT的PID,并將PMT的狀態位設定為需要解碼。

如果PID等于PID碼表中PMT包的PID,則判斷PMT的狀態位。如果不需要解碼,就丟棄這個包;如果需要解碼,則進入PMT包解析子程序,提取出該解碼對應的音、視頻傳輸流包的PID,將提取出的音、視頻傳輸流包的PID值對FPGA片上的PID碼表進行更新。

如果PID等于PID碼表中的音、視頻PID值,那么就進入到音/視頻處理程序,對音、視頻的傳輸流包進行解包,將解得的PES包的內容(就是實際的音、視頻流)通過DMA發送到片外SDRAM的音/視頻緩沖區中,供下一級的音/視頻解碼器完成解碼功能,最終完成MPEG-2碼流的解碼過程。

結語

本文使用了Altera公司的一款具有ARM硬核的FPGA器件EPXA10,提出了一種基于ARM微處理器的對MPEG-2的傳輸流進行解復用的解復用器設計方案。根據傳輸流的特點,使用硬件實現了數據量操作比較大的PID包過濾、DMA傳輸等任務,并利用ARM處理器完成較為復雜的PAT、PMT包的解包工作,同時也將音、視頻包解包,并將解出的音、視頻發送到片外SDRAM上的音/視頻緩沖區中。

最終設計的解復用器能對碼率最高為19 Mbps的傳輸流進行解復用,對系統層的數據和其他輔助數據進行解碼。解復用得出的視頻流和音頻流可供下一級的音/視頻模塊進行實時解碼。

責任編輯:gt

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601864 -

ARM

+關注

關注

134文章

9046瀏覽量

366822 -

微處理器

+關注

關注

11文章

2247瀏覽量

82318

發布評論請先 登錄

相關推薦

波分復用/解復用器知多少?

內嵌ARM核怎么進行解復用?

MPEG-2編碼復用器中的FPGA邏輯設計

MPEG-2編碼復用器中的FPGA邏輯設計

MPEG-2復用器PSI信息分析部分的FPGA實現

FPGA芯片EPXA10在圖像處理中的應用

基于FPGA器件EPXA10實現MPEG-2傳輸流解復用器的設計

基于FPGA器件EPXA10實現MPEG-2傳輸流解復用器的設計

評論