前言

計算機的并行接口一開始是作為打印機接口而設計的。隨著計算機周邊設備的不斷擴展,人們對提高計算機外設的數據采集速度的要求也越來越高。傳統的異步串行通訊方式雖然具有數據傳輸距離較遠的優勢,但是由于數據傳輸速度慢,會造成傳輸速率的瓶頸問題。所以在一些需要高速數據傳輸的場合,使用并行接口一直是一種比較理想的解決方法。

1、并口EPP模式介紹

1.1并行接口的種類

最初的PC機并口由8個單向輸出,5個位輸入和4位雙向(控制)線組成(SPP),如今為了適應擴展外圍設備的需要,并口已經發展出了多種工作模式。總共有標準并行接口(SPP)、簡單雙向接口(PS/2)、增強型并行接口(EPP)和擴展功能接口(ECP)模式和多模式接口(ECP+EPP)這幾種。EPP工作模式作為一個提供高性能并口連接的方法,仍與SPP兼容。EPP工作模式的優點概括如下:

1)8位數據線由原來SPP的單向改成了雙向,簡化了外圍電路的設計;

2)在一個ISA的周期可以完成一次數據的傳輸,大大加快了數據傳輸速率;

3)只需要對計算機發送一條簡單軟件指令,接口硬件就可以自動生成握手聯絡信號;

4)接口數據線可以分別定義為數據和地址,通過綜合使用nAstrb和nDstrb兩條控制線可以快速的實現數據向不同的設備傳輸;

5)相對ECP的工作模式,EPP具有操作簡單、易于實現的特點;

1.2 EPP的硬件接口

EPP接口通常是25芯的D-sub接口,符合IEEE1284標準。其中數據選通和地址選通信號為低電平有效, 且兩者不可能同時為低, 等待信號(nWait) 為握手信號,主要是考慮PC比外設快, 外設通過發送等待信號與PC并口協調工作。空閑信號線(Spare)可以由外設根據需要來決定其狀態,由PC直接讀取并口狀態寄存器的相應位來獲得Spare的狀態信息。

1.3 EPP寄存器說明

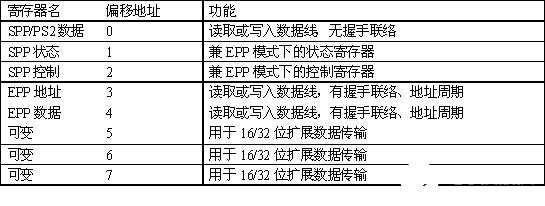

在PC機中,標準并行接口使用了3個8位的端口寄存器。PC就是通過對這些寄存器,也就是通常所說的數據、狀態、控制寄存器的讀寫訪問并口信號的,這3個寄存器的地址分別是基地址、基地址+1、基地址+2。如今,EPP將在基地址+3到基地址+7的范圍內,添加5個寄存器。所以EPP一共使用了8個寄存器,表1列出了這些寄存器及其功能。

表1 EPP的8個寄存器及他們的功能

為了能夠在EPP模式下讀寫一個數據字節,你需要將數據讀取或者寫入EPP數據寄存器(基地址+4),而不是讀寫基地址。同樣的,地址的讀寫也是通過讀取或者寫入EPP的地址寄存器(基地址+3)來實現的。EPP的基地址通常是378h和278h。

1.4 EPP工作模式的時序分析

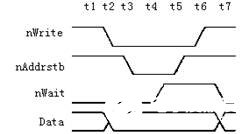

在EPP和ECP模式中,簡單的端口讀寫操作就會自動產生握手聯絡信號,這簡化了很多軟件上的設計。圖1是一個EPP地址寫入周期的時序圖。如圖所示,對EPP數據寄存器的寫操作將導致接口啟動一個完整的數據寫入周期。接口的硬件把待寫入數據置于D0~D7,然后接口自動觸發握手聯絡信號,并檢測外設的應答。讀取一個字節的過程與此類似。同樣的,對EPP地址寄存器進行讀寫操作將引發一個完整的數據讀寫周期。所以,仔細研究EPP工作狀態的時序是非常重要的。

圖1 EPP地址寫入周期的時序圖

2、基于WDM的并口驅動程序的實現

在設計PC機外圍產品時,不僅需要考慮PC接口定義,與接口相關的寄存器定義,數據傳輸協議,還要根據上位機采用的操作系統來編寫合適的通訊程序,以便上位機對數據進行管理和監控。早期的Windows98以及更低版本的操作系統,可以直接訪問并口硬件資源,比如使用C語言中的inp()和outp()函數來編寫簡單的通訊程序。但Windows2000/XP的操作系統采用了一些保護措施,阻止對端口的直接訪問。這樣做雖然提高了系統運行的可靠性,但也增加了軟件上實現通訊的難度。

2.1 WDM驅動程序的種類和結構

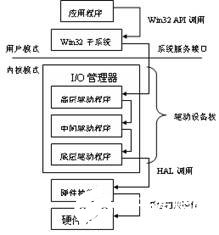

WDM(Win32 Driver Model),即Windows驅動程序模型,是Microsoft力推的全新驅動程序模式,可以用來開發Windows 98和Windows 2000設備驅動程序。圖2顯示了在Win2000/XP系統中應用程序調用一個硬件操作的基本過程,從中可以看到WDM在整個驅動體系結構中的位置何作用。

圖2 Win2000的驅動體系結構

如圖所示,WDM的驅動程序是分層的,一般按照層次分為高層、中間和底層三類。顧名思義,高層驅動程序依賴于中間和底層驅動程序完成工作,而中間驅動程序又依賴于底層驅動程序來完成工作。其中各層驅動程序的詳細介紹請參閱參考文獻[1]。

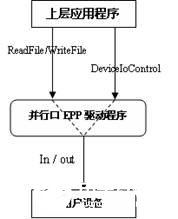

圖3 并行口EPP模式驅動程序接口框圖

2.2 并口EPP模式驅動程序的功能實現

WDM驅動程序開發工具通常用NuMega DriverStudio。因為它可以集成到VC++ 開發環境中,這樣就可以像生成其他工程一樣生成驅動程序框架,省去了大量的編寫代碼的時間。

2.3 EPP模式的基本操作

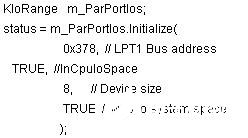

首先定義類KIoRange的一個實例,以對應EPP

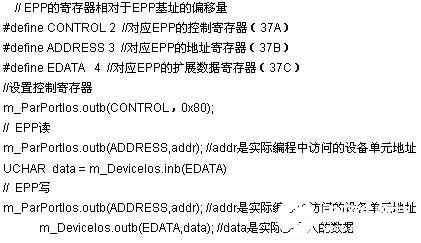

下面就可以用類KIoRange的成員函數來訪問EPP的寄存器:

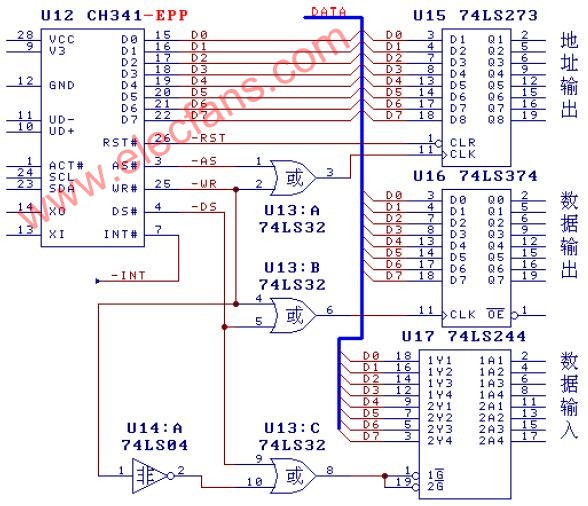

3、并口EPP模式外圍電路硬件設計實例

由上文可知,并口EPP模式下的數據傳輸速度可以達到?s級,所以使用一般的單片機來控制外設與EPP的通訊顯然不能滿足高速的要求。早期,工程師使用大量的邏輯分立元件來設計EPP的外圍電路,但是當計算機的主頻越來越高,EPP 模式在高速數據傳輸中可靠性明顯下降, 因此本文采用大規模可編程邏輯器件, 充分利用其高速和大容量特性設計接口電路, 不僅可大大提高其可靠性, 且易于系統擴展和升級, 可廣泛用于數據采集、D/A 轉換以及數字控制。

采用Xilinx公司的XC95144芯片作為EPP接口模塊的控制單元,并且通過XC95144實現了計算機并口與外部存儲器SRAM的數據交換。在某些外設需要數據存儲和與PC機進行數據交換的應用場合得到了成功的應用。該EPP接口模塊的總體框架如圖4所示。

圖4 EPP接口模塊邏輯框圖

如圖4所示,CPLD內部由各個負責不同功能的子模塊組成,其作用與早期的分立元件一樣,所有子模塊用Verilog設計實現,并且通過了仿真驗證。采用ECS將所有的子模塊組織起來,集成在一塊CPLD內。這樣做大大提高了整個系統運行的可靠性,同時也為系統擴展其他功能提供條件。

由于SRAM相對DRAM具有存儲速度塊,無需定時刷新,控制信號簡單的優點,所以被廣泛的用于需要高速數據處理的小型設備中。圖4中的SRAM采用ISSI的IS61C6416,存儲容量是64K×16位。地址線和數據線都是16條,但是EPP每次只能傳送一個字節的數據,所以CPLD內部需要配置4個8位的數據寄存器,分別保存SRAM的地址和數據總線上的數據。

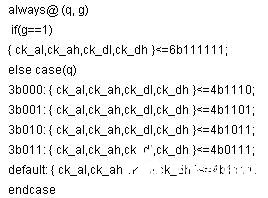

圖4中的總線74LS245是一個總線收發器,由nWrite信號控制并口數據的傳輸方向。74LS138子模塊是一個3-8譯碼器,通過EPP的地址線向138寫入數據,使能不同的觸發信號(CK)來鎖存SRAM的地址或者數據總線上的高/低8位數據。該模塊的Verilog核心源碼如下:

由此可知,如果希望向SRAM的地址低8位寫入數據,PC只需執行outp(0x378+3, 0x00),outp(0x378h+4,地址低8位值) 兩條指令,在執行后一條指令的同時,ck_al選通信號將并口的數值鎖存到SRAM地址低8位鎖存器中。在ck_dh信號觸發的同時將由nWE_cre模塊使能一個nWE信號,將數據寫入SRAM。

4、總結

采用增強型并口(EPP)模式,可以極大地擴展并口通訊的容量和速度。編寫針對并口的WDM驅動程序,既可以保證系統運行的可靠性,也可以增加驅動程序的可移植性。使用CPLD設計并口EPP接口模塊,可以*限度的體現EPP高速傳輸的特性,而且由于將所有的功能模塊集成在一塊芯片中,提高了系統的可靠性,特別是XC95144具有的ISP(在線可編程)技術使復雜的接口電路可根據具體的應用加以修正,大大增強了接口電路的靈活性和可擴展性。本文設計的EPP接口模塊已被成功的運用到某款單片機仿真器產品中,實驗證明這種設計是可行的。

責任編輯:gt

-

寄存器

+關注

關注

31文章

5317瀏覽量

120008 -

計算機

+關注

關注

19文章

7421瀏覽量

87718 -

數據采集

+關注

關注

38文章

5906瀏覽量

113518

發布評論請先 登錄

相關推薦

基于68HC908GP32單片機實現EPP增強并口的接口技術

連接計算機并口的數據采集系統

Windows下通過計算機并口讀寫24系列I2C存儲器

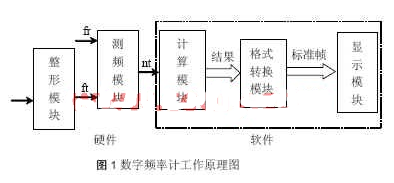

基于Xilinx XC95144和單片機實現數字頻率計的設計

計算機并口EPP模式及基于XC95144芯片實現它的通信設計

計算機并口EPP模式及基于XC95144芯片實現它的通信設計

評論