一 引言

TDI CCD能在不犧牲空間分辨率和工作速度的情況下獲得高靈敏度,這個突出特點使其 在高速、微光領域具有廣泛的應用前景。在科研任務中,新型TDI CCD器件研制時間過長、 供貨不及時等原因會嚴重影響科研生產(chǎn)任務的進度。另外,TDI CCD器件的造價往往很高, 工藝復雜,并且有些新型TDI CCD器件的驅動要求復雜,多電源供電,上下電順序嚴格,這 樣在實驗中就容易引起器件的損壞,造成巨大的損失。這些在電路的調(diào)試階段經(jīng)常發(fā)生。所 以我們迫切需要設計一種能在設備研制過程中和電路的調(diào)試階段模擬實現(xiàn)TDI CCD器件電 性輸入輸出功能的模擬裝置來解決上述問題。為此,本文設計了一種TDI CCD電性模擬器, 能在不用TDI CCD的條件下完成各種實驗任務。

二 TDI CCD電性輸入輸出原理

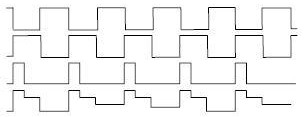

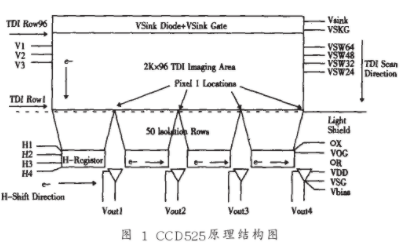

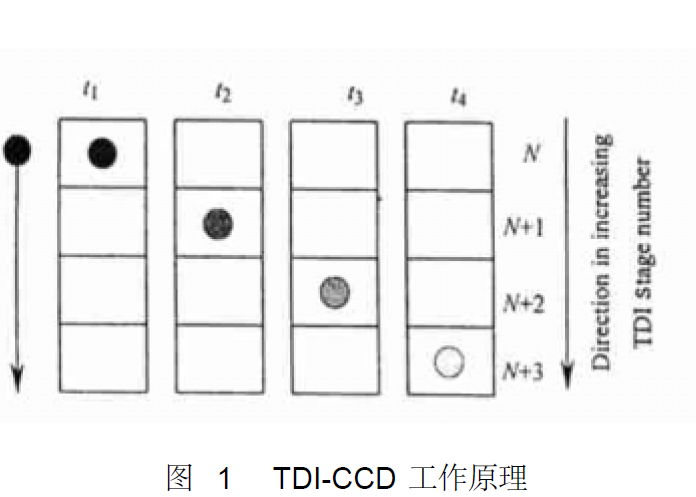

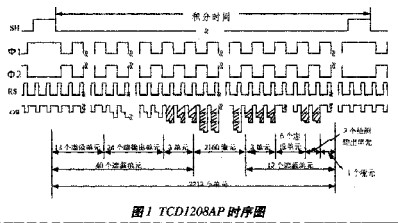

TDI CCD 為時間延遲積分型線陣CCD,它采用多次曝光的方法來提高靈敏度。本文以某 款新型TDI CCD 為例來說明其驅動與輸出視頻信號的關系。此TDI CCD 電性輸入輸出原 理如圖1 所示。在其所有的驅動信號中,與輸出有直接對應關系的主要是兩相讀出信號CR1、 CR2 和復位信號RST。其中CR1 和CR2 是完全倒相的關系。在圖1 中,當TDI CCD 開始 讀有效的視頻信號時,輸出視頻信號OS 在每個RST 信號的上升沿時復位,即在輸出視頻 信號OS 上出現(xiàn)復位干擾脈沖A 段,然后立即回到參考電平B 段。TDI CCD 芯片在CR1 信 號的上升沿處開始讀積分得來的像元信號反映在輸出視頻信號OS 上就是C 段。 A、B、C 三段即構成一個完整的TDI CCD 像元輸出信號單元。由此可知,輸出OS 信號的輸出時序 由兩個驅動信號CR1 和RST 信號決定。

對于大多數(shù)的 TDI CCD 來講,驅動信號CR、RST 高低電平的相差幅度都是比較大的, 有時還有可能是負電平,輸出信號OS 也都集中在比較高的電平上。例如本例中的TDI CCD 中CR 的高低電平各為10V 和0V,RST 的高低電平各為+3V 和-3V。輸出OS 的范圍是 +9V-+7V 之間,其中參考電平B 為+8V。設計TDI CCD 電性模擬器必須按照圖1 所示 時序關系完成電輸入輸出功能,同時也要處理好電平大小關系。

三 系統(tǒng)的原理及設計

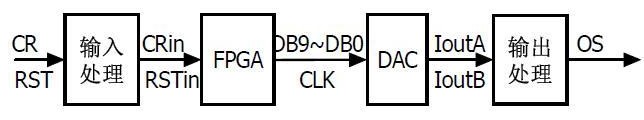

為了要按照圖 1 所示模擬出TDI CCD 的電性輸入輸出關系,本設計所采用的方案是高速 運放作輸入電平轉換,用FPGA 作主控單元,高速DAC 作數(shù)模轉換,高速運放作輸出的結 構。如圖2 所示,系統(tǒng)具體由四部分組成:輸入處理電路、FPGA 單元、數(shù)模轉換電路、輸 出處理電路。其工作原理如下:輸入處理電路把TDI CCD 驅動信號CR、RST 轉化成可輸 入的FPGA 信號Crin、RSTin,然后FPGA 單元再按照圖1 的時序關系輸出十位的數(shù)字信號 DB0~DB9 和時鐘CLK 到DAC。再經(jīng)DAC 進行數(shù)模轉換之后輸出是差分形式的模擬TDI CCD 信號,最后經(jīng)由輸出處理電路使其成為與TDI CCD 輸出信號一致的視頻信號OS。

3.1 輸入驅動信號處理電路

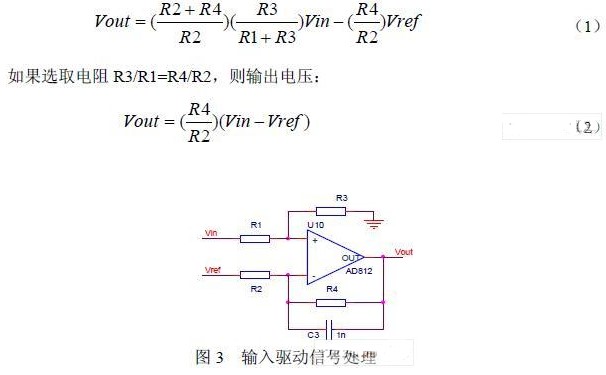

TDI CCD 芯片的輸入驅動信號一般為電壓差較大的兩電平信號,且可能有負電平,不能 直接輸入FPGA,必須先處理。如圖1 所示,本設計中的TDI CCD 讀出信號CR1、CR2 都 是+3V 到-3V 的兩電平信號,電壓差為6V。復位信號RST 的高低電平各為10V 和0V, 電壓差為10V。所以采用的處理電路既要能提升負電平又要減小幅值,在本設計中采用高速 集成運放AD812 來實現(xiàn)這一功能[3]。如圖所示:

依公式(2),圖3 中引入Vref 就可以把驅動信號中的負電平提升到正區(qū)間來,適當?shù)倪x 取Vref、R4/R2 值,就能使Vout 與FPGA 電平匹配。例如處理CR1 信號時,取Vref 為-3V,R4/R2 為0.5,把CR 接到Vin 上,則Vout 輸出區(qū)間為0~3V。同理,將Vref 接地, R4/R2 為 0.3, 把RST 接到Vin 上,則Vout 輸出區(qū)間為0~3V。這樣就可以安全輸入到FPGA 中。

3.2 FPGA 單元

FPGA 單元是本設計的核心器件,為保證系統(tǒng)的性能同時兼顧價格因素,本設計采用了 Xilinx 公司的高性能低成本FPGA 芯片Spartan3 XC3S50。它采用90nm 工藝技術以及300mm 晶圓,大大降低了FPGA 的成本。和其它同類器件相比,具有最低的價格而能提供更高的 容量和性能。設計語言采用Verilog HDL 硬件描述語言[4]。

FPGA 完成的功能是按照圖1 所示輸入輸出信號的時序,由驅動信號CR 和RST 觸發(fā)相應 的給DAC9750 的十位數(shù)字信號DB0~DB9 和時鐘信號CLK。具體關系如前所述。其處理流 程如下:首先由時序判斷電路來判斷輸入的驅動信號的上升沿。當有RST 的上升沿來時, 由其時序關系可知FPGA 的輸出為圖1 中A 段尖峰脈沖電平的十位數(shù)字信號。然后經(jīng)計數(shù) 器延遲一小段時間后,輸出為B 段對應的復位參考電平的十位數(shù)字信號。因CR1 與CR2 互 為反相關系,僅用一相CR1 來判斷就可以。當有CR1 的上升沿來時,F(xiàn)PGA 的輸出為C 段 視頻信號電平對應的十位數(shù)字信號。此視頻信號可根據(jù)不同的要求變化大小,可以是亮度漸 變的視頻信號,也可以是預先設定的信號,這樣既可以模擬出各種的TDI CCD 輸出又可以 模擬疊加噪聲,以滿足不同實驗的需要。

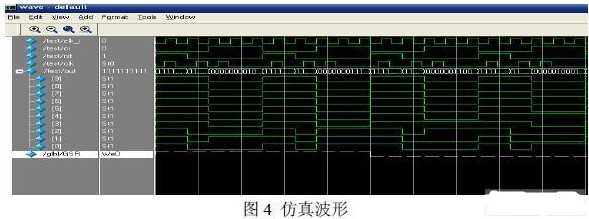

Verilog HDL 語言設計主要有三個模塊:輸入時序判斷模塊根據(jù)CR1、RST 的不同狀態(tài)來 判定某一時刻的輸出到底是圖1 中的A,B,C 哪種狀態(tài)。輸出控制模塊再把相應的輸出轉換 成DB9~DB0 和CLK,其中,對于有效狀態(tài)C,可以去讀取波形存儲模塊中的數(shù)據(jù)來滿足不 同實驗的需求。對于一個簡單的應用,TDI CCD 輸出頻率為8Mhz 且輸出為亮度遞增,其 仿真波形如圖4 所示:

由此可以看出,本設計還具有驅動時序檢測的功能,當所用的驅動時序不是嚴格如圖1 所示的時序的話,就不能輸出正確的TDI CCD 視頻信號。

3.3 數(shù)模轉換

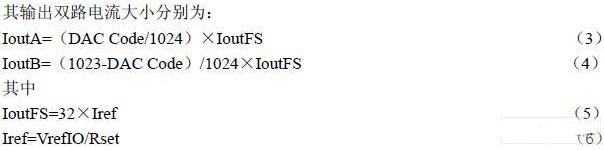

為保證 TDI CCD 的高速、低噪聲要求,設計采用了Analog Device 公司的高速D/A 轉換 芯片AD9750。它是一款雙路電流輸出型、最大輸出電流為20mA、輸出阻抗大于100MΩ、最大轉換速率為125MSPS 的十位高速數(shù)模轉換器。它接收由FPGA 產(chǎn)生的十位數(shù)字信號和 時鐘信號,并把轉成模擬信號以電流形式輸出。為滿足電路的低噪聲要求,本設計采用了雙 路差分電流輸出[5]。

VrefIO 設為內(nèi)部參考電壓1.25V,取Rset=2kΩ,則IoutFS=20mA,為AD9750 的最大電流輸出值。

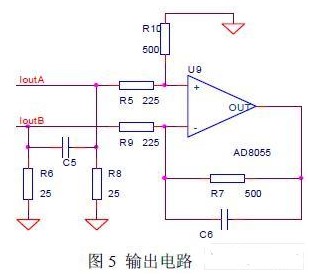

3.4 輸出處理

由 AD9750 產(chǎn)生的雙路模擬電流差分信號要轉換成相應的電壓形式。AD9750 的輸出負 載可以有多種形式,為了最大限度的保證信號精度,減少信號間干擾及噪聲,設計中采用了 雙路輸出加到運算放大器AD8055 上的結構。如圖5 所示: AD9750 的輸出IoutA 及 IoutB 分別接25Ω的負載。電容C5 起到低通濾波和減小運算放大器的輸出失真的作用。這樣雙路 差分信號經(jīng)AD8055 轉成單端信號輸出。

由 AD8055 輸出的電壓信號的幅值范圍為:-1V~+1V,TDI CCD 視頻輸出信號的范圍大約 在+9V~+7V 之間,所以要經(jīng)過一個電壓提升的電路使輸出符合要求。所采用的電路如圖3 所示的電路結構。把一個-8V 的直流電平接到反相端,AD8055 的輸出信號接到同相端。 放大倍數(shù)為1,最后得到的輸出即是TDI CCD 視頻信號。

3.5 提高信號信噪比

按照上述方法,可以由TDI CCD 的驅動得到相應的視頻輸出信號。但是由于TDI CCD 的 工作頻率比較高,使得整個系統(tǒng)的工作頻率都很高。所以,如何去除掉干擾和噪聲,提高信 號質(zhì)量是本設計的重要問題。為此,采取了以下措施:

PCB 板布局是產(chǎn)生干擾的,也是去除干擾的關鍵。本設計重點考慮FPGA 與高速 DAC 以及輸出運放之間的布局。盡量減少高速信號線的線長,特別是FPGA 與高速DAC 之間的線長。對電源濾波,減少電源帶來的干擾。合理設計地平面,采用數(shù)字地和模擬地分 開的方式,減少各器件間的干擾。

四 結束語

本文設計的TDI CCD 電性模擬器能模擬出TDI CCD 芯片的電性輸入輸出功能,同時具有 一定的驅動時序檢測功能,它能替代昂貴的TDI CCD 芯片完成部分相關的實驗工作,且功 能基本滿足要求。

-

芯片

+關注

關注

454文章

50430瀏覽量

421866 -

CCD

+關注

關注

32文章

879瀏覽量

142144 -

模擬器

+關注

關注

2文章

869瀏覽量

43165

發(fā)布評論請先 登錄

相關推薦

基于CPLD芯片MAX7000AE實現(xiàn)TDI/CCD驅動時序的設計

高速EM CCD圖像傳感器CCD97時序驅動電路的設計方法

TDI-CCD圖像傳感器

一種多普勒模擬器的設計與實現(xiàn)The Design and I

TDI-CCD圖像傳感器電荷包總轉移效率分析

基于FPGA 的TDI-CCD 時序電路的設計

線陣CCD驅動時序及模擬信號處理的設計

基于CPLD的CCD相機圖像信號模擬器的設計

使用FPGA實現(xiàn)線陣CCD驅動時序及模擬信號處理的設計說明

CCD的工作原理和幾種產(chǎn)生CCD驅動時序方法

如何分析高分辨力TDI-CCD遙感相機的特性

使用TDI CCD芯片的電性模擬器可進行驅動時序檢測

使用TDI CCD芯片的電性模擬器可進行驅動時序檢測

評論