脈沖壓縮技術是指對雷達發射的寬脈沖信號進行調制(如線性調頻、非線性調頻、相位編碼),并在接收端對回波寬脈沖信號進行脈沖壓縮處理后得到窄脈沖的實現過程。脈沖壓縮有效地解決了雷達作用距離與距離分辨率之間的矛盾,可以在保證雷達在一定作用距離下提高距離分辨率。

線性調頻信號的脈沖壓縮

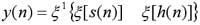

脈沖壓縮的過程是通過對接收信號s(t)與匹配濾波器的脈沖響應h(t)求卷積的方法實現的。而處理數字信號時,脈壓過程是通過對回波序列s(n)與匹配濾波器的脈沖響應序列h(n)求卷積來實現的。

依據式(1)的實現方法叫做時域相關法。根據傅里葉變換理論,時域卷積等效于頻域相乘,因此,式(1)可以采用快速傅里葉變換(FFT)及反變換(IFFT)在頻域內實現,稱為頻域快速卷積法。

用頻域方法實現數字脈壓,其基本原理是先對外部采樣信號進行快速傅里葉變換(FFT)以求得回波信號頻譜S(w),再將S(w)與匹配濾波器頻譜H(w)進行乘積運算,最后對乘積結果進行快速傅里葉逆變換(IFFT)得到脈壓結果Y(n),用公式表示為

(2)

(2)

頻域快速卷積法的原理如圖1所示,存儲器中存儲的是匹配濾波器傳遞函數H(k)。

圖1 頻域脈沖壓縮原理框圖

依據匹配濾波理論,數字匹配濾波器的脈沖響應h(n)及傳遞函數H(k)為

h(n)=s1(-n),H(k)=s1(k) (3)

其中, s(n)為雷達發射信號序列;S(k)為信號序列頻譜。

數字脈沖壓縮系統

1 系統構成和硬件設計

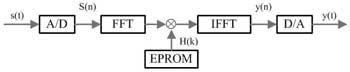

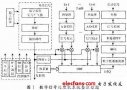

本系統是單脈沖雷達信號處理機的一部分,由于單脈沖雷達所需要處理的距離、方位/俯仰兩路信號來自同一發射信號源的目標反射回波,要求對兩路信號進行同時、同頻ADC采樣和完全相同算法的脈沖壓縮處理。針對這一特點,雷達數字脈沖壓縮系統將相同的脈沖壓縮處理功能移至兩片FPGA芯片內。由于對雷達體積、重量、功耗等指標有特殊要求,本系統采用二個通道的脈沖壓縮處理硬件結構,即方位和俯仰兩路信號分時共用一個脈沖壓縮通道。雷達信號處理分系統硬件結構如圖2所示。

圖2 雷達信號處理分機硬件結構圖

系統中,數據采樣后分為和路和差路(包括航向差和俯仰差)兩組數據,分別輸入兩片FPGA單獨進行脈沖壓縮計算,脈沖壓縮后再送入后端的DSP做譜分析,以確定目標的距離、速度、方位等情況。由框圖中我們看到,FPGA不僅要對數據做脈沖壓縮計算,還承擔了對輸入數據處理和讀寫狀態寄存器的任務。狀態寄存器存儲了脈沖壓縮計算的控制參數,由后端的DSP根據分析的結果對其做相應的控制。

2 軟件設計

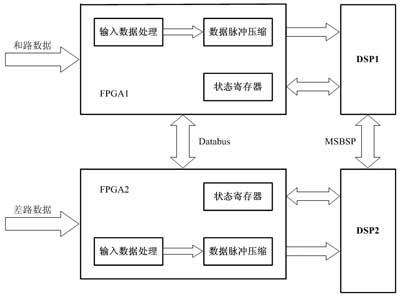

根據位內運算結構的特點,針對芯片內嵌的塊RAM資源豐富的優勢,脈沖壓縮系統采用兩片存儲器的乒乓操作,在FFT的每一級運算中使一片雙口RAM的兩個端口同時處于讀或寫狀態,達到每個時鐘周期輸出兩個操作數的需要。而且,數據經蝶算單元運算結束后以相同的地址寫入另一片雙口RAM,節省了寫地址生成的時間,為設計高速的FFT系統提供了可能。

如圖3所示,采用兩片中間級RAM:RAMA和RAMB,用它們來完成乒乓操作。地址產生模塊生成的讀地址同時與中間級的兩片RAM相連,控制相應的RAM讀取所需的操作數,操作數經蝶算模塊運算后以同址方式寫入到另一片RAM的兩個端口。RAM的讀寫由地址產生模塊生成的寫使能信號控制,處于讀狀態的RAM寫使能置零,而另一片的寫使能端置高,處于寫狀態。而且,RAM被設置為寫狀態時輸出端口不輸出,以減少RAM的讀取次數。這樣,輸入RAM變為輸出RAM,輸出RAM變為輸入RAM,如此反復,直到FFT最后一級。

圖3 脈沖壓縮系統的結構框圖

FFT的每一級運算結束后,兩塊RAM功能互換,寫使能變反,運算結束。RAM的每次輸出數據需經過數據選擇模塊(datamux),該模塊由地址產生模塊輸出的當前級數信號Stage控制。本系統采用三種FFT模式:1024點、512點和256點,均采用同一旋轉因子ROM。根據FFT點數的不同,ROM的讀地址expaddr做相應的調整,這樣的設計也在很大程度上節省了芯片內的塊RAM資源。

3 系統性能

針對本雷達信號處理機對實時性和高精度的要求,我們設計研制出具有自主知識產權的高性能脈沖壓縮處理系統,該處理系統具有以下特點:

A 處理系統內部采用24位自定制浮點數據格式,能夠兼顧處理系統的資源占用和處理精度。數據輸入為定點數據格式,輸出為標準32位浮點數據格式。

B 處理系統工作時,需要依次完成FFT運算、復數乘法運算和IFFT運算。在進行FFT和IFFT運算時,蝶形運算/乘法運算單元完成蝶形運算操作;在進行復數乘法運算時,該單元完成乘法操作。這兩種操作在實際工程中分時實現,并且共享浮點數規格化處理硬件電路。

C 處理系統中進行FFT/IFFT運算的長度N(N=2048、1024或512)由雷達信號處理機的控制信號決定。

D 內置三組數據存儲器(輸入數據RAM、同址運算RAM、輸出數據RAM),保證處理系統能全速運行,提高該處理系統的處理能力。

E 旋轉因子(N=1024時的FFT運算旋轉因子)以上電初值的形式存儲在FPGA片內存儲器中。當N=512、256時,其旋轉因子從N=1024的旋轉因子中抽取得到。N點IFFT的旋轉因子由N點FFT的旋轉因子取共扼得到。實驗結果

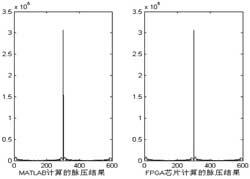

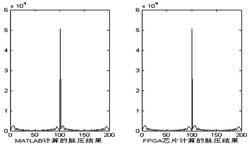

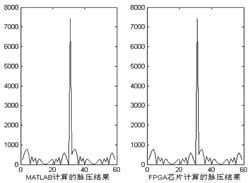

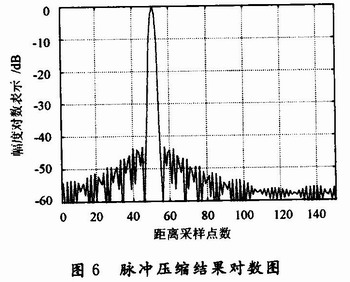

本雷達信號處理機存在三組時間—帶寬指標,分別對其進行理論仿真和實際輸出結果對照,其結果如圖4、圖5和圖6所示。

圖4 1024點脈沖壓縮狀態FPGA計算結果與MATLAB計算結果對比圖

圖5 512點脈沖壓縮狀態FPGA計算結果與MATLAB計算結果對比圖

圖6 256點脈沖壓縮狀態FPGA計算結果與MATLAB計算結果對比圖

圖4至圖6分別對應時寬為60μs、20μs、6μs,帶寬均為5M的線性調頻信號。其中,左圖對應MATLAB的計算結果,右圖為FPGA芯片的輸出結果。可以看到,FPGA芯片的輸出結果和MATLAB仿真結果吻合。經測試驗證結果良好,最大誤差不超過-76db,在內部時鐘頻率80MHz條件下,完成1024點FFT 運行時間為146μs ,滿足了雷達系統實時處理要求,達到了滿意的效果。

-

濾波器

+關注

關注

160文章

7727瀏覽量

177674 -

存儲器

+關注

關注

38文章

7452瀏覽量

163603 -

雷達

+關注

關注

50文章

2897瀏覽量

117310

發布評論請先 登錄

相關推薦

雷達信號處理機的脈沖壓縮系統設計介紹

雷達信號處理機的脈沖壓縮系統設計介紹

評論