自20世紀80年代單片機引入我國以來,學習和應用單片機的熱潮始終不減,特別是MCS51系列。這是由單片機的特點決定的。實際上,從單片機/CPLD應用通用數字集成電路系統,到廣泛應用單片機,是我國電子設計在智能化應用水平上質的飛躍。據統計分析,單片機的銷量單片機/CPLD到目前為止依然逐年遞增,而且在很長一段的時間內,單片機依然會是電子設計的主角(雖然這一地址已經受到了CPLD的挑戰)。

1 純單片機系統優缺點

①大量單片機/CPLD的外圍芯片和接口電路使得單片機應用系統的設計變得簡單而且快捷,新型單片機的上市和高級語言的支持(如C51)進一步延長了單片機的壽命。

②長期穩定的發展和使單片機性價比非常高,而且單片機/CPLD積累了大量的資料并擁有了大量的工程技術為員。這一點是CPLD目前難以達到的。

但是,單片機的缺點也有目共睹:

①低速。即使是高速度單片機也只能工作在μs級,這是由單片機串行工作的特點所決定的。

②低可靠性。雖然單片機/CPLD目前有很多器件與設計在一定程序上解決了部分問題,如看門狗的廣泛應用,但在某些情況下瞬間的復位也會造成嚴重后果。

2 純CPLD設計的優缺點

即使單純單片機/CPLD的單片機結構能完成的功能,在某些情況下也寧可使用純數字電路完成。而當前開始流行的CPLD,則不但克服了單片機的缺點,而且由于可采用VHDL語言編程,進一步單片機/CPLD打破了軟硬件工程師的界限,加速了產品的開發過程,使純數字電路的設計變得簡單。人們甚至在討論用C作為下一代硬件描述語言。

難怪有專家指出,電子設計的單片機時代即將過去,而以PLD為核心的EDA(電子設計自動化)將是單片機/CPLD未來設計的方向。由于超大規模集成電路技術的發展,單片PLD芯片上已經可以集成上百萬門,就系統規模而言,將單片機設計在內也沒什么問題。美國的可編程器件廠商已經以軟核和硬核嵌入兩種形式(將單片機電路嵌入PLD)為設計人員提供幫助。PLD器件取代單片機是早晚的事。但是,在我國當前的普遍應用中,單純依靠PLD器件還有點早,原因如下:

①由于歷史單片機/CPLD的原因,我國的電子設計人員大部分應用的是MCS51系列單片機,還沒聽說哪家公司提供軟核或硬核集成。而讓這么多人改學其它系列單片機還需要一段時間,而且原有的程序更使人不愿改動。

②單片機價格低廉,而PLD如果增加單片機內核的話,至少在目前形勢下價格會比較昂貴。

所以,由于單片機和PLD的互補性,利用單片機加PLD的結構至少在近期內將一種較好的選擇。下面通過作者設計的實例,介紹MCS51+EMP703S結構體系的特點及注意事項。

3 單片機+CPLD結構體系設計實例

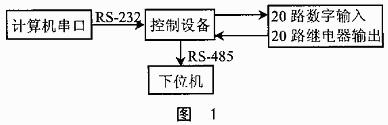

本設計用于單片機/CPLD自動化控制,設計要求如圖1所示。

對于一個熟悉單片機系統設計的工程師而言,上述設計不會有技術上的困難,問題在于:

①要用兩個全雙工串口;

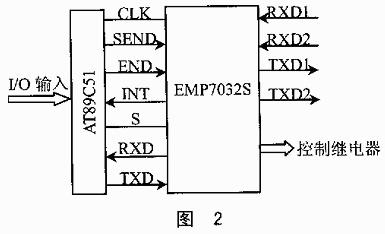

②要求比較多的輸入輸出口。如果用傳統設計方法,勢必要用比較多的芯片,電路板的設計也較麻煩,一旦設計有誤,必須重新設計整個電路板,費時、費力、費錢。而采用MCS51+EMP7032S設計后,基本上做到了模塊化設計,電路的修改只是編程而已。從開始設計到定型所用的時間,基本上就是制作電路板的時間。由于設計了輸出信號鎖存,完全避免了單片機程序跑飛和看門狗復位所引起的輸出的跳變,這時設備完全至關重要。圖2是設計原理電路圖。

從設計的原理圖可以看出,主要部分單片機/CPLD只需要兩片集成電路:單片機AT89C51和CPLD——EPM7032S,并且電路板采用模塊化設計,預留了擴展接口,只需要配上不同的處理模塊,就可以實現數據采集、鍵盤掃描、顯示驅動和繼電器控制等許多功能。單片機和EPM7032S之間采用了類似SPI接口的通信方法。如圖2所示。采用這種方法,既實現了單片機和CPLD之間的通信,又具有靈活性,并且節約了大量的端口資源。

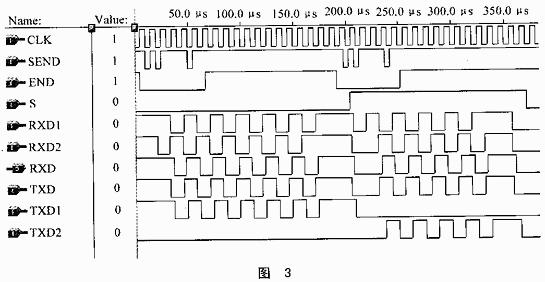

EPM7032S有36個I/O口,除去用于和單片機通信的7個端口,還有29個端口可以使用。可滿足大部分對于端口擴展設計的需求。圖3是為EPM7032編寫的測試程序的波形仿真圖。

圖3中:CLK為同步時鐘;SEND為數據接收;END為SEND信號的控制端;S為位選端,用業控制串行通信端口選擇;RXD、TDX為單片機和EPM7032之間的串行通信端口;RXD1、TXD1、RXD2、TDX2為串行通信擴展口。這種方案,已經過多次檢驗,對于節省PCB板的面積和布線難度、提高設計可靠性和提高設計效率都非常有幫助。

單片機程序

sdosend:

setb clk

setb end

mov r7,#06h

ssend:

rrc a

mov send,c

nop

nop

clr clk

nop

nop

setb clk

djnz r7,ssend

nop

nop

clr end

nop

nop

setb end

ret

VHDL 語言程序

Library ieee;

Use ieee.std_logic_1164.all;

Entity pldse1 is

Port

(

so,clk,send :in std_logic

);

end pldse1;

architecture io1 of pldse 1 is

begin

process(cs)

begin

if(cs='0')then

casep qout is

when "000000"=>

when "000001"=>

when "000010"=>

··················

when "000100"=>

when "000101"=>

when others=>null;

end case;

else null;

end if;

end process;

process(clk)

begin

if(clk'event and clk='0')then

qout<=data &qout(5 downto 1)

else null;

end if;

end process;

end io 1;

通過程序單片機/CPLD可以看出,利用CLK和SEND線發送控制信號;利用END作為結束位,無論什么情況,如果沒有結束位的下降沿脈沖,PLD的輸出端口不會改變,這樣可確保輸出信號的穩定。這種輸出鎖存使單片機在死機復位時依然不影響繼電器原輸出。PLD在接收到單片機的控制信號后首先暫存,直到收到END的下降沿脈沖時再把數據輸出,作出相應的置高低電平的動作。

由上述設計可以看出,單片機和PLD在使用上有很強的互補性:在邏輯運算、智能控制方面,單片機具有不可替代的優越性;而在高速穩定等方面,PLD無疑是首選。因此,在目前的電子設計中,充分利用單片機+PLD結構將起到事半功倍的效果。

:

-

單片機

+關注

關注

6032文章

44514瀏覽量

632981 -

PLD

+關注

關注

6文章

224瀏覽量

59338

發布評論請先 登錄

相關推薦

單片機+CPLD結構體系在電子設計中的應用

純硬件的STC 單片機自動下載設計

單片機匯總_常用單片機優缺點詳細剖析

電子設計領域的單片機/CPLD自動化控制

在51單片機中使用ucosii有哪些優缺點詳細資料分析

純單片機和純CPLD設計的優缺點分析

純單片機和純CPLD設計的優缺點分析

評論