引言

采樣保持電路(S/H)是數(shù)據(jù)采集系統(tǒng)尤其是模數(shù)轉(zhuǎn)換器(A/D)的一個(gè)重要組成部分。近幾十年來(lái)無(wú)線通訊的迅速發(fā)展,使得數(shù)據(jù)的傳輸速率越來(lái)越快。復(fù)雜度不斷提高的調(diào)制系統(tǒng)和電路使得模數(shù)轉(zhuǎn)換器(ADC)的采樣頻率達(dá)到射頻的數(shù)量級(jí),與此同時(shí),模數(shù)轉(zhuǎn)換器的精度也超過(guò)12位以上。在這種高速度和高精度的要求下,采樣保持電路的作用就越發(fā)顯得重要,因?yàn)樗梢韵?shù)轉(zhuǎn)換器前端采樣級(jí)的大部分動(dòng)態(tài)錯(cuò)誤。傳統(tǒng)的開(kāi)環(huán)采樣保持電路只能達(dá)到8~10位的精度,主要由于開(kāi)關(guān)的非理想特性,諸如電荷注入、時(shí)鐘饋通、開(kāi)關(guān)的非線性電阻等。

另一方面,高精度的閉環(huán)采樣保持電路又受限于運(yùn)算放大器的性能。無(wú)線通訊系統(tǒng)十分重視降低功耗,流水線A/D通常是無(wú)線通訊器件中的一部分,因此在設(shè)計(jì)的時(shí)候也將功耗作為一個(gè)重要的考慮因素。本文設(shè)計(jì)了一個(gè)用于14位20MHz流水線A/D的采樣保持電路,通過(guò)采用flip-around結(jié)構(gòu)來(lái)降低功耗。同時(shí)為了抑制傳統(tǒng)開(kāi)關(guān)的一些非理想特性,采取自舉開(kāi)關(guān)來(lái)降低信號(hào)失真,從而提高整個(gè)系統(tǒng)的信噪比。通過(guò)采用增益增強(qiáng)技術(shù),實(shí)現(xiàn)了高增益低功耗運(yùn)算放大器。通過(guò)這些措施,在較低功耗的情況下仍然獲得了14位的精度。

本文主要分以下幾部分:介紹采樣保持電路的結(jié)構(gòu);詳細(xì)介紹運(yùn)算放大器的設(shè)計(jì);描述自舉開(kāi)關(guān)的實(shí)現(xiàn);最后給出電路的仿真結(jié)果和結(jié)論。

采樣保持電路的結(jié)構(gòu)

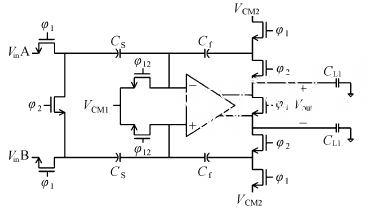

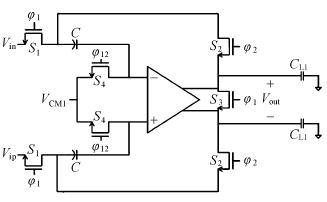

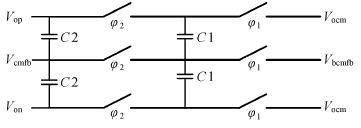

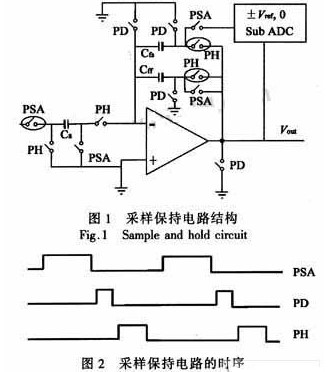

采樣保持電路的要求主要是在較低功耗的情況下能采樣大帶寬、高頻率輸入信號(hào),并且在驅(qū)動(dòng)較大負(fù)載的情況下實(shí)現(xiàn)盡可能小的失真。閉環(huán)轉(zhuǎn)換電容采樣保持電路通常有兩種結(jié)構(gòu),如圖1和圖2所示。

圖1電荷傳輸結(jié)構(gòu)采樣保持電路

圖2Filp-around結(jié)構(gòu)采樣保持電路

圖1所示的結(jié)構(gòu)稱之為電荷傳輸采樣保持電路(charge-transferringS/H)。在采樣階段,將輸入信號(hào)存儲(chǔ)在采樣電容CS上,并且在保持階段,僅將差分電荷轉(zhuǎn)移到反饋電容Cf上。因?yàn)楣材k姾纱鎯?chǔ)在采樣電容CS上,所以這種結(jié)構(gòu)的采樣保持電路可以處理共模范圍較大的輸入信號(hào)。

圖2所示的結(jié)構(gòu)稱之為翻轉(zhuǎn)(flip-around)采樣保持電路。在采樣階段,將輸入信號(hào)存儲(chǔ)在采樣電容C上,而在保持階段,將采樣電容C翻轉(zhuǎn)到輸出端。因此,理想的反饋因子β,第一種結(jié)構(gòu)為0.5,而后一種在忽略輸入管的寄生電容情況下為1,后者的反饋因子是前者的兩倍。因此在同樣的閉環(huán)帶寬要求下,后者的放大器單位增益帶寬(GBW)只需要前者的一半,這就大大地降低了放大器的功耗。而采樣保持電路的功耗主要來(lái)自于內(nèi)部運(yùn)算放大器的功耗。

對(duì)于A/D而言,采樣保持電路的輸入噪聲直接影響到A/D的輸入?yún)⒖荚肼暋R虼艘M量減小由采樣保持電路引入的噪聲。在采樣階段,忽略晶體管的寄生電容,則電荷傳輸采樣保持電路的輸入?yún)⒖荚肼暪β蕿閂2n=(2κT)/C。而翻轉(zhuǎn)采樣保持電路的輸入?yún)⒖荚肼暪β蕿閂2n=κT/C。后者的噪聲比前者降低了一半。在保持階段,假設(shè)放大器的噪聲主要由輸入晶體管的熱噪聲決定,則輸入?yún)⒖荚肼暪β士梢杂霉奖硎荆?/p>

V2n=(8πκT)P3βCL[1] (1)

(1)式表明翻轉(zhuǎn)采樣保持電路由于較高的反饋因子使得噪聲功率僅為電荷傳輸采樣保持電路的1/2。

由于在減小噪聲和降低功耗方面的優(yōu)勢(shì),采用翻轉(zhuǎn)結(jié)構(gòu)作為采樣保持電路結(jié)構(gòu)。但需要指出的是,由于輸入晶體管寄生電容的影響,使得反饋因子小于理想值1,所以在噪聲和功率方面的改進(jìn)可能會(huì)小于上面的理想值。另外,如果輸入信號(hào)的共模電壓V sig-cm不等于采樣保持電路中運(yùn)算放大器的輸出共模電壓V out-cm,則在維持階段,由于運(yùn)算放大器的共模反饋電路使得輸出的共模電壓穩(wěn)定在V out-cm,因此運(yùn)算放大器的輸入共模電壓會(huì)有一個(gè)階躍變化ΔV in-cm=V out-cm-V sig-cm。因此為了滿足各種共模信號(hào)的要求,則該運(yùn)算放大器要求較大的輸入共模范圍。

運(yùn)算放大器的設(shè)計(jì)

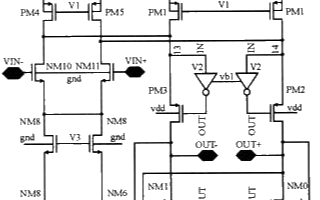

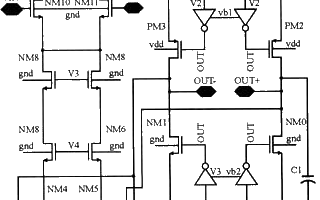

由于噪聲和功率方面的優(yōu)勢(shì),采用翻轉(zhuǎn)結(jié)構(gòu)作為采樣保持電路的結(jié)構(gòu),同時(shí)采用折疊式共源共柵放大器來(lái)實(shí)現(xiàn)大輸入共模范圍的要求。采用PMOS管作為輸入管,這樣就可以使第二個(gè)極點(diǎn)推到較高的位置。因?yàn)椋诙€(gè)極點(diǎn)的位置為折疊點(diǎn)。而NMOS折疊管的寄生電容比PMOS折疊管的寄生電容小的多。除此之外,PMOS管還可以采用自襯底工藝,從而大大減小由于工藝產(chǎn)生的偏差。唯一的缺點(diǎn)是PMOS輸入管有較大的寄生電容,從而減小翻轉(zhuǎn)結(jié)構(gòu)在功率和噪聲方面的改進(jìn)。

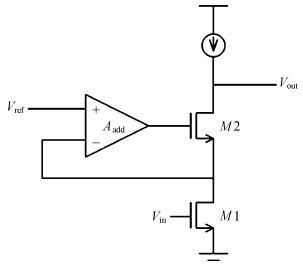

另外由于該采樣保持電路運(yùn)用于14位20MHz流水線A/D,則要求該放大器的直流增益必須大于93dB,輸出在25ns的建立時(shí)間內(nèi)穩(wěn)定在最終值0.003%。對(duì)于單極點(diǎn)放大器,建立時(shí)間又可以轉(zhuǎn)化為對(duì)GBW的要求。因此為了實(shí)現(xiàn)近似單極點(diǎn)放大器,則要求放大器必須為一級(jí)結(jié)構(gòu)。而為了實(shí)現(xiàn)如此高的直流增益,則必須采用增益增強(qiáng)技術(shù),原理示意圖如圖3所示。圖中,由M1、M2和理想電流源構(gòu)成主運(yùn)放,Aadd為用于增益增強(qiáng)的輔助放大器。采用該技術(shù)后,這個(gè)電路的直流增益為:

![]()

其中,ro1、ro2為M1、M2的輸出電阻,gM1、gM2為M1、M2的跨導(dǎo)。

圖3增益增強(qiáng)結(jié)構(gòu)的運(yùn)算放大器

采用該技術(shù)之前,放大器的直流增益為:

![]()

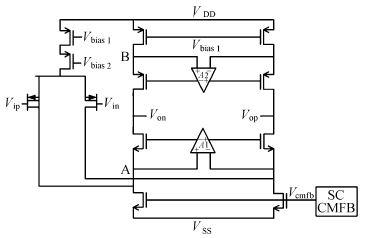

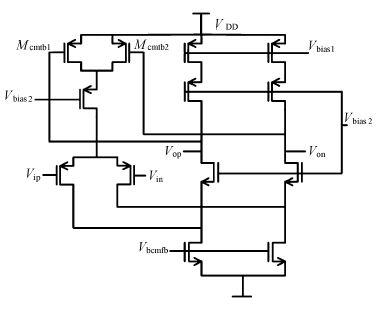

(2)式和(3)式表明,增益增強(qiáng)技術(shù)可以使放大器的直流增益提高一個(gè)數(shù)量級(jí)。因此在該放大器的設(shè)計(jì)中,采用如圖4所示的帶有A1和A2兩個(gè)輔助放大器的增益增強(qiáng)折疊式共源共柵放大器,其中,A1和A2以外的部分為主放大器。為了簡(jiǎn)化設(shè)計(jì),輔助放大器也采用折疊式共源共柵結(jié)構(gòu)。因此,輔助方法器和主放大器的偏置電路可采用同一個(gè)偏置電路,大大簡(jiǎn)化了設(shè)計(jì)。而輔助放大器的電流僅為主放大器電流的1/10,因此與套筒式共源共柵放大器相比,整體電路并不會(huì)額外增加電流。

圖4增益增強(qiáng)折疊式共源共柵運(yùn)算放大器

需要提出的是,主放大器和輔助放大器采用了不同的共模反饋電路(CMFB)。對(duì)于主放大器而言,因?yàn)檩敵鲭妷悍秶?Vpp,因此在實(shí)現(xiàn)較大的輸出擺幅,又不額外增加功耗的要求下,采用開(kāi)關(guān)電容共模反饋電路。如圖5所示,通過(guò)電容C1和C2間的電荷轉(zhuǎn)移調(diào)節(jié)電流源管的柵電壓來(lái)改變輸出電流,從而穩(wěn)定輸出共模電壓。對(duì)于輔助放大器而言,其輸出擺幅很小,輸出為共柵管的偏置電壓,采用一種簡(jiǎn)單的連續(xù)時(shí)間共模反饋電路,如圖6所示,其原理是通過(guò)調(diào)節(jié)Mcmfb1和Mcmfb2管子的電流來(lái)穩(wěn)定輸出共模電壓。

圖5開(kāi)關(guān)電容共模反饋電路

圖6輔助放大器及其共模反饋電路

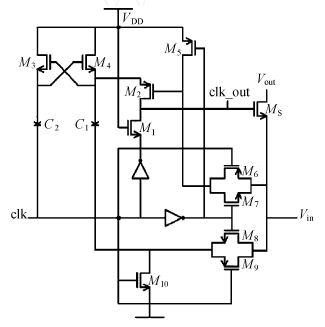

自舉開(kāi)關(guān)

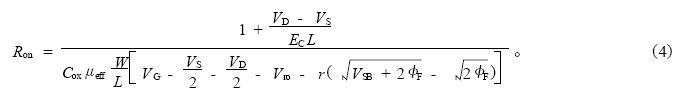

開(kāi)關(guān)是采樣保持電路的一個(gè)重要組成部分。它是信號(hào)失真,電荷注入和時(shí)鐘饋通效應(yīng)主要。后兩者可通過(guò)采用下極板采樣和全差分電路結(jié)構(gòu)來(lái)消除。A/D對(duì)信號(hào)失真要求很高,因?yàn)槭д嬷苯佑绊懙紸/D的精度。當(dāng)信號(hào)幅度較高時(shí),采樣保持電路的精度和速度就直接受限于失真。而失真的主要原因是開(kāi)關(guān)導(dǎo)通電阻的非線性。開(kāi)關(guān)導(dǎo)通電阻不是一個(gè)固定值,而是輸入信號(hào)的函數(shù)。對(duì)于短溝器件的導(dǎo)通電阻為:

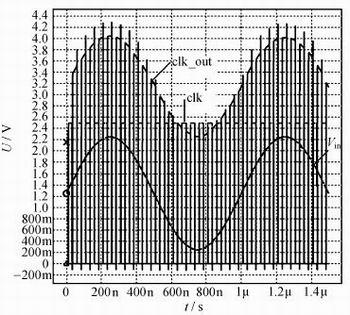

其中VG,VS,VD和VB分別為晶體管柵、源、漏和襯底電壓。一般,輸入信號(hào)電壓連接在源端。假設(shè),VS=VD=VB。通過(guò)PMOS管的自襯底技術(shù)使襯底和源短連接在一起,從而消除分母中后半部分平方根中的部分。則開(kāi)關(guān)的導(dǎo)通電阻RON主要有VG-VS的差值決定,自舉開(kāi)關(guān)就是通過(guò)固定這個(gè)差值來(lái)實(shí)現(xiàn)開(kāi)關(guān)的線性導(dǎo)通電阻,從而消除信號(hào)失真。自舉開(kāi)關(guān)電路如圖7所示,工作原理是:當(dāng)CLK為高的時(shí)候,自舉開(kāi)關(guān)屬于關(guān)斷狀態(tài),此時(shí)開(kāi)關(guān)MS的柵通過(guò)管子M1連接在VSS。而同時(shí),電容C1兩端電壓差為VDD-VTH,其中VTH為NMOS管的閾值電壓。當(dāng)CLK為低的時(shí)候,自舉開(kāi)關(guān)屬于導(dǎo)通狀態(tài),此時(shí),M1管關(guān)閉,通過(guò)M2管使開(kāi)關(guān)MS的柵電壓固定為Vin+(VDD-VTH)。其仿真結(jié)果如圖8所示。需要指出的是,圖2中4處有開(kāi)關(guān),其中S1和S2采用自舉開(kāi)關(guān),S3采用CMOS傳輸門,S4采用簡(jiǎn)單NMOS傳輸門,這樣可以簡(jiǎn)化電路并降低功耗。

圖7自舉開(kāi)關(guān)

圖8自舉開(kāi)關(guān)仿真結(jié)果

仿真結(jié)果和結(jié)論

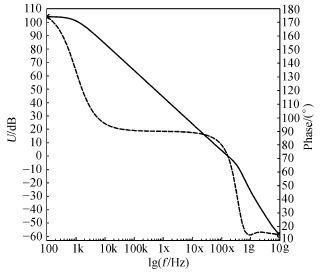

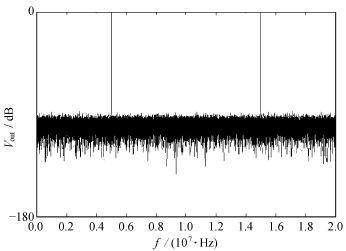

圖4所示的運(yùn)算放大器的Hspice的仿真結(jié)果為圖9,在電路負(fù)載為15p的情況下,直流增益為104.6dB,單位增益為166MHz,相位裕度為71度。完全滿足設(shè)計(jì)要求。圖10為該采樣保持電路的在輸入信號(hào)為5MHz,全差分信號(hào)幅度為2Vpp采樣頻率為20MHz情況下的輸出頻譜圖。仿真結(jié)果顯示,該電路的SFDR為92.4dB,SNDR為88.6dB,SNR為96.1dB。

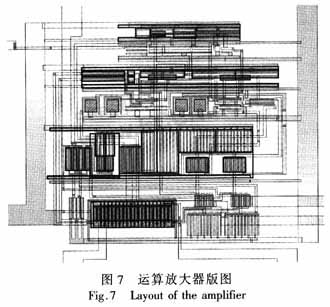

本文描述了一個(gè)用于14位20MHz流水線A/D的采樣保持電路。該電路采用UMC logic 0.25μm2.5V工藝,通過(guò)采用增益增強(qiáng)放大器和自舉開(kāi)關(guān),在輸入為±1V頻率為5MHz正弦波,采樣頻率為20MHz的情況下獲得了96.1dB的信噪比。

圖9運(yùn)算放大器的頻率特性曲線

責(zé)任編輯:gt

-

數(shù)據(jù)采集

+關(guān)注

關(guān)注

38文章

5925瀏覽量

113539 -

仿真

+關(guān)注

關(guān)注

50文章

4048瀏覽量

133431 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3144瀏覽量

126747

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)問(wèn)ADS6422這個(gè)差分輸入的采樣保持電路中的Ron有什么用呢?

一種用于高速ADC的采樣保持電源電路的設(shè)計(jì)

差分ADC中不同電阻容差對(duì)THD性能的影響

DC1384A-A,演示電路采用帶有SPI接口的16位高性能差分模數(shù)轉(zhuǎn)換器LTC2452

如何設(shè)計(jì)一個(gè)適用于12bit流水線ADC采樣保持電路?

一種新型高速采樣保持電路

適用于12 bit流水線ADC采樣保持電路的設(shè)計(jì)

基于二極管橋的兩級(jí)全差分跟蹤保持電路的設(shè)計(jì)

高性能低功耗的采樣保持電路的設(shè)計(jì)與實(shí)現(xiàn)

采用全差分結(jié)構(gòu)的高性能采樣/保持電路的設(shè)計(jì)

采用全差分結(jié)構(gòu)和增益自舉運(yùn)算放大器實(shí)現(xiàn)采樣/保持電路的設(shè)計(jì)

應(yīng)用于電機(jī)驅(qū)動(dòng)的隔離運(yùn)放單端和差分輸出對(duì)采樣性能的影響

OPA1632高性能、全差分音頻運(yùn)算放大器數(shù)據(jù)表

OPA1633高性能、全差分音頻運(yùn)算放大器數(shù)據(jù)表

采用全差分flip-around結(jié)構(gòu)的高性能采樣保持電路

采用全差分flip-around結(jié)構(gòu)的高性能采樣保持電路

評(píng)論