設計工程師通常在FPGA上實現(xiàn)FIFO(先進先出寄存器)的時候,都會使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對性變差,某些情況下會變得不方便或者將增加硬件成本。此時,需要進行自行FIFO設計。本文提供了一種基于信元的FIFO設計方法以供設計者在適當?shù)臅r候選用。這種方法也適合于不定長包的處理。

FIFO在數(shù)字通訊芯片領域中有兩個主要的作用,緩沖數(shù)據(jù)和隔離時鐘。對于FIFO的設計,最關鍵的問題是如何實現(xiàn)RAM的讀寫雙方的信息交換。一般情況下,設計者都直接調用廠商為自己的FPGA專門打造的FIFO核。基本單元是FIFO所使用的RAM的一次讀寫操作的最小單元,如一個字節(jié),一個字或者是一個雙字。所謂操作粒度,即FIFO的讀寫雙方的信息交換是基于這些基本單元。

ATM應用中的FIFO設計

以ATM的設計為例,在ATM的相關設計中,設計者則更多希望一個FIFO對外給出的信息是“現(xiàn)在FIFO中還剩下幾個信元”。要實現(xiàn)這一功能通常有兩種方法:

1. 調用廠商提供的以操作粒度為基本單元的通用FIFO,然后在這個FIFO的外面再加上一個“套子”。這個套子里面設計一些計數(shù)器,根據(jù)計數(shù)內容對外提供相應的信息。

2. 設計操作粒度為信元的定制FIFO。這樣對外直接提供設計者最希望得到的信息,即FIFO中還有多少個信元。

設定FIFO最多可以存放4個信元。基本單元為字節(jié),因此RAM的數(shù)據(jù)寬度為8位,一個信元的長度為53字節(jié)。

把RAM分成4個信元區(qū)域,讀寫地址的高二位指明信元區(qū)域,低六位指明信元區(qū)域內的字節(jié)地址,這樣組合成8位讀寫地址。讀寫雙方的信息交換是互相通知對方還有多少個信元在FIFO中。讀寫雙方都擁有自己的記分牌(Scoreboard),這個記分牌可以由一個四位的寄存器來實現(xiàn),每一位對應一個信元區(qū)域。當一個信元區(qū)域中有一個完整的信元的時候,記分牌的相應的寄存器被設置為‘1’,否則為‘0’。讀出方讀出一個信元,修改自己記分牌的動作叫做清位。寫入方寫入一個完整信元,修改自己記分牌的動作叫置位。

從邏輯上說,只需要讀出方把自己的記分牌的信息(清位信息)傳送給寫入方,同時寫入方把自己的記分牌的信息(置位信息)傳送給讀出方就可以了,即只要構成兩條邏輯通道就可以滿足需求。但是,在硬件上的實現(xiàn)卻要比這種只從邏輯上的思考要復雜。由于讀寫雙方有可能處在不同的時鐘域,所以當讀寫雙方交換信息的時候就需要處理信號采樣的亞穩(wěn)態(tài)情況。我們使用下面的方法來處理信號亞穩(wěn)態(tài)。

消除信號亞穩(wěn)態(tài)

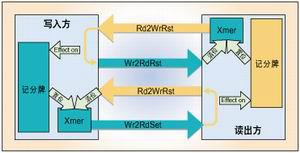

在讀、寫入方之間建立下面的四條單向數(shù)據(jù)通道:傳送寫入方到讀出方的置位信息(Wr2RdSet);寫入方到讀出方的清位信息(Wr2RdRst);讀出方到寫入方的清位信息(Rd2WrRst);讀出方到寫入方的置位信息(Rd2WrSet)。由于讀出方只發(fā)生清位信息,而寫入方只發(fā)生置位信息,所以信息本身只有兩個。四條通道可以被劃分為兩個信息組:一個組(Rd2WrRst和Wr2RdRst)傳遞清位信息,叫清位信息組;一個組(Wr2RdSet和Rd2WrSet)傳遞置位信息,叫置位信息組。讀出方使用清位信息組,寫入方使用置位信息組。這樣做的目的是為了建立起一個穩(wěn)定的握手機制。在讀出方設置一個專門的發(fā)送電路,當此發(fā)送電路通過Rd2WrRst發(fā)出了清位信息后,等待寫入方通過Wr2RdRst通道送回關于這個信息被接收的確認。當收到這個信息的確認后,讀出方發(fā)送電路復位。同樣的,寫入方也有一個發(fā)送電路,操作過程同讀出方一致,無非是使用置位信息組。這兩個發(fā)送電路都各由四個寄存器組成,一位對應一個信元區(qū)域。

為了解決Rd2WrRst進入寫入方時引起的信號亞穩(wěn)態(tài),需要在寫入方設置一個專門消除亞穩(wěn)態(tài)的電路模塊。根據(jù)Rd2WrRst和Rd2WrSet特點不一樣,這個模塊有多種設計方法,但是其宗旨都是使用連續(xù)兩次采樣的方式。

這里介紹一種比較簡單的方法。在設計的時候,把Rd2WrRst和Rd2WrSet的信號都設計為電平方式,即當讀出方要發(fā)送一個信元區(qū)域的清位信息的時候,就把Rd2WrRst信號通道里對應的信元區(qū)域位設置為‘1’。這個‘1’電平一直保持到寫入方的確認到達。當這個‘1’電平被寫入方采樣的時候,由于‘1’同步于讀出方的時鐘,所以很有可能會產(chǎn)生寫入方第一次采樣為一個不確切值,即通常意義上的亞穩(wěn)態(tài)狀態(tài)。但是,由于讀出方一直保持‘1’電平,所以寫時鐘在第二次采樣的時候就會得到一個穩(wěn)定的采樣樣本,從而消除了Rd2WrRst的亞穩(wěn)態(tài)。對于解決Wr2RdSet進入讀出方的時候引起的信號亞穩(wěn)態(tài)的方法和讀出方一樣。

對于Rd2WrSet通道里面的信息,其實是讀出方給寫入方的置位確認。這個信號的源頭是寫入方發(fā)出的Wr2RdSet,讀出方對Wr2RdSet不做任何處理,只是單純地把它里面的信息拷貝到Rd2WrSet通道并回送寫入方,當Rd2WrSet進入寫入方的時候,進入消除亞穩(wěn)態(tài)電路,最后復位寫入方的發(fā)送電路。對于Wr2RdRst通道里面的信息操作也和Rd2WrSet的信息一樣。整個電路的結構如圖所示。

對于信元字節(jié)的計數(shù),和通常的方式一樣,發(fā)生在FIFO的外部,外部的電路需要為FIFO提供基于信元字節(jié)計數(shù)到信元尾的信息。這個信息用來使得FIFO的讀寫地址指針從一個信元區(qū)域跳到下一個信元區(qū)域。FIFO向外部電路提供FIFO有多少個信元的信息。這個信息加上外部電路自己產(chǎn)生的計數(shù)信息,可以知道FIFO是否將滿,F(xiàn)IFO是否將空等一系列信息。

通過上面的描述,可以看到外部電路能夠非常自由地控制FIFO的讀寫地址的變化,這是通用FIFO所不具備的功能。由于FIFO給出的是信元的信息,設計者在做有關UTOPIA協(xié)議的電路的時候,可以很方便地使用這個信息。同時,如果設計需要UTOPIA的查錯功能,這樣的情況更需要外部電路能控制FIFO的地址變化。從而使得寫地址指針回跳以覆蓋原先寫入的數(shù)據(jù)。顯然,這一功能也是通用FIFO很難實現(xiàn)的。

本文小結

對于這樣的FIFO應用還可以延伸到對于非定長包的處理,比如說以太包。由于以太包的特點,要在FPGA中完全存儲一個以太包需要的硬件資源很大,所以,有時候對于以太包的處理都會先把其分為固定長的數(shù)據(jù)塊,并把每一數(shù)據(jù)塊伴以相應的標識以識別他們是屬于哪一個以太包。這樣一來,就變成了對固定長數(shù)據(jù)塊的處理。因此,上面所述的FIFO的設計方法又可以用來緩存以太包。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601808 -

寄存器

+關注

關注

31文章

5317瀏覽量

120002 -

RAM

+關注

關注

8文章

1367瀏覽量

114527

發(fā)布評論請先 登錄

相關推薦

基于信元的FIFO設計如何在FPGA上實現(xiàn)?

異步FIFO結構及FPGA設計

基于PCI接口芯片外擴FIFO的FPGA實現(xiàn)

在FPGA中基于信元的FIFO設計方法實戰(zhàn)方法

基于FPGA的FIFO設計和應用

LabVIEW FPGA模塊實現(xiàn)FIFO深度設定

異步FIFO在FPGA與DSP通信中的運用

基于FPGA的FIFO設計和應用

混沌擴頻SPWM最優(yōu)參數(shù)選取方法及其在FPGA上的實時實現(xiàn)_朱少

異步FIFO在FPGA與DSP通信中的應用解析

基于FPGA的異步FIFO設計方法詳解

在FPGA上實現(xiàn)自行FIFO設計的方法

在FPGA上實現(xiàn)自行FIFO設計的方法

評論