1 引言

采用光纖陀螺的捷聯(lián)慣性導(dǎo)航系統(tǒng)是一種極具發(fā)展?jié)摿Φ膶?dǎo)航系統(tǒng),對于其核心部件的光纖陀螺,尤其是中高精度光纖陀螺,環(huán)境溫度帶來的漂移是不容忽視的,因此對系統(tǒng)進行溫度控制很有必要。溫度控制電路是整個溫控系統(tǒng)的硬件基礎(chǔ),其中涉及到溫度采集,與微處理器通信,串口輸出,控制數(shù)模轉(zhuǎn)換芯片等多個組成部分。本文提出一種高效實用的FPGA 接口設(shè)計,它能夠完成協(xié)調(diào)各個組成部分有序工作,準(zhǔn)確、快速實現(xiàn)數(shù)據(jù)傳輸,嚴(yán)格控制信號時序等工作。

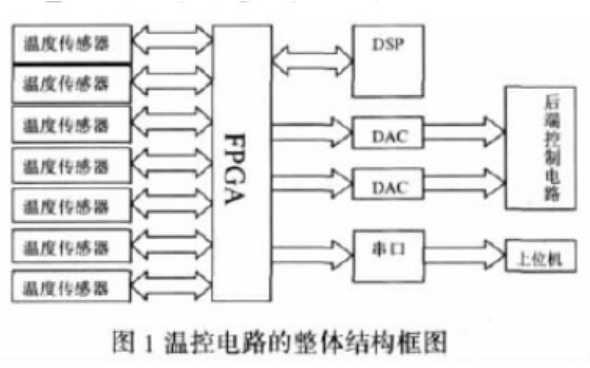

2 溫控電路整體結(jié)構(gòu)

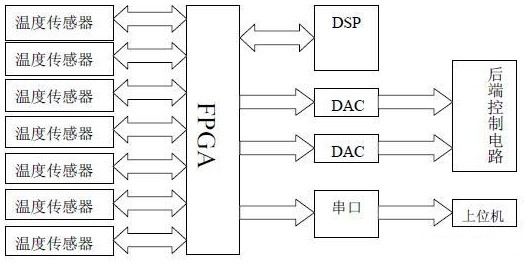

溫控電路的整體結(jié)構(gòu)框圖如圖1 所示。其中包括七路溫度傳感器,DSP, 232 接口芯片,DAC ,后端控制電路,上位機和FPGA 等多個組成部分。FPGA 接口是整個電路的核心。

圖1 溫控電路的整體結(jié)構(gòu)框圖

其中,溫度傳感器采用DALLAS 公司的DS18B20,它采用1-wire 總線協(xié)議,僅需1 根數(shù)據(jù)線進行通信。DSP 采用TI 公司的TMSVC33,它可以實現(xiàn)高速浮點運算。232 接口芯片采用MAXIM 公司的MAX3232,支持高達120kbps 的傳輸速率。DAC 采用TI 公司的TLV5620I,它是通過4 條串行信號控制的8 位4 路數(shù)模轉(zhuǎn)換芯片。FPGA 選用ALTERA 公司的ACEX 系列的EP1K100,它時鐘頻率高,具有豐富內(nèi)部資源,提供大量可編程IO 管腳,配置十分方便。基于FPGA 的溫控電路接口在整個電路中具有非常重要的作用。FPGA 本身的高速并行結(jié)構(gòu)為整個電路的性能提供了可靠保證。

3 溫控電路工作流程

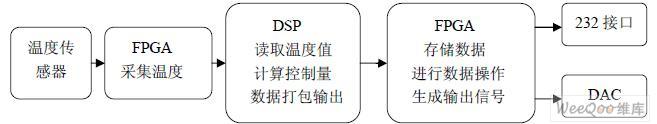

溫控電路的工作流程如圖2 所示。FPGA 與七路溫度傳感器通信,讀取溫度值,并存儲于內(nèi)部存儲器中,每秒更新一次。FPGA 發(fā)送中斷信號通知DSP 讀取FPGA 中存儲的溫度值,DSP 根據(jù)當(dāng)前溫度值和控制算法計算出控制量。而后將溫度值和控制量打包成一幀數(shù)據(jù)發(fā)送給FPGA。FPGA 將DSP 發(fā)送來的數(shù)據(jù)存儲在內(nèi)部存儲器后,對數(shù)據(jù)進行操作,生成輸出信號。

FPGA 一方面將數(shù)據(jù)串行發(fā)送給232 接口芯片,然后通過232 串口發(fā)送給上位機。上位機可通過監(jiān)視軟件實時觀測溫度值和控制量的變化情況,方便系統(tǒng)調(diào)試與*估;另一方面從數(shù)據(jù)中提取出控制量,將其串行輸出到DAC,數(shù)字控制信號經(jīng)過DA 轉(zhuǎn)換后輸出模擬控制電壓到后端控制電路,實現(xiàn)對七路溫度的閉環(huán)控制。

圖2 溫控電路的工作流程

4 FPGA 與外圍電路之間的通信接口

FPGA 與外圍電路之間的通信接口主要包括與溫度傳感器,DSP,232 接口芯片和DAC的通信接口四個部分。

(1) 與溫度傳感器的通信接口

本方案的溫度傳感器采用DS18B20,它通過硬件非常簡單的1-wire 總線通信,由于硬件簡單所以通信協(xié)議比較復(fù)雜。要實現(xiàn)與它的通信接口將占用大量FPGA 片內(nèi)資源,而且本方案要進行七路溫度采集,因此優(yōu)化程序設(shè)計,減少冗余,節(jié)省資源顯得尤為重要。

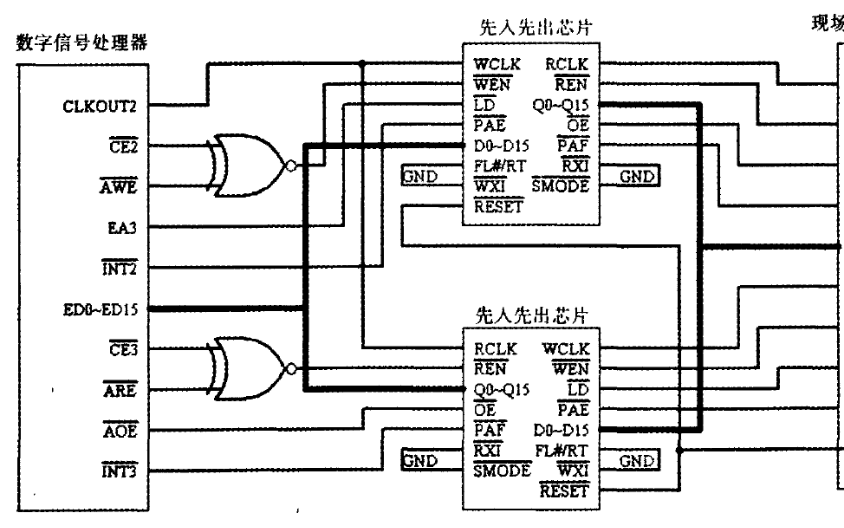

(2) 與DSP 的通信接口

DSP 與FPGA 的組合已經(jīng)成為當(dāng)今數(shù)字電路中非常流行的模式。FPGA 非常適合與DSP配合。本方案中,DSP 與FPGA 的通信接口主要由數(shù)據(jù)總線,地址總線和一些控制信號組成。FPGA 和DSP 之間由8 位數(shù)據(jù)總線連接,數(shù)據(jù)以字節(jié)形式并行傳輸。DSP 通過地址總線對FPGA的片內(nèi)資源尋址。控制信號主要包括復(fù)位信號,中斷信號和讀寫信號。

(3) 與232 接口芯片的通信接口

FPGA 與232 接口芯片的通信是通過收發(fā)兩條數(shù)據(jù)線實現(xiàn)的。本方案中,只存在溫控系統(tǒng)到上位機的單向數(shù)據(jù)傳輸,故僅需一條發(fā)送數(shù)據(jù)線就可以完成與232 接口芯片的通信。

(4) 與DAC 的通信接口

本方案選用TI 公司的TLV5620I 芯片作為DAC。它是8 位4 路電壓數(shù)模轉(zhuǎn)換器。對于它的數(shù)字控制基于由4 條信號線組成的串行總線。包括CLK,DATA,LOAD 和LDAC 四種信號。

5 FPGA 的邏輯設(shè)計

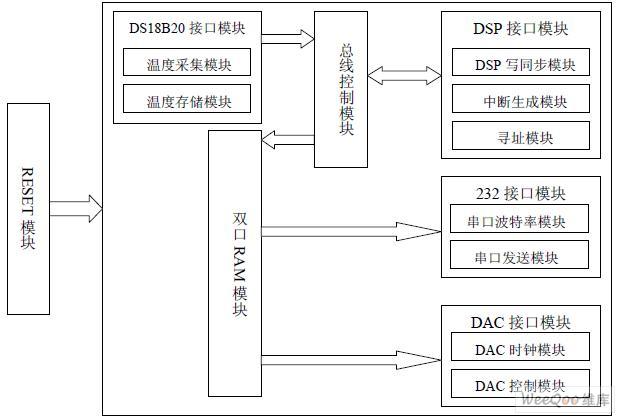

在溫控電路的總體方案,硬件結(jié)構(gòu),工作流程和接口協(xié)議都確定后,就可以進行FPGA的邏輯設(shè)計了。FPGA 的邏輯設(shè)計是整個溫控電路接口設(shè)計的重中之重。它基于verilog 硬件描述語言。良好的FPGA 邏輯設(shè)計應(yīng)該是時序清晰,運行穩(wěn)定,結(jié)果明確和節(jié)省資源的。它能夠保證整個系統(tǒng)的可靠,穩(wěn)定和高效。FPGA 的邏輯模塊圖如圖3 所示。FPGA 內(nèi)部邏輯大致分為RESET 模塊,DS18B20 接口模塊,總線控制模塊,DSP 接口模塊,雙口RAM 模塊,232 接口模塊和DAC 接口模塊等幾部分。

圖3 FPGA 的邏輯模塊圖

(1)RESET 模塊

該模塊生成全局復(fù)位信號。是所有模塊中優(yōu)先級最高的。系統(tǒng)上電后,該模塊將復(fù)位信號拉低并持續(xù)1 秒而后拉高,對DSP 和FPGA 內(nèi)部其他模塊進行復(fù)位。

(2)DS18B20 接口模塊

該模塊用于實現(xiàn)與DS18B20 通信,讀取并存儲溫度值。它包含2 個子模塊。

一、溫度采集模塊

該模塊實現(xiàn)與DS18B20 的通信協(xié)議。首先通過一個初始化序列對DS18B20 進行初始化,包括一個由主機發(fā)出的復(fù)位脈沖和其后由從機發(fā)出的存在脈沖。探測到存在脈沖之后,代表初始化完成,模塊將發(fā)送ROM 操作命令。本方案中,執(zhí)行SKIP ROM 跳過ROM 匹配。之后將發(fā)送存儲器操作命令。溫度轉(zhuǎn)化和讀取溫度就在這部分完成。其中每一次讀寫操作都需要嚴(yán)格按照DS18B20 的讀寫時隙進行。該模塊復(fù)雜程度高和占用資源多,是整個FPGA 中的重要模塊。本方案一共有七路溫度采集模塊,它們的并行結(jié)構(gòu)使得系統(tǒng)可以方便地實現(xiàn)對七路溫度的實時監(jiān)控。

二、溫度存儲模塊

該模塊的主要構(gòu)成部分是一個14*8 位存儲器,用于存儲七路溫度數(shù)值,每一路數(shù)值需要2 個8 位寄存器存放。存儲完畢后,等待DSP 讀取。

(3)DSP 接口模塊

該模塊主要用于與DSP 進行通信。它包含3 個子模塊。

一、DSP 寫信號同步模塊

DSP 的數(shù)據(jù)寫入在寫信號控制下完成。由于DSP 和FPGA 采用不同的時鐘源,所以DSP產(chǎn)生的寫信號無法和FPGA 的主時鐘同步。這樣就會導(dǎo)致寫數(shù)據(jù)錯誤。該模塊用于將DSP 寫信號與FPGA 的主時鐘同步。

二、中斷生成模塊

由于本方案中,溫度值每秒更新一次。在溫度值更新后,通過中斷信號通知DSP 讀取溫度值。該模塊用于生成周期為1 秒的中斷脈沖。

三、尋址模塊

該模塊對FPGA 片內(nèi)資源進行編址,由DSP 的地址總線控制尋址。準(zhǔn)確讀寫所需的數(shù)據(jù)。

(4)總線控制模塊

DSP 和FPGA 之間的數(shù)據(jù)總線是雙向總線,總線控制模塊用于控制總線的數(shù)據(jù)流向。當(dāng)DSP 從FPGA 中讀取溫度值時,總線控制模塊將溫度存儲模塊和數(shù)據(jù)總線相連,輸出數(shù)據(jù)。當(dāng)DSP 向FPGA 中寫數(shù)據(jù)時,總線控制模塊將數(shù)據(jù)總線和雙口RAM 模塊相連,輸入數(shù)據(jù)。

(5)雙口RAM 模塊

該模塊主要實現(xiàn)以下三個功能:當(dāng)DSP 寫數(shù)據(jù)時,將數(shù)據(jù)存儲于內(nèi)部存儲器中;當(dāng)數(shù)據(jù)存儲完畢后,將其中的控制量發(fā)送給DAC 控制模塊;與串口發(fā)送模塊通信,將所有數(shù)據(jù)依次串行輸出。

(6) 232 接口模塊

該模塊用于實現(xiàn)串口數(shù)據(jù)輸出,它包含2 個子模塊:

一、串口波特率模塊

串口通信協(xié)議要求數(shù)據(jù)收發(fā)雙方有相同的波特率。該模塊用于設(shè)定串口通信波特率。

二、串口發(fā)送模塊

雙口RAM 模塊將數(shù)據(jù)存儲完畢后,將給串口發(fā)送模塊一個標(biāo)志信號。串口發(fā)送模塊接到此信號后,依次將雙口RAM 模塊中存儲的數(shù)據(jù)串行輸出。

(7)DAC 接口模塊

該模塊包含2 個子模塊:

一、DAC 時鐘模塊

DAC 需要特定頻率范圍的時鐘來驅(qū)動。該模塊用于生成驅(qū)動DAC 的時鐘信號。

二、DAC 控制模塊

該模塊用于生成DAC 控制信號。它的基本原理是將雙口RAM 模塊輸出的7 路控制量存儲在內(nèi)部存儲器,然后根據(jù)DAC 的接口協(xié)議生成CLK,DATA,LOAD 和LDAC 等控制信號,這些信號將驅(qū)動DAC 的工作,將數(shù)字控制量轉(zhuǎn)換成模擬電壓值。

圖4 溫度控制電路

6 結(jié)束語

FPGA 接口設(shè)計需要綜合考慮硬件連接,工作流程,接口協(xié)議和邏輯模塊等多方面因素,是一項系統(tǒng)工程。本文分別從以上幾方面介紹了基于FPGA 的光纖陀螺慣導(dǎo)系統(tǒng)溫控電路接口設(shè)計,該設(shè)計目前已應(yīng)用于實際系統(tǒng)中。經(jīng)過驗證,接口滿足系統(tǒng)要求,工作狀態(tài)良好。本文所述的FPGA 接口設(shè)計方案是可靠,穩(wěn)定和高效的。可為其他相關(guān)應(yīng)用提供有益的借鑒。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21671瀏覽量

601895 -

溫度傳感器

+關(guān)注

關(guān)注

48文章

2917瀏覽量

155889 -

微處理器

+關(guān)注

關(guān)注

11文章

2247瀏覽量

82322

發(fā)布評論請先 登錄

相關(guān)推薦

學(xué)慣導(dǎo)的人肯定會喜歡的兩本書 (很難找)

我用adis16365做一款捷聯(lián)慣導(dǎo), 陀螺漂移出現(xiàn)時間問題,是電路設(shè)計有問題嗎?

一種基于FPGA的光纖陀螺慣導(dǎo)系統(tǒng)溫控電路接口設(shè)計

怎么實現(xiàn)基于FPGA的數(shù)字閉環(huán)光纖陀螺儀模擬表頭設(shè)計?

光纖陀螺捷聯(lián)慣導(dǎo)系統(tǒng)中數(shù)據(jù)采集單元的設(shè)計與實現(xiàn)

基于FPGA的慣導(dǎo)系統(tǒng)溫控電路接口設(shè)計

基于USB接口的激光陀螺慣導(dǎo)系統(tǒng)數(shù)據(jù)通訊

基于DSP的星載光纖陀螺數(shù)據(jù)采集電路設(shè)計

捷聯(lián)慣導(dǎo)系統(tǒng)中微機械陀螺測試參數(shù)的分析與標(biāo)定

如何實現(xiàn)光纖陀螺慣導(dǎo)系統(tǒng)FPGA接口的設(shè)計

如何實現(xiàn)光纖陀螺信號處理電路中的FPGA與DSP的接口方法

光纖陀螺慣導(dǎo)系統(tǒng)的FPGA接口電路設(shè)計

光纖陀螺慣導(dǎo)系統(tǒng)的FPGA接口電路設(shè)計

評論