引言

隨著現代科學技術的日益發展,顆粒尺寸及其分布在諸如石油、冶金、制藥、建材等領域占據著越來越重要的地位。激光粒度儀就是用來測量微小顆粒尺寸及其分布的儀器,其基本原理是光的衍射理論。數據采集系統對激光粒度儀的光電探測器上光能信號的采集速度是激光粒度儀的性能指標之一,一般來說采集速度越快測量結果的準確性、重復性和穩定性越好[2]。隨著各種新型光電探測器的不斷出現,原有的數據采集系統需要重新設計升級。在新的設計方案中,數據采集系統的模擬通道容量增加到了 112路,并且系統的采集速度也有了大幅度的提高。

FPGA具有硬件資源豐富、設計靈活等特點,適用于數據通訊、數據采集和系統控制中,特別是它的并行結構和算術運算的特點,已越來越受到科技開發人員的青睞,被廣泛應用到數據信號處理當中。對本系統而言, FPGA作為一種可編程、可重配置的數字集成電路,為實現系統的設計目標提供了有力的保證。

1 系統硬件設計

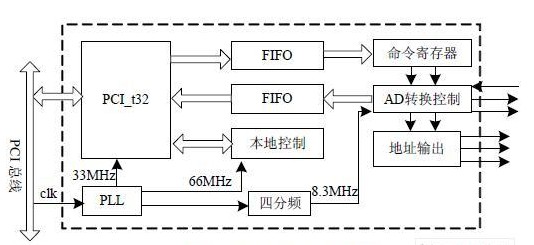

根據激光粒度儀的應用場合,本數據采集系統采用單通道采集的方案,它主要由模擬部分、數字部分和接口部分三部分組成。其中模擬部分包括光電探測器、電信號放大、多路選通、信號調理和 12位 AD轉換,數字部分則完全在 FPGA內部實現,接口部分主要是計算機的 PCI總線接口。系統組成框圖如圖 1所示。

光電探測器電信號放大

激光粒度儀所用的光電探測器是由多個同心的光敏環組成的,每一光敏環輸出的模擬電信號反映了照射到該環上的光能量大小。隨著對激光粒度測量研究的不斷深入,天津大學研制的 LSA系列激光粒度儀的光電探測器組件,其模擬輸出已經發展到 96路之多[3]。為實現對這么多路模擬信號的采集,多路選通采用七片 16選 1模擬開關 DG406和一片 8 選 1模擬開關 MAX308組成雙層級聯結構,共可容納 112路模擬信號,它的地址信號是由 FPGA提供的。AD轉換芯片是數據采集系統的關鍵器件,采用 ADI公司的 12位逐次逼近型模數轉換芯片 AD7321,在本文中該芯片使用其內部的 2.5V參考電壓,模擬輸入范圍選擇為 0~10V,它使用由 FPGA分頻產生的 8.3MHz時鐘信號,這樣該芯片可在 2μs內完成一次模數轉換。若連續兩次采樣間隔的時間設置為 2μs,則系統的數據平均傳輸速率可達到3Mbps。

2 系統軟件設計

2.1 FPGA內部邏輯設計

本文采用了片上系統的設計理念,在 FPGA內部設計了所有所需的數字邏輯,可以實現數據采集控制、數據存儲和 PCI接口方式的數據傳輸等功能。在本方案中,系統初始化后,首先上位機將采集的參數信息(模擬通道數、采樣方式、AD7321工作模式等等)通過 PCI總線送給 FPGA中,FPGA再根據這些參數信息控制多路開關和 AD7321的工作,完成數據采集任務。采集過程中 FPGA將 AD轉換得到的數據存入其內部的 FIFO中,當 FIFO快滿時,它向上位機產生中斷,上位機再通過 PCI總線讀取 FIFO中的數據。

根據以上的設計思想,整個 FPGA內部邏輯的設計框圖如圖 2所示。本文中 FPGA選用 ALTERA公司的 EP2C5Q208C7芯片,采用自頂向下的設計方法,使用 Quartus II 7.0 等相關軟件進行硬件代碼的開發。下面給出各模塊的設計過程。

1)PCI_t32模塊。該模塊是采用 ALTERA公司的 32位 PCI TARGET接口宏核邏輯,它支持 PCI配置空間讀寫、內存方式讀寫和 I/O方式讀寫,支持可參數化的配置寄存器,具有奇偶校驗功能,能提供靈活的本地端接口,可以將復雜的、電氣和時序要求高的 PCI總線邏輯轉換為易于操作的本地接口邏輯[4]。

2)本地控制模塊。該模塊主要由一個能根據 PCI_t32的控制信號和 FIFO的狀態跳轉的有限狀態機實現。它主要負責控制 PCI_t32和 FIFO之間的數據傳送以及協調數據傳輸路徑上其它相關模塊的工作。當 FIFO快滿時,該模塊將產生中斷信號通知上位機讀取 FIFO中的數據。

3)命令寄存器模塊。該模塊用來保存并譯碼由計算機傳來的 16位命令字,配置 AD轉換控制模塊和地址輸出模塊的工作方式。這 16位命令字包含要采集的模擬通道數、AD7321工作模式和是否允許硬件中斷等信息。 4)AD轉換控制模塊。該模塊可輸出 AD7321所需的 SPI總線接口、片選信號和 8.3MHz時鐘信號,其內部主要由一個狀態機和兩個 16位移位寄存器組成。其中移位寄存器可以將 AD7321送來的 16位串行數據轉換為并行數據存入 FIFO中,也可以將命令寄存器模塊中的配置數據串行的發送給 AD7321芯片,狀態機將兩次 AD轉換的間隔時間設置為 2μs。

5)地址輸出模塊。該模塊提供多路模擬開關的片選和地址信號,其內部主要由一個地址計數器組成,當 AD轉換控制模塊完成一路數據的采集時它會自動加 1。 6)PLL和四分頻模塊。 PLL是 FPGA的模擬鎖相環,它工作于 Normal模式下,給其他模塊提供全局時鐘信號。四分頻模塊用來對 33MHz的時鐘信號四分頻,產生 AD轉換控制模塊所需的 8.3MHz時鐘。

在設計中需要特別注意的是異步時鐘域之間的數據同步問題,尤其是 AD轉換控制模塊和 FIFO之間的數據傳遞。本文中參考了通常所說的用寄存器打兩次的方法,在 33MHz的時鐘域中采用兩個寄存器采樣 AD轉換控制模塊的控制信號,并利用一個同或門檢測兩個寄存器輸出是否一致,再根據同或門的輸出信號就可以實現這兩個模塊之間的數據傳遞。

2.2 PCI驅動程序設計

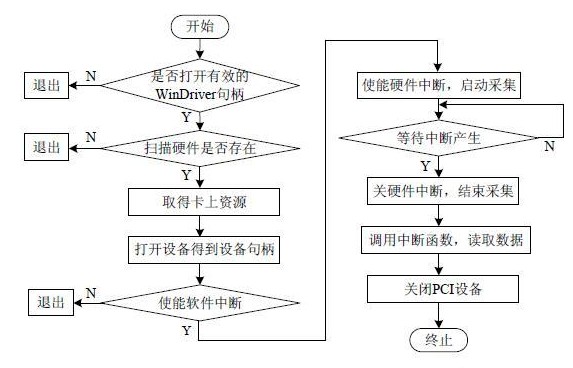

硬件系統一般都需要軟件的支持才能實現系統的設計功能,驅動程序就是控制硬件設備的一組函數。本系統的驅動程序的開發使用的是 Jungo公司的 WinDriver集成開發包,它可以自動生成設備的信息定向文件.INF和系統文件 WINPNP.SYS。利用 WinDriver 9.01開發設備驅動程序時,驅動程序中的所有函數都是工作在用戶態下的,因此不需要熟悉操作系統的內核。本文在 Visual C++ 6.0的平臺下,通過一個動態鏈接庫 wdapi901.dll調用 WinDriver提供的 API函數來編寫設備的驅動程序,實現了用戶程序對硬件的操作。其軟件流程圖如圖 3所示。

3實驗結果與分析

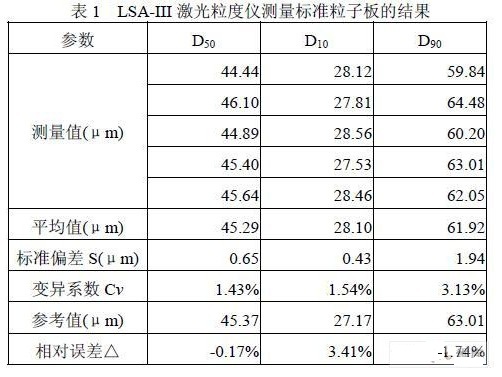

由天津大學研制的 LSA-III型激光粒度儀可測粒徑范圍為 6μm-2000μm,其光電探測器由 32個同心光敏環和 1個位于中心的光敏點組成。由于本系統可以軟件選擇模擬通道數,因此只要將計算機發送到命令寄存器模塊中的命令的模擬通道數改為 33就可以應用到該儀器上。在 LSA-III型激光粒度儀上使用焦距為 300mm的傅立葉物鏡對標準粒子板進行測試,利用 R-R分布模型處理得到的數據,對標準粒子板測量 5次的試驗結果如表 1所示。其中 D50表示小于該直徑的粒子體積占粒子總體積的 50%,D10和 D90的意義與此類似 [5]。變異系數 Cv和相對誤差△是 ISO13320標準的指標,其中 Cv用來衡量測量的重復性,△用來衡量測量的準確性。

由表 1數據可知, D50的變異系數和相對誤差均在1.5%以內, D10和 D90的變異系數和相對誤差均在3.5%以內,符合 ISO13320標準對重復性和準確性的規定。試驗表明該系統在對顆粒粒徑的測量中表現穩定,結果準確,完全滿足了激光粒度測試系統的要求。

4結語

本文創新點:本文以 FPGA為核心為 LSA系列激光粒度儀量身定制的數據采集系統,實現了 PCI總線方式的數據采集與傳輸。系統可在 0-112路范圍內軟件選擇模擬通道的采集路數和 AD7321芯片的工作方式,這使得系統具有了一定的通用性,適應了目前光電探測器越來越復雜的趨勢。將該系統應用到 LSA-III型激光粒度儀上時,系統對光電探測器的采樣速率可達到 7.5Ksps,數據平均傳輸速率可達到 3Mbps。另外,由于設計中貫穿了 SOC的設計理念,系統還具有集成度高、成本低、升級方便、使用靈活等優點。該項目已經在激光粒度儀中得到應用,產生的直接經濟效益達 6萬元。

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601902 -

測試儀

+關注

關注

6文章

3695瀏覽量

54763 -

數據采集

+關注

關注

38文章

5910瀏覽量

113523

發布評論請先 登錄

相關推薦

用于激光掃描測徑儀的數據采集系統設計

基于FPGA的激光粒度儀數據采集系統

全自動激光粒度儀的研制

TD-SCDMA網絡測試儀STM-1數據采集卡的實現

基于FPGA的高速誤碼測試儀的設計

基于FPGA的LSA系列激光粒度測試儀的數據采集系統設計

基于FPGA的LSA系列激光粒度測試儀的數據采集系統設計

評論