引言

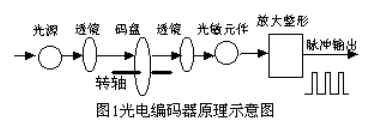

位置編碼器是工業自動控制中重要的反饋環節執行元件。位置編碼器按工作方式分為絕對式和增量式兩種。絕對位置式編碼器的數據輸出一般采用串行通信的方式。位置編碼器的通信速度,在一定程度上影響閉環系統的時間常數。德國IC-Haus公司提出的BiSS(Bidirectional Synchronous Serial)協議是一種新型的可自由使用的開放式同步串行通信協議,使用該協議通信波特率可以達到10Mbps,達到RS422接口總線的波特率上限,是其它一些同類常用串行通信協議(如SSI,EnDat,Hiperface,起止式異步協議)的5倍以上。

注:起止式指一種常用的異步串行通信協議,每幀數據包括1位起始位、5-8位數據位、1(或0)位奇偶校驗位、1(或1.5或2)位停止位。

由表1中可知,BiSS協議通信波特率遠遠高出其它協議,總線連接方式、報警位、協議長度可調整,工業應用靈活性好,無協議產權成本,全數字接口無模擬器件成本。可見,在通信速度、產品適應性、成本等綜合方面,BiSS協議具有很好的發展前景。

1、BiSS協議

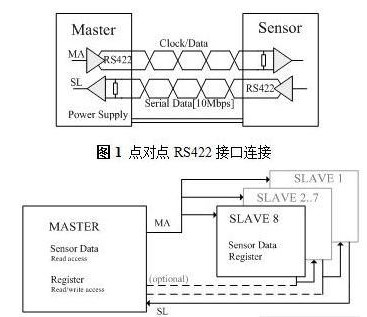

BiSS協議包括讀數模式(sensor mode)和寄存器模式(register mode)兩部分的內容。如圖1、圖2所示,在點對點或總線連接下由主機發送MA(master)信號,編碼器返回SL(slave)信號。SL的返回信號是和MA的時鐘同步的。在寄存器模式下,MA在提供時鐘的同時,需要攜帶寄存器地址、寄存器值等信息,這是通過不同的占空比實現的:當占空比在10%~30%(文中稱為低占空比)時,同時表示數據0;當占空比在70%~90%(文中稱為高占空比)時,同時表示數據1。

1.1 讀數模式

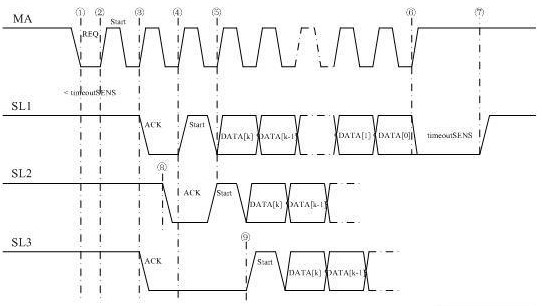

在讀數模式下,通信波特率可達到10Mbps,MA和SL的幀結構如圖3所示。其中,MA的REQ(請求)位的①~②時間長度要小于timeoutSENS(可編程的時間參數),編碼器識別為讀數模式。在MA的每一個時鐘上升沿,SL返回相應的數據位。

實際應用中,長距離的導線傳輸、接口電平轉換芯片等帶來的總線延時(line delay),會有SL2的延遲響應波形。由此可估計總線延時為③~⑧時間長度,即MA時鐘上升沿和SL響應位下降沿的時間長度,相應地延遲采樣時刻,使通信不受總線延時的影響。

編碼器的位置信號需要內部采集,轉換等過程。當編碼器忙不能立刻響應主機的讀數請求時,延遲響應start位,此時為SL3的波形,數據處理帶來的延時為④~⑨時間長度。

可見,在高波特率的通信狀態下,仍能通過估計總線延時和忙延時,準確的進行數據通信。

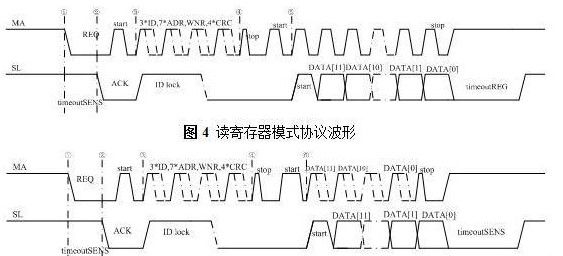

1.2 寄存器模式

在讀寫寄存器模式下,通信波特率相對較低。文中編碼器的寄存器為EEPROM,正常工作上限波特率為250K。MA的REQ位時間長度要大于timeoutSENS,編碼器識別為寄存器模式。寄存器地址序列為③~④波形(讀寄存器、寫寄存器相同),包括3位的ID(編碼器編號)、7位ADR(編碼器地址)、1位WNR(讀寫標志位)和4位CRC(校驗位),同樣使用高低占空比來實現時鐘和數據的同時輸出。

主機輸出寄存器地址序列后,如果是讀寄存器模式,即寄存器地址序列中的WNR位為0,MA繼續輸出時鐘,SL返回寄存器中的數據。如果是寫寄存器模式,即寄存器地址序列中的WNR位為1,MA則繼續輸出高低占空比信號,SL返回寫入的寄存器值,如該值與發送的數據一致,說明寫寄存器操作成功。

位置數據、寄存器數據、寄存器地址后均加有CRC校驗,保證傳送數據的準確性。對于總線連接方式,BiSS協議給出了多編碼器串行連接的讀數方式和寄存器讀寫方式,是上述時序的組合。

2、通信模塊的軟硬件設計

2.1 硬件設計

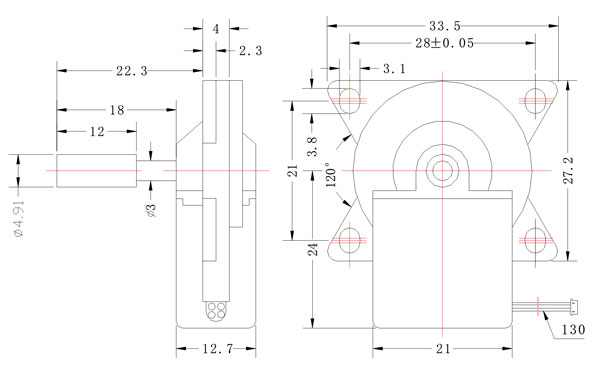

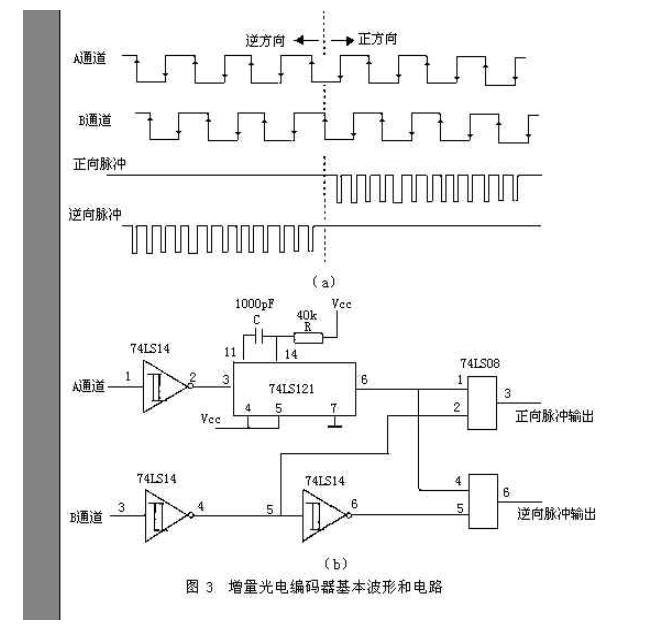

通信模塊基于EP1C12Q240-FPGA設計,對Netzer RE252型號的絕對位置式光電編碼器進行位置讀數,采用點對點連接,RS422差分總線接口使用MAX3460電平轉換芯片。為了提高通信模塊在工業應用中的抗干擾性,接口芯片和FPGA核心模塊之間加入高速光耦HCPL0630進行隔離。輸出接口有并行接口、串行通信接口、增量式等,與上位機通信。

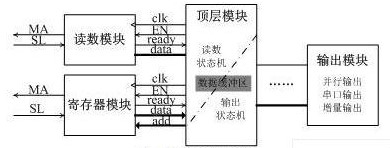

2.2 軟件設計

程序在Quartus II軟件[6]環境下,使用Verilog HDL語言編寫,采用的是自底向上的編寫方式,使用約6000門資源。底層模塊包括讀數模塊、讀寫寄存器模塊。底層模塊的clk時鐘由頂層模塊的鎖相環PLL分頻提供。讀數模塊或者讀寫寄存器模塊在EN置位后,獨占MA線,發送與協議對應的波形,再根據編碼器返回的SL波形采樣識別數據,通過data總線保存到頂層模塊的數據緩沖區。

頂層模塊主要包括兩個狀態機。讀數狀態機根據編碼器的工作時序要求完成寄存器的初始化,然后不斷的讀取編碼器的數據保存到數據緩沖區。輸出狀態機根據指定標志位從數據緩沖區讀取數據,控制以并行、串口、增量式的輸出時序邏輯。

3、實驗結果及對比

quartus II中的signalTap邏輯分析儀可以嵌入到FPGA,觀察管腳電平和內部變量值。圖7所示為編碼器返回14位數據的通信波形。從圖中可見,SL的第一個下降沿即ACK位延遲了約0.65μs,為總線延時。一個完整的讀數操作從-5時刻開始需要約210個采樣點,即4.2μs的時間(4.2μs=210*1/50 MHz,采樣頻率50MHz)。

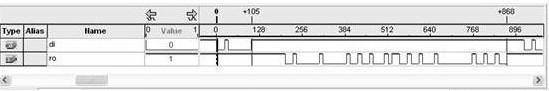

圖8為*AGAWA-TS5667型號的絕對式光電位置編碼器返回17位數據的通信波形,該編碼器采用起止式異步串行通信協議,波特率為2.5M。半雙工通信方式下,一個完整的讀數操作從0時刻di請求開始,到約868時刻ro應答結束,需要約30.4μs的時間(30.4μs=868*1/28.57MHz,采樣頻率28.57MHz)。

BiSS協議下的數據位數可調整,如果把BiSS協議下的數據位數從14位增加到17位,只需增加3個時鐘的時間長度,在10Mbps下為0.3秒。

由此得到,在同樣傳輸17位光電編碼器位置數據的情況下,起止式異步協議耗時30.4μs,而BiSS協議僅耗時4.5μs,通信速度提高了6.75倍。

4、結論

基于BiSS協議的各方面優點,目前已有德國IC-Haus,美國Danaher,以色列Netzer Precision等130多家公司申請并免費使用了BiSS協議,BiSS協議得到了越來越廣泛的應用。同時,BiSS與SSI協議下的接口兼容,方便SSI使用者和廠商系統升級。綜上所述,BiSS協議在降低協議成本、硬件成本,提高通信速度和準確率等綜合方面,是未來編碼器用串行通信協議中一種非常理想的選擇。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602038 -

編碼器

+關注

關注

45文章

3601瀏覽量

134205 -

vhdl

+關注

關注

30文章

816瀏覽量

128082

發布評論請先 登錄

相關推薦

5V BiSS 位置編碼器接口參考設計

5V BiSS位置編碼器硬件接口解決方案

開源硬件-TIDA-00175-5V BiSS 位置編碼器接口 PCB layout 設計

詳解雙向/串行/同步(BiSS)位置編碼器的接口

利用VHDL語言和BiSS協議實現光電編碼器的設計

利用VHDL語言和BiSS協議實現光電編碼器的設計

評論