HDLC(High Level Date Link Control)協議是通信領域中應用最廣泛的協議之一,它是面向比特的高級數據鏈路控制規程,具有差錯檢測功能強大、高效和同步傳輸的特點。目前市場上有很多專用的HDLC芯片,但這些芯片大多控制復雜,通道數目有限;另一方面,專用芯片的使用會有效增大PCB板面積,不利于設備的小型化,而且帶來高成本等問題。

FPGA能對任意數據寬度的信號進行處理,內部的功能模塊可以并行處理。因此,采用FPGA技術設計HDLC協議控制器可以均衡整個系統的負荷,實現多通道的高性能HDLC協議控制器,保證通信的可靠性。同時它還具有設計開發周期短、設計制造成本低、可實時在線檢驗等優點,因此被廣泛用于特殊芯片設計中。本設計中采用Altera公司的EP2C70F672C8芯片來實現HDLC協議控制器。

1 HDLC協議簡介

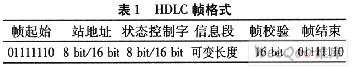

在HDLC通信方式中,所有信息都是以幀的形式傳送,HDLC幀格式,如表1所示。

(1)標志字。

皿LC協議規定,所有信息傳輸必須以—個標志字開始,且以同一個標志字結束,這個標志字是01111110。開始標志到結束標志之間構成—個完整的信息單位,稱為一幀。接收方可以通過搜索01111110來探知幀的開始和結束,以此建立幀同步。在幀與幀之間的空載期,可連續發送標志字來做填充。

(2)信息段及“0”比特插入技術。

HDLC幀的信息長度是可變的,可傳送標志字以外的任意二進制信息。為了確保標志字是獨一無二的,發送方在發送信息時采用“0”比特插入技術,即發送方在發送除標志字符外的所有信息時(包括校驗位),只要遇到連續的5個“1”,就自動插入一個“0”;反之,接收方在接收數據時,只要遇到連續的5個“1”,就自動將其后的“0”刪掉。“0”比特插入和刪除技術也使得’HDLC具有良好的傳輸透明性,任何比特代碼都可傳輸。

(3)地址段及控制段。

地址字段為8位,也可以8的倍數進行擴展,用于標識接收該幀的棧地址;控制字段為8位,發送方的控制字段用來表示命令和響應的類別和功能。

(4)幀校驗。

HDLC采用16位循環冗余校驗碼(CRC-16)進行差錯控制,其生成多項式為x16+x12+x5+1,差錯校驗指對整個幀的內容作CRC循環冗余校驗,即對在糾錯范圍內的錯碼進行糾正,對在校錯范圍內的錯碼進行校驗,但不能糾正。標志位和按透明規則插入的所有“0”不在校驗的范圍內。

2 HDLC協議的FPGA實現

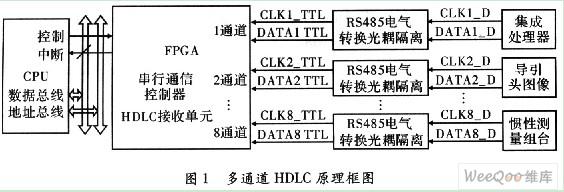

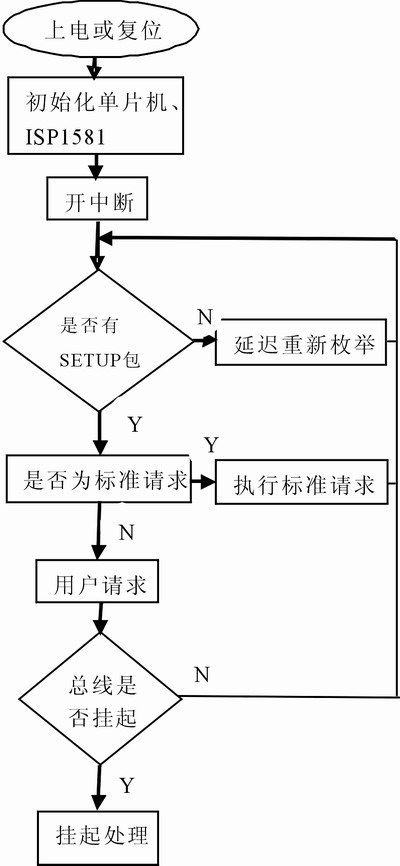

某遙控遙測平臺為確保滿足高速通訊、多通道收發、功能易于擴展配置的任務要求,中心控制器采用了以高性能的ARM7為CPU數據處理核心、采用FPGA設計串行通信控制器來收發多通道HDLC數據的一體化設計。

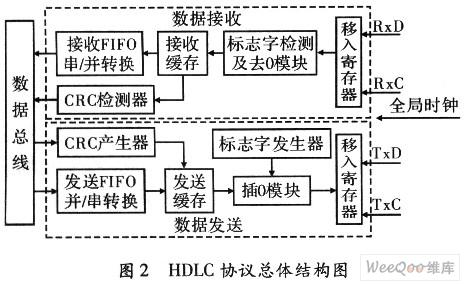

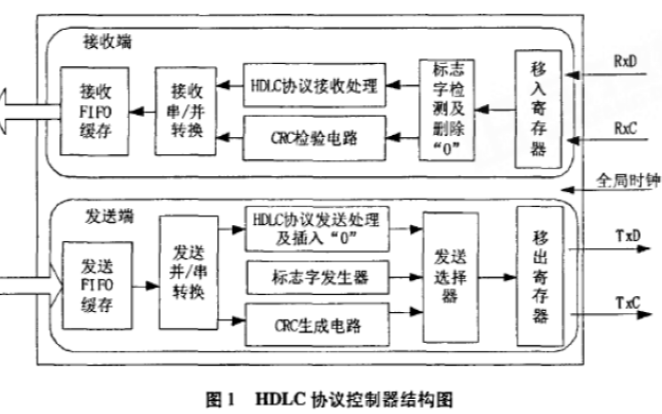

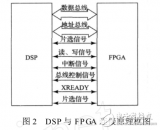

FPGA按照HDLC協議規程,接收并存儲來自集成處理器等8個獨立通道的數字量。系統先將外部輸入的HDLC數據流由RS485電氣特性轉換為TTL電平,在此過程中用光耦進行隔離,以避免與外部設備之間的相互干擾,并且RS485芯片與光耦器件的相關電源使用由電氣供給的獨立5 V和5 V地。 HDLC協議總體結構框圖,如圖2所示,每個控制模塊由時鐘控制、編碼/沖突檢測、發送和接收FIFO等功能模塊組成。在發送方向和接收方向,各有一個128 bit的FIFO,用于串行通道和CPU總線接口之間的數據緩沖。發送是接收的逆過程,這里以HDLC數據接收為例進行說明。

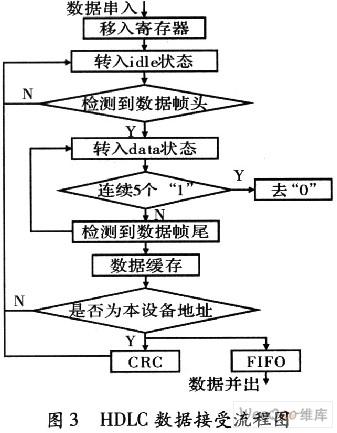

FPGA串行通信控制器接收HDLC數據的原理為:首先,將接收到的數據幀的消息字段和附加的狀態字段移入,然后根據選定的尋址模式,對接收幀中的目的地址進行識別,確認數據幀的發送地址是否為本設備(站地址=77H),是本設備數據幀則進行接收數據并存儲在FIFO中,當接收數據幀結束時,發出中斷信號給ARM系統,請求接收HDLC數據。

目的地址不是本設備的數據幀將被拋棄,流程圖如圖3所示。

3 實驗結果和分析

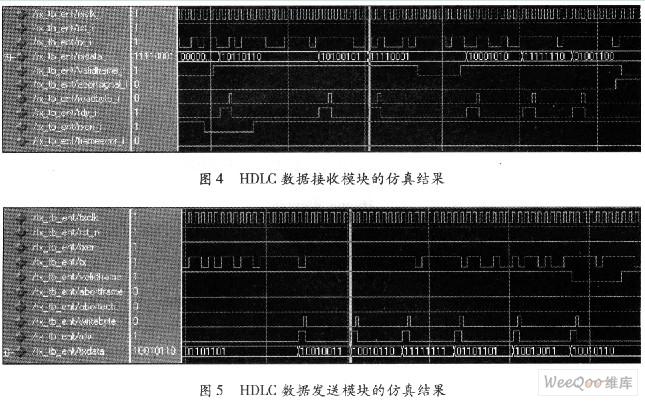

首先,在FPGA中實現一對HDLC數據收發電路,并在對收發電路進行仿真和相關測試。通過在Matlab開發環境下,生成相關的數據文件作為HDLC的數據源,在ModelSim SE 6.1的測試文件中直接調用,最后對比仿真結果和Matlab生成的數據源,可以得到滿意的結果。仿真的測試代碼覆蓋率為100%,仿真結果和數據源完全吻合,可以認定電路的正確性及良好的可靠性。圖4,圖5分別為HDLC數據收發模塊在ModelSim SE 6.1中的仿真圖。

為合理利用FPGA內部的邏輯資源,對設計進行一系列布局布線約束:(1)由前期的論證可知,設計的矛盾主要集中在資源的消耗上,所有模塊的優化目標定位為“Area”,除FIFO外,其他模塊規劃在一起;(2)將FIFO劃分為獨立的模塊;(3)全局時鐘綁定在Global資源上,并/串、串/并模塊中的衍生時鐘,根據和全局時鐘的關系,設定為多周期路徑。

實際數據收發的穩定性和可靠性,也跟單板、溫度等有關系。仿真完成后,在單板上進行飛線,對特定的收發電路進行電氣連接,進行回環測試法,即發送端輸出的數據由其接收端接收回來進行測試。在常溫下,經過30小時的長時間運行測試后,接收和發送的數據做了對比,沒有發現丟數據包和錯數據包的情況。由測試結果可知,該HDLC收發電路的具有穩定性和可靠性。高低溫實驗由于條件所限未進行,單板的溫度特性可由器件的溫度特性大概推知,這里不做討論。

4 結束語

針對某遙控遙測平臺的要求,文中提出了一種基于FPGA的多通道HDLC收發電路設計方案,并利用Altera公司的P2C70F672C8芯片來實現。目前,實現該電路的單板已經完成調試,并成功地應用于整機試驗。實踐表明,該電路實現簡單、可靠性高、使用靈活等優點,具有一定的推廣價值。

-

FPGA

+關注

關注

1626文章

21666瀏覽量

601836 -

芯片

+關注

關注

453文章

50402瀏覽量

421802 -

控制器

+關注

關注

112文章

16203瀏覽量

177401

發布評論請先 登錄

相關推薦

HDLC的DSP與FPGA實現

怎么設計多通道HDLC收發電路?

基于FPGA的多通道HDLC通信系統設計與實現

采用P89C61x2和ISP1581的USB接口電路的設計

基于DSP和FPGA的HDLC協議通訊電路設計

高速多通道數據采集系統的設計與實現

三星ARM處理器S3C4510B的HDLC通道使用及編程

如何使用FPGA實現HDLC協議控制器

采用FPGA與P2C70F672C8芯片實現多通道HDLC收發電路設計

采用FPGA與P2C70F672C8芯片實現多通道HDLC收發電路設計

評論