對基于單體存儲器的FIFO,作為一種數據緩沖器,其數據存放結構和RAM是一致的,只是存取方式有所不同。因RAM中的各存儲單元可被隨機讀寫,故FIFO的隊首位置及隊列長度均可浮動。為此,需要用兩個地址寄存器,分別存儲讀地址(即隊首元素地址)和寫地址(即隊尾元素地址加1)。在讀寫過程中FIFO所存儲的信息并不移動,而是通過改變讀地址或寫地址來指示隊首隊尾。

本32X8 FIFO的設計,采用了雙體存儲器的交替讀寫機制,使得在對其中一個存儲器寫操作的同時可以對另一個存儲器進行讀操作;對其中一個存儲器讀操作的同時可以對另一個存儲器進行寫操作。實現了高速數據緩沖,速度比單體存儲器的FIFO提高了一倍。

1指針以及滿空信號的產生

空/滿標志的產生是FIFO的核心部分。如何正確設計此部分的邏輯,直接影響到FIFO的性能。

對于同步FIFO,讀寫指針都指向一個內存的初始位置,每進行一次讀寫操作,相應的指針就遞增一次,指向下一個內存位置。當指針移動到了內存的最后一個位置時,它又重新跳回初始位置。在FIFO非滿或非空的情況下,這個過程將隨著讀寫控制信號的變化一直進行下去。如果FIFO處于空的狀態,下一個讀動作將會導致向下溢出(underflow),一個無效的數據被讀出;同樣,對于一個滿了的FIFO,進行寫動作將會導致向上溢出(overflow),一個有用的數據被新寫入的數據覆蓋。這兩種情況都屬于誤動作,因此需要設置滿和空兩個信號,對滿信號置位表示FIFO處于滿狀態,對滿信號復位表示FIFO非滿,還有空間可以寫入數據;對空信號置位表示FIFO處于空狀態,對空信號復位表示FIFO非空,還有有效的數據可以讀出。當讀指針和寫指針相等也就是指向同一個內存位置的時候,FIFO可能處于滿或空兩種狀態。可以通過不同的方法判斷或區分FIFO究竟是處于滿狀態還是空狀態,也就是究竟是寫指針從后趕上了讀指針,還是讀指針從后趕上了寫指針。

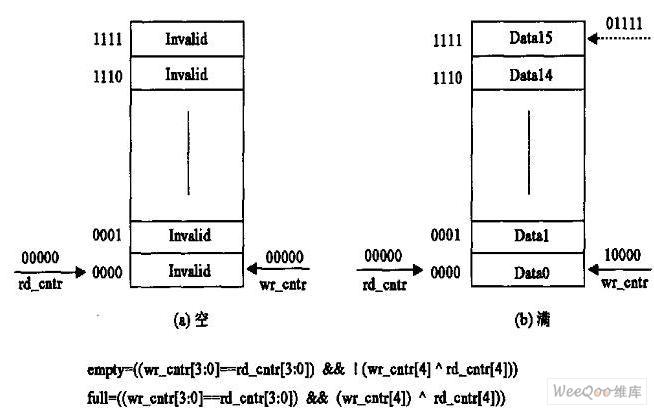

本文所應用的方法是分別將讀、寫地址寄存器擴展一位,將最高位設置為狀態位,其余低位作為地址位,指針由地址位以及狀態位組成。巧妙地應用地址位和狀態位的結合實現對空、滿標志位的控制。當讀寫指針的地址位和狀態位全部吻合的時候,讀寫指針經歷了相同次數的循環移動,也就是說,FIFO處于空狀態(圖1(a));如果讀寫指針的地址位相同而狀態位相反,寫指針比讀指針多循環一次,標志FIFO處于滿狀態(圖1(b))。

圖1FIFO處于的狀態

232X8FIFO系統結構

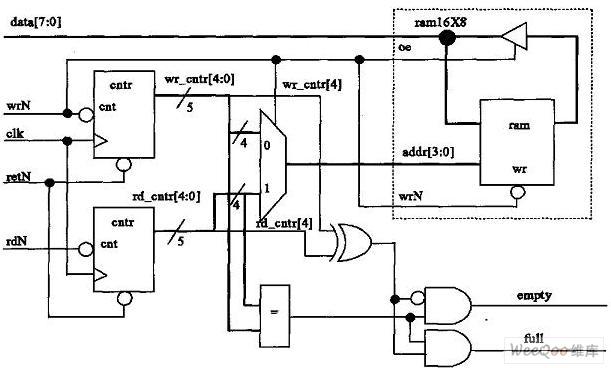

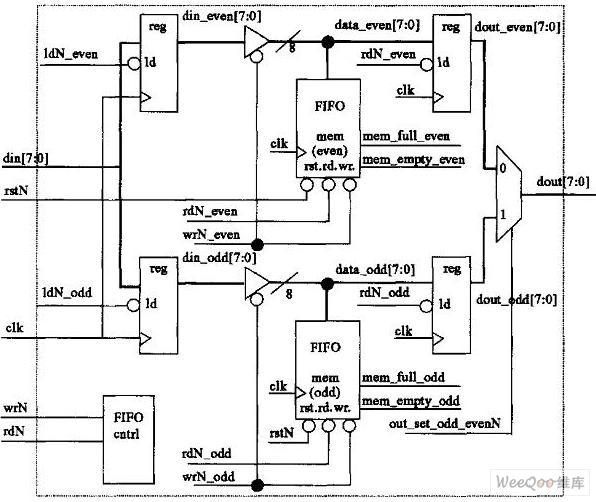

本文介紹的32X8FIFO設計采用了雙體存儲器(FIFOMemory)結構(如圖2)。每個FIFOMemery中都有一個16X8的RAM,rd-cntr3: 和wr-cntr3: 分別作為讀、寫地址,rd-cntr和wr-cntr分別作為讀、寫狀態位。對整個系統,當寫信號(wrN)有效,數據將寫入FIFO,且交替寫入這兩個分立的存儲器。當讀信號(rdN)有效,數據將被讀出FIFO,且交替從這兩個分立的存儲器讀出。對基于單體存儲器的FIFO,在讀操作的同時不能有任何的寫操作,只能在讀操作結束后再進行寫操作。本文應用的交替讀寫機制使得32X8 FIFO具有可以同時讀寫的能力,即對一個存儲器讀操作的同時可以對另一個存儲器寫操作;對一個存儲器寫操作的同時可以對另一個存儲器讀操作。32X8 FIFO Data Path的結構框圖如圖3所示。其結構中有兩個分立的存儲器FIFOmem(even)和FIFOmem(odd)。FIFO cntrl模塊控制對這兩個分立存儲器的讀、寫操作。而整個系統的空、滿標志位分別由FIFOmem(even)和FIFOmem(odd)中的空、滿標志位mem_full_even、mem_empty_even、mem_full_odd和mem_empty_odd來實現。其中rdN和wrN為整個系統的讀寫控制信號,rstN為FIFO復位信號。同時可以看出32X8 FIFO共有3個周期的延時:輸入寄存器,FIFOMemery和輸出寄存器延時,存取速度快。

圖2FIFOMemory結構框圖

圖332X8FIFODataPath結構框圖

332X8FIFO的Verilog HDL實現

硬件描述語言Verilog HDL是一種廣泛應用于集成電路設計的高層次描述語言,適合行為級、寄存器傳輸級和門級等多層次的設計和描述,并且具有簡單、易讀、易修改和與工藝無關等優點。因此利用Verilog HDL語言進行電路設計可以節約開發成本和周期。

此32X8FIFO各個部分均采用Verilog HDL代碼實現。限于篇幅,下面僅列出FIFOMemery模塊的程序清單。整個

32X8FIFO設計應用全球著名EDA軟件供應商Synopsys公司的DesignCompiler進行了邏輯綜合,并應用Synopsys公司的仿真軟件VCS做了仿真驗證。(VCS是Synopsys公司的VerilogHDL仿真軟件) FIFO Memery模塊程序清單如下:

module fifo_mem(data,clk,rstN,wrN,rdN,empty,full);

inout [7:0] data;

input clk,rstN,wrN,rdN;

output empty,full;

reg [4:0] _cntr,rd_cntr;

wire [3:0] add;

ram16X8 ram(.data(data),.addr(addr),.wrN(wrN),.oe(wrN));

always @(posedge clk or negedge rstN)

if(!rstN) wr_cntr<=0;

else if (!wrN) wr_cntr<=wr_cntr+1;

always @ (posedge clk or negedge rstN)

if(!rstN) rd_cntr<=0;

else if(!rdN) rd_cntr<=rd_cntr+1;

assign addr=wrN?rd_cntr [3:0]: wr_cntr [3:0];

assign empty=(wr_cntr [3:0] == rd_cntr [3:0])&&!(wr_cntr[4]^rd_cntr[4]);

assign full=(wr_cntr [3:0] ==rd_cntr [3:0])&&(wr_cntr[4]^rd_cntr[4]);

endmodule

4結語

本文通過兩個分立存儲器間的交替讀、寫機制,實現32X8 FIFO的可同時讀、寫功能,提高了數據存取的速度,并且提出了新穎的空、滿標志位的實現方法。采用Verilog HDL硬件描述語言進行電路設計,應用Synopsys公司的DesignCompiler和VCS進行電路綜合和仿真,電路功能得到驗證。

-

ARM

+關注

關注

134文章

9046瀏覽量

366817 -

存儲器

+關注

關注

38文章

7452瀏覽量

163606 -

緩沖器

+關注

關注

6文章

1917瀏覽量

45450

發布評論請先 登錄

相關推薦

基于Verilog HDL語言與雙體存儲器的交替讀寫機制實現32X8 FIFO設計

基于Verilog HDL語言與雙體存儲器的交替讀寫機制實現32X8 FIFO設計

評論