引言

近年來,寬帶接入技術(shù)得到了飛速的發(fā)展,其中非對稱用戶數(shù)字線路技術(shù)(ADSL)能利 用現(xiàn)有的電話網(wǎng)絡(luò)資源,具有投資少見效快等優(yōu)點,成為向B - ISDN 的最佳過渡形式之一。 在ADSL系統(tǒng)中,由數(shù)字用戶接入復(fù)用器(DSLAM)完成ATM的終結(jié)和路由,該模型分為4 層,自上而下分為高層、AAL層、ATM層和物理層,這里高層是指RFC1483及其以上各層, AAL層又分為拆分與組裝子層(SAR)和匯聚子層(CS)兩個子層,ATM層主要完成信元 復(fù)用/解復(fù)用、有關(guān)信元頭的操作以及流控等功能,UTOPIA(ATM的通用測試和操作物理接 口)位于ATM層和物理層之間,規(guī)范ATM層和物理層之間的信號電平和時序定義,物理層 的主要任務(wù)是物理線路編碼和信息傳輸。當(dāng)前,ATM SAR功能和UTOPIA接口由專用通信處 理芯片MPC866處理器來完成,成本較高功能固定,靈活性較差。針對特定的AAL5業(yè)務(wù)采 用FPGA芯片來實現(xiàn)AAL層中SAR子層功能和ATM層功能,,即在通用微處理器的環(huán)境中實 現(xiàn)ATM接口,增強產(chǎn)品的靈活性,同時降低成本,對替代專用通信芯片具有較強的實際意義。

1 ATM 協(xié)議概述

ATM 是一個分組協(xié)議,利用異步傳輸模式規(guī)程,來自不同信源的數(shù)據(jù)經(jīng)由相同的物理 信道發(fā)送,所設(shè)計的協(xié)議滿足不同用戶應(yīng)用的需要。

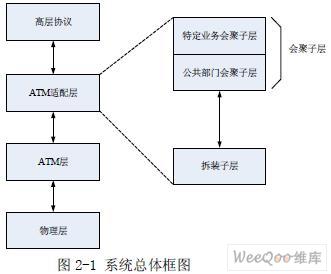

ATM 協(xié)議棧,為了有效地處理不同的業(yè)務(wù),協(xié)議被構(gòu)造為層次體系結(jié)構(gòu),每層實現(xiàn)特 定的功能,圖1-1 顯示了通用的協(xié)議棧。高層協(xié)議包括應(yīng)用層、表示層、傳輸層和網(wǎng)絡(luò)層。 應(yīng)用層的例子有用于傳送文件傳輸協(xié)議、簡單郵件傳送協(xié)議(SMTP)、提供虛擬終端服務(wù) 的Telnet 協(xié)議等,傳輸控制協(xié)議(TCP)和Internet 協(xié)議(IP)則分別是傳輸層協(xié)議和網(wǎng)絡(luò) 層協(xié)議。

ATM 傳送信息的基本載體是ATM 信元,信元長度為53 字節(jié),分為信頭和凈荷兩部分, 信頭為5 字節(jié),凈荷為48 字節(jié)。ATM 層主要完成信元復(fù)用/解復(fù)用,有關(guān)信頭的操作,以 及流量控制。信元復(fù)用/解復(fù)用在ATM 層和物理層的TC 子層接口處完成,發(fā)送端ATM 層 將具有不同VPI/VCI 的信元復(fù)用在一起交給物理層;接收端ATM 層識別物理層送來的信元 的VPI/VCI,并將各信元送到不同的模塊處理,如識別出信令信元就交控制面處理,若為 OAM 等管理信元則交管理面處理。信頭操作指VPI/VCI 翻譯,翻譯的依據(jù)是連接建立時所 分配的VPI、VCI 的值。

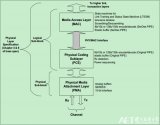

一對一模式下,如何實現(xiàn)物理層-ATM 層-AAL 層間簡單的ATM 協(xié)議,如何滿足備 用鏈路或多種類型的物理層共享一個ATM層的需求,如何在同一ATM層上同時支持AAL1、 無連接數(shù)據(jù)服務(wù)(AAL3/4)和面向連接數(shù)據(jù)服務(wù)?為此,提出了UTOPIA,即ATM 的通用 測試和操作物理接口(Universal Test and Operations PHY Interface for ATM)。 UTOPIA 是連接ATM 層和物理層的接口,允許物理層以不同的速度在不同的媒質(zhì)上進(jìn) 行數(shù)據(jù)傳輸,它包括收發(fā)數(shù)據(jù)端口、控制信號和地址信號。

UTOPIA LEVEL1 和LEVEL2 主 要在地址信號的定義上有所不同,其中LEVEL1 未定義地址信號,主要針對單個物理通道 (Single-PHY)的情況,最大工作頻率25MHz,支持物理層傳輸速率達(dá)到155Mbps,能夠 很好地支持OC-1、OC-3 等同步數(shù)字網(wǎng)的典型傳輸速率;LEVEL2 針對多個物理通道 (Multi-PHY)的情況,比LEVEL1 多了兩組地址信號,最多支持31 個PHY 端口(地址0~ 30,地址31 起端口分隔作用),最大工作頻率50MHz,支持物理層傳輸速率達(dá)到622Mbps, 能夠很好地支持OC-12、OC-12c 等同步數(shù)字網(wǎng)的典型傳輸速率。

2 ATM SAR 及UTOPIA 實現(xiàn)

針對 AAL5 業(yè)務(wù)類型,方案設(shè)計內(nèi)容包括用FPGA 芯片實現(xiàn)UTOPIA 接口的讀、寫時 序控制、實現(xiàn)ATM SAR 功能及完成FPGA 與ARM 處理器上連通信。該設(shè)計實現(xiàn)的全部功 能都包括發(fā)送和接收兩個方向,其中UTOPIA 接口需滿足ATM Forum 提出的Level1 和 Level2 標(biāo)準(zhǔn)。根據(jù)數(shù)據(jù)發(fā)送與接收的流程來劃分功能模塊,分為CS 子層數(shù)據(jù)存儲模塊、ATM SAR 模塊和UTOPIA 接口模塊,發(fā)送和接收過程均為獨立的模塊。

2.1 總體方案概述

如圖 2-1 系統(tǒng)總體框圖可知,F(xiàn)PGA 完成的工作包括對UTOPIA 總線的讀寫時序控制、 實現(xiàn)ATM SAR 功能和與ARM 處理連接。設(shè)計實現(xiàn)的全部功能都包括發(fā)送和接收兩個方向, 詳細(xì)流程如下。

(1)發(fā)送流程:FPGA 存儲器接收CS 子層發(fā)送來的CPCS-PDU 包,將數(shù)據(jù)拆分成48 字節(jié)的SAR-PDU,然后加上5 個字節(jié)的信元頭,得到53 字節(jié)的信元存入發(fā)送存儲器中,由 FPGA 控制UTOPIA 接口發(fā)送時序發(fā)送到物理層去。

(2)接收流程:由FPGA 控制UTOPIA 接口接收時序接收來自物理層的53 字節(jié)信元 存入接收存儲器中,剝?nèi)バ旁^,由信元頭的PT 域指示數(shù)據(jù)的開始、中間和結(jié)束,將接收 到的信元還原成完整的一個CPCS-PDU 包存入FPGA 存儲器后發(fā)送給CS 子層。

2.2 發(fā)送流程模塊設(shè)計

根據(jù)數(shù)據(jù)發(fā)送的流程來劃分功能模塊,分為 CS 子層數(shù)據(jù)的存儲模塊、ATM SAR 模塊 和UTOPIA 接口發(fā)送模塊三個主要功能模塊。

CPCS-PDU 存儲模塊:實現(xiàn):CPCS-PDU 存儲模塊輸入數(shù)據(jù)寬度為16 位,輸出數(shù)據(jù)寬度 為8 位,有可讀/寫、片選信號和地址總線。上層先查詢RAM 的可寫(WR)信號有效時, 將CPCS-PDU 包發(fā)送到16 位數(shù)據(jù)總線上,一個包發(fā)完后置RAM 的片選(CS)信號為無效; RAM 將數(shù)據(jù)線上的數(shù)據(jù)順序存入,并對PDU 包的字節(jié)數(shù)計數(shù),用RAM 的頭兩個字節(jié)存放 包的長度,3~6 字節(jié)存入VPI/VCI 值。一個PDU 包存入后置可寫(WR)信號無效,置可 讀(RD)信號有效。

SAR 拆分和ATM 模塊實現(xiàn):首先在ATM 層創(chuàng)建一發(fā)送FIFO,用來存放ATM 層生成的 信元。在發(fā)送雙口RAM 可讀的狀態(tài)下,從CPCS-PDU 存儲器讀出頭2 個字節(jié)(即數(shù)據(jù)包的 長度)與48 比較,大于48,生成中間信元;等于48 生成末尾信元,存入FIFO,準(zhǔn)備發(fā)送。

UTOPIA 發(fā)送模塊實現(xiàn):UTOPIA 接口實現(xiàn)采用信元級握手傳輸方式,它是以信元為單 位進(jìn)行傳輸,傳輸中的控制信號是以信元為基礎(chǔ)的。設(shè)計一個發(fā)送控制模塊,通過地址信號 輪詢PHY 層狀態(tài),接收來自ATM 層的UTOPIA 控制信號、物理層的控制信號以及發(fā)送FIFO 的狀態(tài)信號,控制信元一個一個地從ATM 層發(fā)送到物理層,時序要求滿足ATM 論壇關(guān)于 UTOPIA 接口Level1 和Level2 標(biāo)準(zhǔn)。

2.3 接收模塊流程設(shè)計

根據(jù)數(shù)據(jù)接收的流程來劃分功能模塊,分為UTOPIA 接口接收模塊、ATM SAR 組裝模 塊和接收SAR-PDU 存儲模塊三個主要功能模塊。

UTOPIA 接收模塊模塊實現(xiàn):首先在ATM 層創(chuàng)建一個接收FIFO,再設(shè)計一個接收控制 模塊,通過地址信號輪詢PHY 層狀態(tài),接收來自ATM 層的UTOPIA 控制信號、物理層的 控制信號以及接收FIFO 的狀態(tài)信號,控制信元一個一個地從物理層傳送到ATM的FIFO 中。

ATM和SAR 組裝模塊實現(xiàn):在SAR-PDU存儲器可寫的狀態(tài)下,不斷讀入信元接收FIFO 的53 字節(jié)數(shù)據(jù),剝?nèi)バ旁^還原為SAR-PDU,由信元標(biāo)識PT 來判斷SAR-PDU 是中間還 是末尾數(shù)據(jù)包,并計算CPCS-PDU 包長度,最后在SAR-PDU 存儲器中存入一個完整的 CPCS-PDU 包,包的長度存入存儲器的頭兩個字節(jié)中。

接收 SAR-PDU 存儲模塊實現(xiàn):接收SAR-PDU 存儲模塊輸入數(shù)據(jù)寬度為8 位,輸出數(shù)據(jù) 寬度為16 位,有可讀/寫、片選信號和地址總線,如圖4-8。可寫(WR)信號有效時,RAM從第六個字節(jié)開始順序存入SAR-PDU(頭2 個字節(jié)放包長,后4 個字節(jié)存放VPI/VCI 值), 直到存入最后一個SAR-PDU,RAM 頭兩個字節(jié)存入CPCS-PDU 包的長度,置可寫(WR) 信號無效,置可讀(RD)信號有效,此時一個完整的CPCS-PDU 包已經(jīng)存好,供CS 子層 讀取。

3 軟、硬件調(diào)試

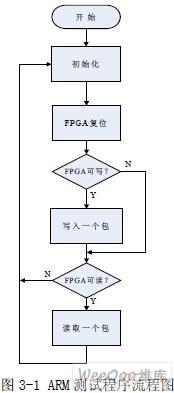

編寫基于ARM7處理器μcLinux 系統(tǒng)下的CPCS-PDU 數(shù)據(jù)包的收發(fā)程序,在Red Hat9.0 系統(tǒng)中(ARM 工具鏈已建立好)編譯通過后,下載到在ECPB 板上運行。程序主要完成ARM 處理器對外設(shè)FPGA 的復(fù)位、讀、寫等操作,流程圖如圖3-1 所示。

QuartusⅡ軟件的SignalTapⅡ邏輯分析儀可以用來采集FPGA 內(nèi)部節(jié)點和I/O 引腳信號, 通過JTAG 端口送往邏輯分析儀顯示。調(diào)試過程中主要利用SignalTapⅡ邏輯分析儀和示波 器,通過收、發(fā)數(shù)據(jù)包來驗證FPGA 中數(shù)據(jù)處理的正確性。

調(diào)試步驟如下:

(1)ARM 測試程序和FPGA 程序下載;

(2)ECPB 板ARM 初始化配置、CMTC 板UTOPIA 接口初始化等;

(3)程序運行; 按照上述步驟驗證 FPGA 芯片設(shè)計是否滿足任務(wù)需求。經(jīng)過發(fā)送和接受數(shù)據(jù)包測試后得 出,經(jīng)反復(fù)數(shù)據(jù)測試比對,F(xiàn)PGA 工作正常,滿足任務(wù)要求。

4 結(jié)束語

本文的創(chuàng)新點在于對 ATM 技術(shù)和UTOPIA 接口時序進(jìn)行了深入、系統(tǒng)的分析與研究, 以替代現(xiàn)有專用通信處理器為目標(biāo),提出了一種采用FPGA 來實現(xiàn)ATM SAR 和UTOPIA 接 口的解決方法。設(shè)計好的FPGA 芯片與上層ARM 處理器和物理層CMTC 板對接后應(yīng)用于 ADSL 測試系統(tǒng)中,在數(shù)據(jù)接收和發(fā)送兩個方向,F(xiàn)PGA 均正確完成上述功能,且工作穩(wěn)定, 具備了專用通信處理器MPC866 同樣的功效。作者相信,本文的研究成果,即采用FPGA 在基于ARM 處理器的環(huán)境中實現(xiàn)了ATM 接口,對于ATM 應(yīng)用領(lǐng)域的成本降低和靈活性有 著較大的實際意義,也為替代專用通信芯片邁出了成功的一步。

-

處理器

+關(guān)注

關(guān)注

68文章

19167瀏覽量

229153 -

FPGA

+關(guān)注

關(guān)注

1626文章

21670瀏覽量

601875 -

芯片

+關(guān)注

關(guān)注

454文章

50421瀏覽量

421855 -

ARM

+關(guān)注

關(guān)注

134文章

9054瀏覽量

366827

發(fā)布評論請先 登錄

相關(guān)推薦

dslam的實現(xiàn)原理,dslam的應(yīng)用組網(wǎng)

ATM技術(shù)在計算機(jī)通信網(wǎng)中的應(yīng)用

ATM交換機(jī)中心控制單元的設(shè)計與實現(xiàn)

采用PM3388和FPGA實現(xiàn)網(wǎng)絡(luò)接口設(shè)計

采用FPGA實現(xiàn)以太網(wǎng)MII接口擴(kuò)展設(shè)計

軟件通信體系結(jié)構(gòu)規(guī)范下如何實現(xiàn)FPGA的硬件抽象層設(shè)計

如何采用FPGA來實現(xiàn)UTOPIA LEVEL2主接口的發(fā)送和接收模塊?

ATM技術(shù)資料

UTOPIA LEVEL2接口時序分析及FPGA實現(xiàn)

ATM技術(shù)中的OAM信元專題

AAL2/AAL5等ATM連接的區(qū)別

面向業(yè)務(wù)管理中業(yè)務(wù)層與管理層接口研究與設(shè)計

通過采用MPC8280為核心實現(xiàn)AAL2與DMA通道的數(shù)據(jù)交互

PCIe物理層接口定義了物理層中的,媒介層和物理編碼子層之間的統(tǒng)一接口

采用FPGA芯片實現(xiàn)AAL中SAR層和ATM層功能與接口設(shè)計

采用FPGA芯片實現(xiàn)AAL中SAR層和ATM層功能與接口設(shè)計

評論