軟件無線電技術給正在開發無線電架構的工程師帶來力量。編程中頻(IF)帶寬、調制、編碼模式和其他無線電功能的能力廣泛引起注意的。除了提供所有這些靈活性外,軟件無線電必須改善靈敏度,動態范圍和鄰信道抑制性能。軟件無線電仍然是無線電,但它必須被比正在替代的通常無線電執行的更好。

現場可編程陣列(FPGA)技術先進之處在于緊湊的占位空間能夠高速處理,同時也保持軟件無線電技術的靈活性和可編程性。FPGA在高速、計算密集、可重新配置應用(FFT、FIR和其他乘法—累加運算)中是受歡迎的。從FPGA和板供應商可得到可重新配置核,在FPGA中能夠實現調制器,解調器和CODEC功能。系統設計人員期待著帶集成FPGA的前端采集/變換器產品來卸載基帶處理和降低數據傳輸率。

盡管應用開發工具有巨大改進,但FPGA設計應考慮硬件開發,這需要不同于軟件開發的技術。

FPGA設計意味著重新設計商用現成的前端數據采集/變換器模塊上的核,這不是簡單的軟件開發執行。在任務計劃階段需要考慮降低延誤。

FPGA在多任務軟件無線電應用(如電子戰、雷達、通信、RF測試)中是重要的。

FPGA或DSP

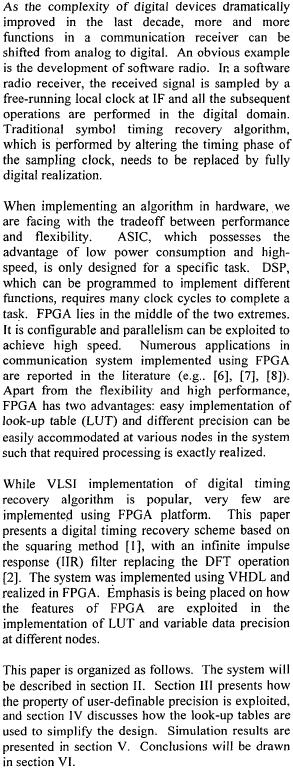

FPGA已從靈活的邏輯設計平臺發展到信號處理引擎。現在FPGA是軟件無線電的主要元件,這是由于FPGAR的靈活性和實時處理能力所致。系統設計人員正在把更多的信號處理集成在一起的靈活性推動設計人員用FPGA替代傳統的DSP。FPGA 因有效的適合于高速并行乘法累加函數。現代FPGA可執行18×18乘法運算,速度超過200MHz。這使得FPGA成為FET、FIR,數字下復頻器(DDC)、數字上變頻器(DUC)、相關器和脈沖壓縮(用于雷達處理)運算的理想平臺。然而,這不意味著所有DSP功能可以在FPGA中實現。用FPGA實現浮點運算是困難的,這是由于器件需要大量的有效區域。另外,包括短陣反演(或除法)的處理更適合DSP/GPP平臺。因此,FPGA和DSP將共存很長時間,一個靈活的平臺將包括二者的混合。

FPGA設計

FPGA設計是特有的硬件設計,而不是簡單DSP編碼執行。EDA(電子設計自動化)工具的發展能保證更好和更精確的設計。傳真軟件在市場有售。FPGA供應商(Xilinx和Altera公司是兩個最大的)也用儀器裝備來促進工具開發。從而使FPGA設計變容易。

FPGA IP核

在普通的FPGA 中,已經增加了來自FPGA供應商和其他第3號核開發商的IP核。這些核提供各種DSP功能。然而,這需要集成到實際的硬件中。把這些核集成到商用現成模塊中需要時間和硬件設計經驗。ICS公司提供的FPGA核是完全測試和集成有高性能數據采集和變換器的商用現成模塊。這些模塊提供智能前端產品,因此,降低了系統設計和集成風險。

寬帶數字下變頻器

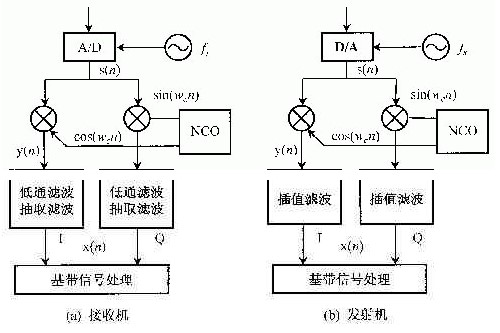

寬帶數字下變頻器(DDC)是任何軟件無線電基系統的主要元件。DDC已基本上改變了通常的無線電設計。DDC能夠簡化RF前端設計,這包括LO和混頻器設計,這是在數字域執行下變頻過程。數字混頻器后面的數字濾波器比傳統模擬濾波器能提供更佳整形濾波。這些濾波器通常是分樣,所以降低了輸出數據率。流行的專用DDC提供可調頻率。然而,它們通常應用目標是窄帶應用。

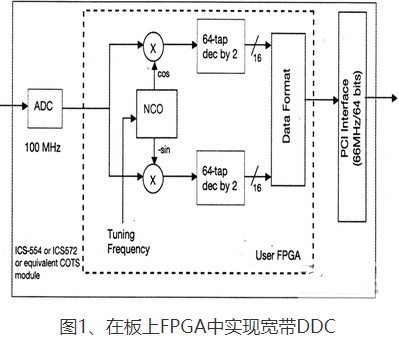

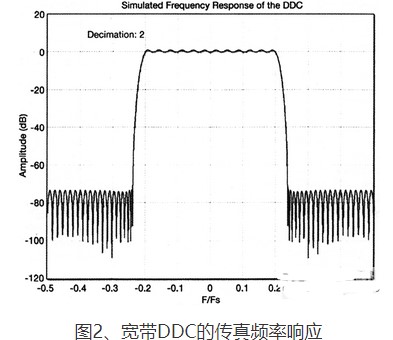

隨著較寬帶寬需求的增加,系統設計人員正在力圖設計帶寬高達40MHz的寬帶系統。這包括雷達、GPS、遙測裝置、寬帶通信等。對于較寬帶寬,在FPGA中實現DDC需要在FPGA之后有ADC。典型的分樣DDC實現示于圖1。此2分樣DDC提供-0.2*FS~0.2*FS的最大平頂帶寬(在100MHz ADC取樣)。用100MHz取樣時鐘,這說明40MHz平頂帶寬和每個信道200MBps數據率。DDC提供阻帶抑制超過70dB(圖2),為較寬帶寬配置的濾波器可提供2X或4X過取樣因數。

濾波器的可編程性是軟件無線電實現的一個主要方面。ICS設計人員已實現平頂帶寬-0.1*FS~+0.1*Fs的4分樣DDC。對于100MHz取樣率,可提供20MHz平頂帶寬。

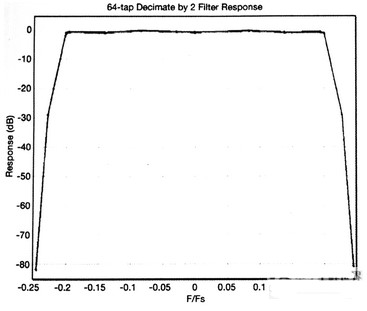

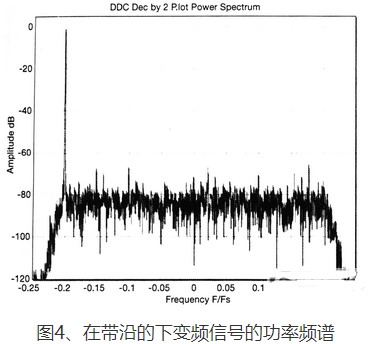

圖3示出在ICS-554中實現的2分樣寬帶DDC的頻率特性。這是實際測量的數據,可與傳真電線對照。圖4示出在帶沿的下變頻信號的頻譜。

圖3、用ICS-554實現的64抽頭2分樣DDC的系統內系統性能

1百萬門的Virt ex II FPGA支持單個2分樣64抽頭DDC,因此,FPGA可容易地集成到ICS-554B中。

在集成這些高速DDC時,必須保證數據傳輸不被中斷。對于多信道系統,這意味著需要用專門數據總線。行業標準PMC模塊具有通過旁路PCI總線經Pn4PMC用戶I/O連接器直接傳輸高速數據。

對于發送器,數字下變頻器用數字上變頻器(DUC)替代。DUC采用數字內插濾波器并具有同樣的優點 。

實時頻譜監控和監測

實時頻譜監視和監測是方便采用FPGA和軟件無線電技術的另一問題。不同于明顯用于信號信息(SIGINT)和EW方案,此功能已泛用于RF測試和頻譜分析應用。

帶高速ADC和大用戶FPGA的商用現成模塊(如ICS-554)對于實時頻監視和監測系統是一個理想的平臺。大用戶FPGA對于實現實時功率頻譜估計值(FFT),幅度計算和頻譜平均是理想的。限定范圍和檢測之后,可以用板上窄帶數字調諧器做為降落接收器來調諧所關心的信道。集成IP核以保證這樣復雜的系統可用于行業標準單PMC卡。

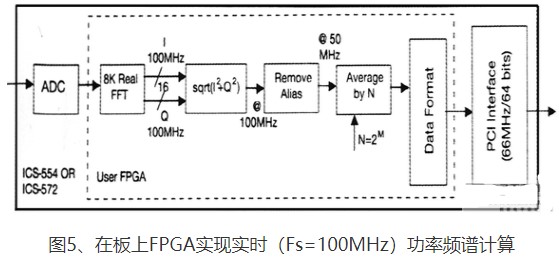

ICS已把8K實時FET引擎和功率檢測及頻譜平均集成在一起(圖5)。

Virtex II FPGA很容易支持需功率檢測和可編程平均的8K FET引擎。

用于改進C/I 的智能天線和相控陣雷達射束形成器

雖具有大量元件的相控陣雷達的C/I改進的智能天線正在成為下一代商用無線系統的共同關心的問題。這兩方面的應用具有共同的原理。這些系統可以處理大量帶寬并能來回傳送數據。建造一個能在多DDC間同步和多模塊間高速數據傳輸均同步系統。

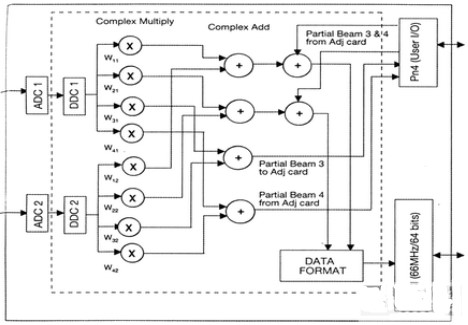

一個在40和20MHz帶寬實現的2×2射束形成器示于圖6。用兩個ICS-554采集4路模擬信道。對于20MHz帶寬,每個ICS-554產生4個單獨的射束,其中兩個射束送到其他數據采集板卡。每個板卡把內部產生的2個單獨射束與以其他ICS-554接收的2個單獨射束組合產生2個完整射束。對于低電壓晶體管—晶體管邏輯(LVTTL)門400MBps。每個方向板之間的數據傳輸是200MBps。希望用低電壓差分傳輸(LVDS)接口能顯著地增加數據傳輸,增加帶寬。

圖6、用安裝在單PCI載波器上的2個ICS-554C模塊實現2×2射束形成器。

在Pn4PMC用戶I/O上高速數據傳輸

在某些應用中,對于系統集成人員從商用現成PMC模塊用用戶定義的協議傳輸高速數據是更方便的,這使系統總線對于其他功能是空閑的。這樣一種協議通常用在前面板數據口(FPDF)協議,這是一種ANSI/VITA(美國國家標準委員會/VME bus行業貿易協會)標準。為了確保高速數據傳輸,ICS在用戶FPGA中已實現發送和接收核來支持PMC模塊的Pn4用戶I/0連接器的FPDA前面板數據口。因此,系統集成人員經FPDA在ICS PMC模塊上有無縫傳輸數據的方法。其他標準和專利數據傳輸協議也能在用戶FPGA中實現。

在Pn4用戶 I/O連接器上用LVDS信號傳輸可在PMC模塊間或從PMC模塊到母板實現高速數據傳輸。

結語

FPGA 正在成為無線電設計的主要部分。要增加更多功能到FPGA。然而,FPGA和傳統DSP及GPP正在共存,而靈活的平臺將包括二者的混合。對待FPGA,設計像執行硬件設計,而不僅是一個軟件問題,在任務計劃階段是需要考慮的因素。

-

dsp

+關注

關注

552文章

7962瀏覽量

348252 -

FPGA

+關注

關注

1626文章

21665瀏覽量

601803 -

無線電

+關注

關注

59文章

2131瀏覽量

116301

發布評論請先 登錄

相關推薦

基于FPGA技術實現軟件無線電的設計

基于FPGA技術實現軟件無線電的設計

評論