直接數(shù)字頻率合成(DDS)是近年來(lái)得到迅速發(fā)展的一種新的頻率合成方法,具有頻率切換速度快,很容易提高頻率分辨率、對(duì)硬件要求低等優(yōu)點(diǎn)。可編程全數(shù)字化便于單片集成、有利于降低成本。提高可靠性并便于生產(chǎn)等有點(diǎn)。DDS技術(shù)從相位的概念出發(fā)進(jìn)行頻率合成,存儲(chǔ)了數(shù)字采樣波形表,可以產(chǎn)生點(diǎn)頻、線性調(diào)頻、ASK、FSK等各種形式的信號(hào)。線性調(diào)頻信號(hào)可以獲得較大的壓縮比,有著良好的距離分辨率和徑向速度分辨率,作為一種常用的脈沖壓縮信號(hào),已經(jīng)廣泛應(yīng)用于高分辨率雷達(dá)領(lǐng)域。

Matlab是美國(guó)MathWorks公司自20世紀(jì)80年代中期推出的數(shù)學(xué)軟件,優(yōu)秀的數(shù)值計(jì)算與卓越的數(shù)據(jù)可視化能力使其很快在同類(lèi)軟件中脫穎而出。Matlab已經(jīng)發(fā)展成為多學(xué)科、多種工作平臺(tái)的功能強(qiáng)大的大型軟件。本文用Matlab軟件建立DDS系統(tǒng)中線性調(diào)頻信號(hào)的仿真模型,對(duì)于理解線性調(diào)頻信號(hào)和在FPGA中來(lái)實(shí)現(xiàn)線性調(diào)頻信號(hào)有借鑒意義。

DDS線性調(diào)頻信號(hào)發(fā)生器框圖設(shè)計(jì)

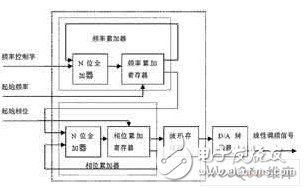

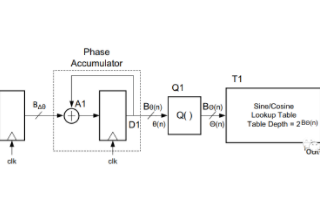

圖 1 DDS技術(shù)的基本原理

1 DDS技術(shù)的基本原理

基本模型如圖1所示,主要由時(shí)鐘頻率源fclk、相位累加器、波形存儲(chǔ)器(ROM)、數(shù)/模轉(zhuǎn)換器(D/A)、以及低通濾波器(LPF)組成。輸出信號(hào)波形的頻率表達(dá)式為:

(1)式中,fclk為參考時(shí)鐘頻率,ΔΦ為相位增量,N為相位累加器的位數(shù)。只要N足夠大,DDS可以得到很小的頻率間隔。要改變DDS的輸出信號(hào)的頻率,只要改變?chǔ)う导纯伞.?dāng)參考時(shí)鐘頻率給定后,輸出信號(hào)的頻率取決于頻率的控制字,頻率分辨率取決于累加器的位數(shù),相位分辨率取決于ROM的地址位數(shù),幅度量化取決于ROM的數(shù)據(jù)字長(zhǎng)和D/A轉(zhuǎn)換器的位數(shù)。

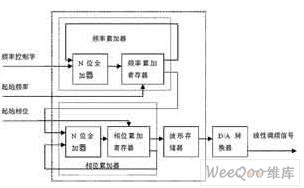

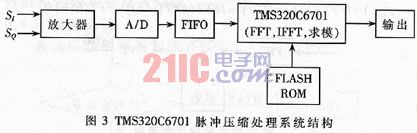

2 線性調(diào)頻信號(hào)的實(shí)現(xiàn)框圖

圖2 軟件編程實(shí)現(xiàn)線性調(diào)頻信號(hào)的原理圖

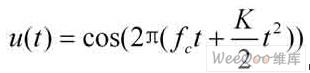

脈沖壓縮雷達(dá)最常見(jiàn)的調(diào)制信號(hào)是線性調(diào)頻信號(hào),接收時(shí)采用匹配濾波器(Matched Filter)壓縮脈沖。它的數(shù)學(xué)表達(dá)式如下:

式中fe為載波頻率,K=B/T是調(diào)頻斜率,于是,信號(hào)的瞬時(shí)頻率為。

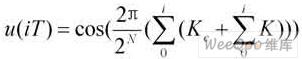

其對(duì)應(yīng)的量化公式如下(此式是以圖2實(shí)現(xiàn)的原理公式):

(3)

(3)

式中N為相位累加器的位數(shù),Kc為頻率控制字,K為上式中的調(diào)頻斜率。

圖1所示的DDS原理框圖是用于實(shí)現(xiàn)固定頻率的正弦波信號(hào),按照公式(3)的思路實(shí)時(shí)改變?chǔ)う担纯僧a(chǎn)生線性調(diào)頻信號(hào)。

經(jīng)過(guò)頻率累加器輸出的是嚴(yán)格線性增長(zhǎng)的瞬時(shí)頻率。在實(shí)際過(guò)程中,相位累加器的輸出是經(jīng)過(guò)相位截?cái)嘣龠M(jìn)行尋址,從而引入了一定的相位誤差,雖然這一誤差會(huì)影響到線性調(diào)頻信號(hào)的線性度,但是調(diào)頻斜率為相位的二次導(dǎo)數(shù),相位截?cái)嗾`差本身已很小,所以對(duì)調(diào)頻線性度的影響就更小了。在本文的Matlab實(shí)現(xiàn)中暫時(shí)不考慮截?cái)鄦?wèn)題,忽略不計(jì)。

3 Matlab軟件建模實(shí)現(xiàn)線性調(diào)頻信號(hào)

本程序遵照上述軟件編程實(shí)現(xiàn)線性調(diào)頻信號(hào)的原理圖編寫(xiě),采用.m文件的方式編寫(xiě),下面是實(shí)現(xiàn)的源程序:

%調(diào)頻信號(hào)的累加器實(shí)現(xiàn)

clear all;clc %清除所有變量,清屏

M=2^11; %采樣的點(diǎn)數(shù)

a(1:1:M)=0; %頻率累加器的數(shù)值

b(1:1:M)=0; %相位累加器的數(shù)值

y(1:1:M)=0; %輸出的波形數(shù)據(jù)

K=400; %調(diào)頻斜率

Kc=10; %初始頻率控制字

N=10; %幅度量化位數(shù)

L=24; %相位累加器位數(shù)

%下面一段實(shí)現(xiàn)頻率累加器

a(1)=0.5*K; %初始頻率步進(jìn)量

for i=2:1:M

a(i)=a(i-1)+K;

end

%下面一段實(shí)現(xiàn)相位累加器

b(1)=Kc+a(1); %相位初始值

for i=2:1:M

b(i)=b(i-1)+(Kc+a(i));

end

%下面一段實(shí)現(xiàn)了查找表ROM以及進(jìn)行幅度量化

for i=1:1:M

y(i)=floor(2^N*cos(2*pi/(2^L)*b(i)));

end

%下面一段畫(huà)出相應(yīng)的圖形

figure(1);plot(y);axis([0 M,-2^N-100 2^N+100]);

figure(2);freqz(y)

上面這段程序中,有很多的變量,包括調(diào)頻斜率K、頻率控制字Kc、幅度量化位數(shù)N以及相位累加器位數(shù)L等等,修改不同變量值可以得到各,不同的線性調(diào)頻信號(hào)。具體的實(shí)現(xiàn)要根據(jù)實(shí)際的需要來(lái)設(shè)置。

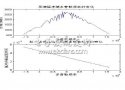

4 實(shí)驗(yàn)結(jié)果

根據(jù)上面的程序,取調(diào)頻斜率為400,頻率控制字為10,幅度量化為10位(和所使用的D/A配合),相位累加器為24位,用Matlab仿真得到的線性調(diào)頻信號(hào)的波形和相應(yīng)的幅頻響應(yīng)如圖3和圖4所示。

結(jié)束語(yǔ)圖3 K=400,Kc=10,N=10,L=24的情況下的線性調(diào)頻信號(hào)

圖4 針對(duì)圖3的幅頻特性曲線

本文所講的線性調(diào)頻信號(hào)的產(chǎn)生原理和方法有很好的可擴(kuò)展性,修改頻率累加器的內(nèi)容即可以實(shí)現(xiàn)其他的各種調(diào)頻信號(hào)。作為線性調(diào)頻信號(hào),由于廣泛應(yīng)用于高分辨率的雷達(dá)系統(tǒng)中,因此正確理解線性調(diào)頻信號(hào)的產(chǎn)生原理和掌握其產(chǎn)生的方法是很有現(xiàn)實(shí)意義的。在實(shí)際應(yīng)用中主要采用專用DDS芯片或者FPGA來(lái)實(shí)現(xiàn)線性調(diào)頻信號(hào)(各有優(yōu)缺點(diǎn)),而本文則基于Matlab軟件的良好編程性來(lái)驗(yàn)證這一方案,仿真結(jié)果較好的證明本方案的可行性,完成了預(yù)期的方案設(shè)計(jì)和論證。

-

dsp

+關(guān)注

關(guān)注

552文章

7962瀏覽量

348310 -

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602044 -

調(diào)頻信號(hào)

+關(guān)注

關(guān)注

0文章

18瀏覽量

12734 -

仿真

+關(guān)注

關(guān)注

50文章

4048瀏覽量

133431

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于FPGA 的DDS 調(diào)頻信號(hào)的研究與實(shí)現(xiàn)

基于FPGA的雷達(dá)線性調(diào)頻信號(hào)實(shí)現(xiàn)

基于FPGA的DDS調(diào)頻信號(hào)的研究與實(shí)現(xiàn)

基于SystemView的調(diào)頻信號(hào)的調(diào)制解調(diào)仿真

基于TMS320C6701 DSP的線性調(diào)頻信號(hào)的數(shù)字脈沖壓

基于STM32和FPGA的可控線性調(diào)頻信號(hào)源的設(shè)計(jì)

基于TMS320C6701浮點(diǎn)DSP芯片來(lái)實(shí)現(xiàn)線性調(diào)頻信號(hào)的

基于FPGA IP核的線性調(diào)頻信號(hào)脈沖壓縮

線性調(diào)頻信號(hào)干擾仿真分析

線性調(diào)頻信號(hào)數(shù)字脈壓的分析及其實(shí)現(xiàn)系統(tǒng)

調(diào)頻線性度對(duì)線性調(diào)頻信號(hào)影響

線性調(diào)頻信號(hào)檢測(cè)方法

基于FPGA的DDS IP實(shí)現(xiàn)線性調(diào)頻信號(hào)的設(shè)計(jì)方案

通過(guò)Matlab軟件實(shí)現(xiàn)對(duì)DSP/FPGA線性調(diào)頻信號(hào)仿真

通過(guò)Matlab軟件實(shí)現(xiàn)對(duì)DSP/FPGA線性調(diào)頻信號(hào)仿真

評(píng)論