傳統的頻率特性測試儀不僅價格昂貴,且得不到相頻特性,更不能保存頻率特性圖和打印頻率特性圖,也不能與計算機接口,給使用者帶來了諸多不便。而本文采用DDS技術作為掃頻信號源;同時采用了集成模擬芯片AD8302對幅度和相位進行檢測,用DSP芯片TMS320VC5409和CPLD芯片EPM7128進行測量控制和數據處理,人杌接口部分是利用單片機AT89C51實現,并配有打印機接口和串行通信接口。

1 系統總體方案設計

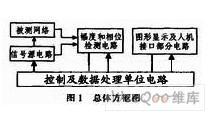

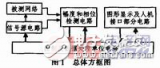

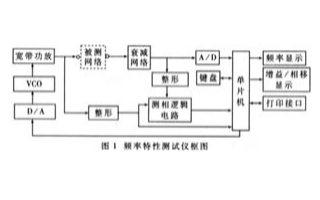

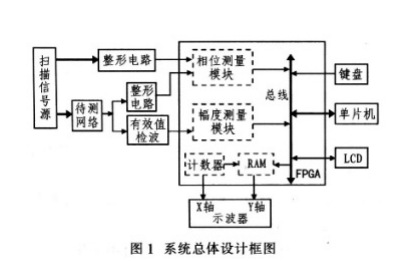

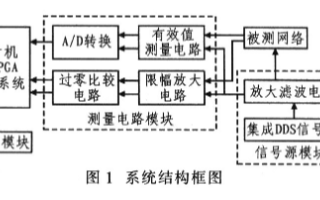

頻率特性測試系統一般包含測試信號源、被測網絡、檢波及顯示3個部分。本系統根據所要完成的測試功能及技術指標,該系統應由掃頻源、幅度相位測量電路、控制及運算部分、人機接口單元幾部分組成。系統總體方框圖如圖1所示。

信號源電路由信號發生電路和信號調理電路兩部分組成。在本系統中信號發生電路采用DDS技術(即直接數字頻率合成技術)實現,用于產生頻率、持續時間等均可控的掃頻信號,并能夠滿足一般用戶對頻率范圍的要求;信號調理電路主要是對信號中的噪聲進行抑制并對輸出信號的功率起到控制作用。

增益相位檢測電路是為了檢測被測網絡兩端的幅度差和相位差。先對被測網絡兩端的信號進行預處理后對其進行模擬鑒幅和鑒相,然后把幅度差和相位差的模擬量由ADC轉化為數字量,送給控制及數據處理電路進行分析處理。

控制及數據處理電路要完成邏輯控制、數據處理和與人機接口部分通信3個主要功能,由DSP和CPLD組成。主要用于控制整個系統的協調工作,并對測量及人機接口部分來的數據進行分析處理。

圖形顯示及接口電路負責接收各種指令和顯示測量結果,測量時掃頻信號所需要的起始頻率、終止頻率、頻率問隔、單頻點持續時間、信號功率等參數,以及測量完成后顯示特性曲線時顯示方式的設置,如:刻度大小選擇、文字標注方式、坐標選擇等。

2 系統硬件設計

系統由掃頻源、幅度相位測量電路、控制及運算部分、人機接口單元幾部分組成。

2.1 掃頻信號源設計

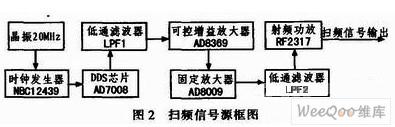

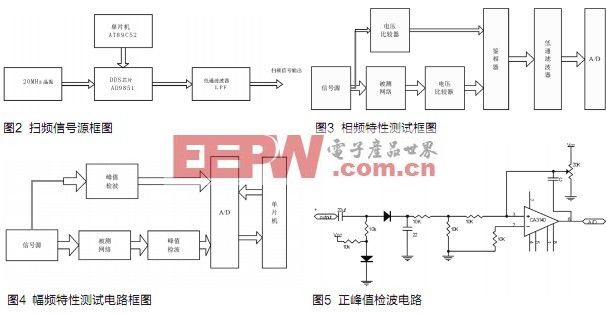

直接選用DDS技術設計掃頻信號源。從設計要求低頻和成本考慮,這里選擇AD7008系列中20 MHz芯片。掃頻信號源框圖如圖2所示。由于AD7008內部沒有時鐘發生電路,所以需要外部時鐘源提供時鐘信號,本系統采用NBC12439為AD7008提供時鐘信號。

由于AD7008輸出信號的幅度不能達到系統所要求的-55~+18 dBm的范圍,故需要對信號進行放大,放大電路的設計較為簡單,為了便于對輸出信號的功率控制使用了可控增益放大器,易于數字控制增益的大小;又因為輸出信號的最大功率要達到+18 dBm且信號頻率最高達5 MHz,普通的運放難以達到要求,故使用射頻放大器來提升信號的輸出功率。AD7008所產生的信號直接由器件內部的DAC輸出,內部不含低通濾波器,故要對其輸出信號進行濾波處理。

2.2 幅度相位檢測電路的設計

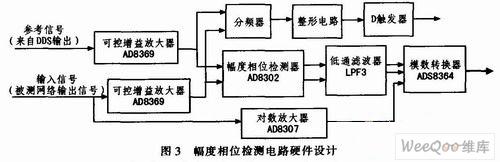

介紹用幅度相位檢測芯片AD8302來檢測被測網絡的幅度和相位,及其信號調理電路,以及模擬/數字轉換電路和相位的極性判斷電路。由于增益相位檢測器AD8302要求被檢測的兩路信號功率在-60~0dBm范圍內,為防止損壞器件,需對兩路信號進行功率調整,本系統使用了易于數字控制增益的可控增益放大器AD8369和對數放大器AD8307構成一個反饋系統進行自動調整。對數放大器AD8307可以對信號的幅度進行檢測,通過被檢測到的幅度范圍,系統調整可控增益放大器AD8369的放大倍數,使增益相位檢測器AD8302能夠有效地對被測網絡的增益和相位進行檢測。將模擬增益和相位檢測結果轉化為數字量的方法是采用ADC,由于檢測結果是個慢變信號,因此對ADC的速度要求較低,本系統中具有3路模擬量要轉化為數字量,因此選用了多通道模數轉換器件——ADS8364。幅度相位檢測電路的硬件設計方案如圖3所示。

由于AD8302檢測的相位是0~180°之間,不能給出相位是超前還是滯后,所以需要相位極性判斷電路對相位進行判斷,其電路主要由分頻器電路、施密特觸發器、D觸發器等組成。

2.3 數據處理及控制電路設計

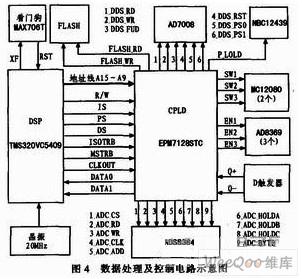

數據處理及控制單元主要完成通信、數據處理、功能控制等工作。主要由TMS320VC5409、晶體振蕩器、電源控制、WATCHDOG和CPLD等器件組成。

2.3.1 電路設計

這一部分電路是數字電路,所用器件均為數字器件,核心芯片是TI公司的數據處理芯片TMS320VC5409和ALTEM公司的CPLD芯片EPM7128。電路結構圖如圖4所示。

系統是對電網絡進行實時測量,在測量過程中要采集大量的數據,對這些數據還需要進行數字濾波等方法來提高準確度,系統必然需要大數據量的運算,而單片機的運算能力弱不能達到實時處理的要求,故采用DSP作為數據處理電路的核心,考慮到系統成本因素采用TI公司的54系列DSP。

在選擇可編程邏輯器件時,容量大小是需要考慮的最基本問題。故在器件選擇前,先確定完成設計功能所需邏輯資源的多少,本系統對CPLD所要完成的功能經仿真、綜合后,約需占用1 500門左右的邏輯資源。綜合考慮之后選擇了Altera公司Max7000系列的EPM7128。

在圖4中TMS320VC5409通過主機接口(HPI)接受單片機系統來的各種控制命令,并通過EPM7128STC控制掃頻信號源中的時鐘發生器NBCl24 39、DDS芯片AD7008和可控增益放大器AD8369產生信號功率可控的掃頻信號;控制增益相位檢測電路中的2個可控增益放大器AD8369和A/D轉換器ADS8364進行信號檢測;據輸入信號頻率對兩個MC12080的分頻比進行控制;選通D觸發器讀入相位極性。

2.3.2 看門狗電路設計

由于本系統是一個獨立的系統,且DSP系統的工作時鐘頻率較高,在運行時極有可能發生干擾和被干擾,嚴重時系統可能會出現死機現象,為了克服這個毛病,除了在軟件上做一些保護措施外,在硬件上也必須做相應的處理。硬件上最有效的保護措施通常采用具有監視功能(WATCHDOG)的自動復位電路。

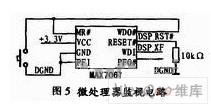

其基本原理是電路提供一個用于監視系統運行的信號,當系統運行正常時,應在規定的時間范圍內給監視線一個高低電平發生變化的信號,如果在規定的時間內這個信號不發生變化,自動復位系統就認為系統運行不正常并重新對系統進行復位。本系統采用MAXIM公司的微處理監視電路MAX706-T實現對系統的監視,電路如圖5所示。

2.4 單片機系統設計

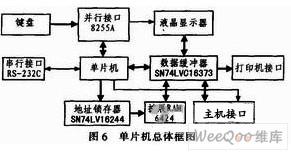

本系統主要功能是完成人機接口功能和通信功能,包括鍵盤、液晶顯示器、標準串行接口、微型打印機接口和與DSP通信的HPI接口等。單片機系統總體框圖如圖6所示。

單片機是用AT89C51,通過1片8255A來擴展其并口,8255A的C口用于鍵盤接口,A口接到打印機數據線,打印機的控制線接于單片機的P1口(占3位),8255A的B口對液晶顯示器進行控制,液晶顯示器的數據線通過緩沖器接于單片機的P0口。HPI接口完成與DSP的通信。

3 系統軟件設計

系統電路的軟件設計包括DSP軟件設計和CPLD的軟件設計。

3.1 DSP軟件設計

DSP軟件的設計使用了TI公司的CCS開發工具,通過DSP仿真器進行調試,使用C語言和匯編語言混合編程。

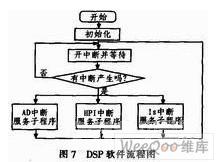

DSP軟件程序主要功能是通過中斷方式從單片機系統中得到各種設置參數和命令,并根據這些參數和命令進行相應設置和相應操作,并將采集的數據處理后送單片機系統顯示。另外還要照看看門狗。其程序流程圖如圖7所示。

3.1.1 主程序設計

系統上電后,TMS320VC5409內部固化的加載程序檢測到外部8為并行加載方式有效,則將存儲在AT29C010A中的源程序取出存入內部SRAM中。源程序占據FLASH的低32 K地址空間0000H~7FFFH,同時映射在DSP外部數據存儲空間8000H~FFFFH。加載過程中DSP軟件上自動設置7個等待周期,可保證數據存取正確。加載完畢程序開始順序執行,首先設置定時器,開定時器中斷,使其在每低于0.8 s的時間內產生一次中斷,在定時器中斷子程序中設置專用輸出管腳XF,使看門狗的輸入端定時產生變化,否則其將產生DSP的RESET信號。然后,對系統進行初始化,初始化結束后。為了降低系統功耗可使DSP進入空轉狀態(IDLE),直到中斷發生。程序流程如圖8所示。

初始化包含DSP初始化、AD7008初始化以及AD8369的初始化。DSP的初始化主要是對中斷向量的定義,內部時鐘的設置,外部等待時間的設置以及內部空間SRAM/DRAM的映射等,這些都是通過對DSP內部專用寄存器的設置來完成的。AD7008的初始化可通過設置控制寄存器來完成。AD8369的初始化是把AD8369的放大倍數降為最小-10 dB,可以減少信號源電路的射頻功放的功率,也可以保護增益與相位檢測電路中增益鑒相器AD8302,使AD8302的輸入信號功率保持為最低,防止輸入信號功率過大損壞器件。

3.1.2 HPI中斷服務程序設計

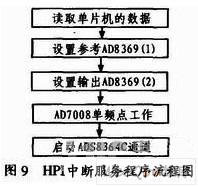

HPI口是連接單片機與DSP的接口,通過HPI口,主機也就是單片機可以向DSP寫數據,也可以從DSP的RAM單元讀取數據;同時通過HPI口控制寄存器提供的中斷位,以及HPI的中斷信號中斷單片機,主機和單片機可以實現很好的對話。并且,根據單片機來的數據,進行相應操作。其流程圖如圖9所示。

AD7008單頻工作的目的是為了檢測輸入信號的幅度范圍,從而設置輸入AD8369的增益倍數。AD7008以起始頻率為頻率點進行單頻工作,輸入信號的幅度檢測由AD8307來完成,檢測結果由ADS8364的C通道進行數據轉換,供DSP采集。當采集到的數據個數達到系統設置值后,DSP對數據進行處理,判斷出輸入信號的幅度,以設置檢測電路中AD8369(2、3)的增益。

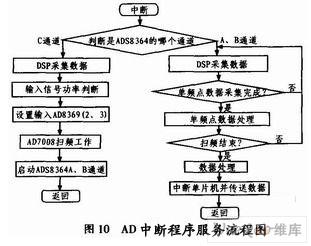

3.1.3 AD中斷服務程序設計

在AD中斷服務子程序中,主要是對采樣數據的讀取,如果是ADS8364的C通道的數據則是對輸入信號進行幅度判斷:如果是ADS8364的A,B通道的數據則是進行幅度相位的測量。測量結束后,將處理好的數據送單片機顯示。其流程圖如圖10所示。

通過C通道判斷以后,就設置好了檢測電路中的AD8369(2、3),完成了掃頻測試前的準備工作,AD7008可以開始掃頻工作了。按照起始頻率、頻率步長、單頻點持續時間等對AD7008相應寄存器進行設置,使AD7008輸出滿足要求的掃頻信號;緊接著啟動ADS8364的A、B兩通道進行數據的轉換,其轉換的是AD8302的增益和相位檢測電壓:DSP在中斷服務子程序中對ADS8364進行數據采集。并做以下工作:接收采集數據,判斷單頻點采集到的數據量,進行單頻點數據的數字濾波和簡單計算處理,判斷掃描頻率點數是否達到要求,決定掃頻是否結束,將數據轉換成圖形顯示格式送單片機顯示。

3.1.4 1s中斷服務程序設計

1s中斷服務程序較為簡單,就是照看看門狗,看門狗是系統穩定運行的重要部件,由于系統的高速運行,外界的干擾以及程序內部的有關問題,都有可能導致系統的運行不穩定,甚至出現死機的情況。設置看門狗就是在系統出現意外而導致運行紊亂、死機時,自動恢復運行的保證。在系統出現上述情況時,當時間超過1 s時,看門狗將自動重新啟動系統。相關內容在系統硬件設計部分有涉及。

3.2 CPLD軟件設計

CPLD的軟件設計使用MAXIM公司的MAX+PLUSII開發工具,使用VHDL語言進行編程。這部分程序主要是對來自DSP的信號進行譯碼后,對各個器件進行控制,使整個系統協調工作,完成測量任務。其設計流程圖如圖11所示。

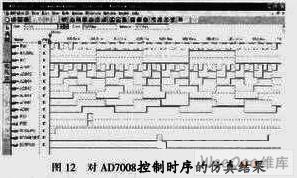

圖12是CPLD對AD7008控制時序的仿真結果。從圖中可以看到,當IOS和IOSTRB信號為低電平(這時DSP選中IO空間)時,CPLD芯片對DSP的高位地址(ADD15~ADD9)進行譯碼,當高位地址為00H時,選中AD7008芯片,并在DSP讀寫信號RW為低時,DDSWRB變為低電平,即對AD7008進行寫入操作;當高位地址為78H時,CPLD使DDSRESET信號變為低電平,即對AD7008進行復位操作;當高位地址為01H時,CPLD使DDSFUD信號變為高電平,否則變為低電平,此信號在上升沿對AD7008內部存貯器進行更新操作。可以看出,仿真結果符合要求。

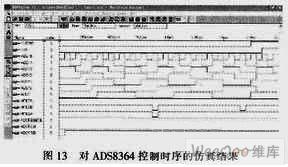

圖13是CPLD對模數轉換芯片ADS8364的仿真結果,同樣,當IOS和IOSTRB信號為低電平(這時DSP選中10空間)時,CPLD芯片對DSP的高位地址(ADD15~ADD9)進行譯碼,當高位地址為20H時,ADCRESETB信號輸出低電平,對AD8364進行復位操作;當高位地址為30H時,ADCCSB信號輸出低電平,對ADS8364進行片選;當最高四位地址(ADD15~ADD12)為0CH時,由ADD11、ADD10、ADD9三位譯碼決定HOLDC、HOLDB、HOLDA的輸出電平;這3個信號分別控制ADS8364的3個采樣通道的轉換。由圖可以看出,其仿真結果符合要求。

4 測量結果

掃頻范圍0.004 7 Hz~5 MHz,可以在全頻段內任意設置掃頻寬度,分辨率為0.004 7 Hz,輸出電平范圍-55~+18 dBm,掃頻步長可以在0.004 7 Hz~0.5 MHz范圍內自行調整;輸出阻抗50 Ω,相位測量精度小于0.1°,幅度測量精度小于0.5 dB,不平坦度+/-0.25 dB,電控衰減并數字顯示衰減量,能在全頻范圍內自動步進測量,可預置測量范圍及步進頻率值。能顯示幅頻特性和相頻特性曲線,并能根據選擇,放大局部曲線,可以用對數坐標和線性坐標顯示,并配有文字標注。

5 小結

本系統設計適用于科研、教學以及生產領域等方面,與傳統的頻率測試儀相比,用直接數字頻率合成(DDS)技術為頻率特性測試儀實現數字化開辟了道路,利用液晶顯示器技術使頻率特性測試儀小型化成為可能。此測試儀有很強的應用價值,可取代傳統的頻率測試儀。

-

dsp

+關注

關注

552文章

7962瀏覽量

348293 -

芯片

+關注

關注

454文章

50444瀏覽量

421930 -

單片機

+關注

關注

6032文章

44522瀏覽量

633182 -

DDS

+關注

關注

21文章

632瀏覽量

152545

發布評論請先 登錄

相關推薦

基于單片機和FPGA的頻率特性測試儀

基于DSP的低頻頻率特性測試儀

低頻頻率特性測試儀設計方案解析

MSP430單片機和DDS技術的頻率特性測試儀的設計詳析

低頻段數字式頻率特性測試儀的特性功能和實現設計

如何使用單片機和FPGA為核心實現頻率特性測試儀的設計

采用DDS技術與AD8302芯片實現了數字化頻率特性測試儀的設計

采用DDS技術與AD8302芯片實現了數字化頻率特性測試儀的設計

評論