移動互聯網時代的到來,高清多媒體視頻的普及,3D大型手機游戲對的出現,單核嵌入式硬件平臺已經難以滿足復雜的實際計算需求。而異構多核處理器在視頻編解碼運算上具有強大的優勢,已經成為了嵌入式處理器架構發展的趨勢。目前普遍高清視頻編解碼都采用異構多核處理器內的DSP進行協同處理,通過片上通信機制實現核間多媒體數據傳輸。DSP相比軟解碼在速度和性能上得到了一定的提升,如DaVinci平臺內置DSP能夠實現720P視頻實時解碼。但DSP運行時需要對信箱以及 DMA 進行配置,占用較多的片上通信帶寬,導致核間通信效率不高,同時DSP編解碼效率和硬編解碼器相比仍偏低。為了進一步提高全高清H264編解碼性能,本文采用TI Soc OMAP4430異構多核處理器作為處理平臺,其最大不同在于內置雙核Cortex-A9強勁處理器、雙核Cortex-M3協處理器及IVA-HD多媒體硬編解碼加速引擎。IVA-HD引擎內部有7個針對各種視頻編解碼而設計的加速引擎,每個加速引擎擁有獨立的數據存儲器,可以在最大程度上降低模塊間因為讀寫數據造成的競爭。同時采用virtio緩存隊列和RPMsg 消息框架來實現基于異步通知的主處理核A9與協處理核M3間數據通信,具有大數據通信效率高、異步通知、等優點。OMAP4430處理器內部的Cortex-A9雙核處理器將運行高級嵌入式操作系統Linux,負責系統工作任務的調度、音頻解碼、用戶界面交互,而其內部的Cortex-M3將充當輔助處理核,管理IVA-HD加速引擎完成解碼任務,最后用實例驗證本次設計的正確性。

1 主要技術

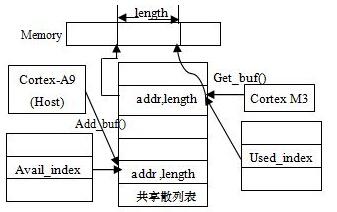

1.1 virtio緩存隊列

Virtio 是半虛擬化 hypervisor中位于設備之上的抽象層, 為異構多核間數據通信提供了最低層的實現。它使用了兩個基于異步通知的緩存隊列( 一個用于向協處理核發送數據,一個用于從協處理核接收數據)和散列表用于與遠程異構處理器進行數據通信。每個緩存隊列最多包含有512個緩存,每個緩存的大小限制在512字節以內,緩沖池里面存放著通信數據。為了最大程度減少共享內存,采用環形散列表,散列表每個表項包括了緩存的物理地址和緩存的大小,散列表存放在內存特定地址中,主處理核與協處理核基于互斥機制的共享內存方式進行訪問,如圖1所示:

圖1 異構多核間訪問virtio緩存池示意圖

采用共享環形散列表進行異構處理核間數據通信的好處主要有幾個方面:

1)采用散列表表項表示數據緩存可以減小共享內存區域的大小,提高系統內存使用率,同時允許變長數據傳輸。

2)采用中斷方式通知目的處理器散列表的變化,減少了處理器盲目等待時間,提高了處理器的利用率

3)允許同時傳輸多個緩存數據,提高了系統通信的吞吐率

1.2 RPMsg消息框架

RPMsg(Remote processor Messaging) 是一個基于virtio技術的用于處理器核間數據通信的消息框架,提供協處理核上電復位管理、消息通信等功能。

1.2.1 協處理核復位管理

主要負責加載程序執行體到協處理核的運行內存中、設置負責虛擬地址映射到物理地址MMU單元,當協處理核遇段錯誤或內部代碼異常時,需要輸出直觀的出錯信息并且提供了恢復機制使得協處理核可以重新使用。

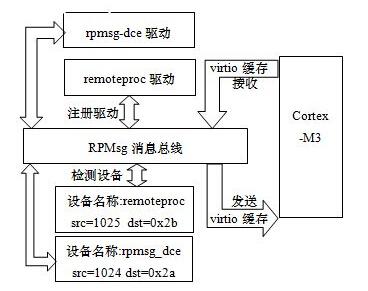

1.2.2 消息通信

RPMsg消息框架是基于virtio緩存隊列實現的主處理核和協處理核間進行消息通信框架,RPMsg向系統注冊了一條消息總線,并為每個M3協處理核創建相應的總線設備,而多個客戶端驅動程序也注冊在該消息總線上并分配一個本地地址端口src和遠程地址端口dst,當客戶端驅動需要發送消息時,會把消息封裝成virtio緩存并添加到緩存隊列中以完成消息的發送, 當消息總線接收到協處理器送到的消息時會根據消息地址端口dst合理的派送給客戶驅動程序進行處理。其示意圖如圖2所示:

圖2 RPMsg消息總線工作示意圖

1.3 IVA-HD加速引擎

H.264/MPEG-4 Part 10 是由ITU-T 視頻編碼專家組和ISO/IEC 運動圖像專家組 (MPEG) 聯合提出的高度壓縮數字視頻編解碼器標準,被廣泛應用于網絡流媒體資源、HDTV 等方面。與之前MPEG4、H263 等標準相比,H.264 具有低碼率、高畫質、高壓縮率和高可靠性等特點,適用于干擾嚴重、丟包率高的信道中傳輸。

H264解碼流程如圖3所示,解碼器從網絡抽象層NAL中接收輸入的數據幀,進過熵解碼、重新排列后得到量化系數矩陣X,量化系數矩陣在經過反量化和空間變換后得到計算殘差Dn,同時通過運動補償和幀間預測或幀內預測得到預測快Pn, 將Pn和Dn相加結果uFn經過環路濾波得到輸出緩存圖像Fn。

圖3 H264解碼器工作流程

IVA-HD引擎是針對嵌入式平臺進行多媒體編解碼加速而設計的第三代硬件加速引擎,其支持H264、MPEG4、MPEG2、H263等常見的視頻編解碼標準。為了釋放CPU,讓其更有效的進行數據準備和邏輯功能控制,IVA-HD集成了7個硬件加速引擎,他們和H264解碼各個功能模塊所對應關系在圖3中用虛線框表示,其中加速引擎名稱core1-5所對應的模塊功能分別是: 熵解碼、反量化和反變換、環路濾波、幀內預測、運動補償。

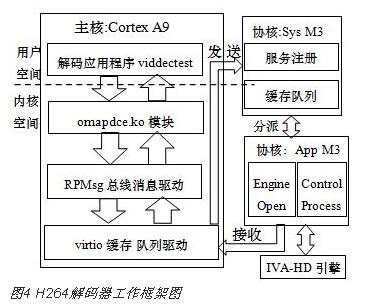

2 系統設計

全高清H264解碼任務由主處理器Cortex-A9和協助處理器Cortex-M3共同完成,Cortex-A9主要負責從多媒體文件中或網絡數據流中進行數據的讀取、多媒體數據包過濾分離視頻流和音頻流、構建RPMsg控制消息進過virtio緩存封裝發送給協處理核Cortex-M3以設置IVA-HD加速引擎的控制參數、向協處理器發送多媒體數據包進行H264解碼、在協處理器完成解碼任務后接收圖像并通過DRM API及KMS 模塊繪制到屏幕上。

平臺上有兩個Cortex-M3處理核,分為Sys M3和App M3,都運行TI BIOS實時操作系統,其中Sys M3主要負責創建與Cortex-A9通信的virtio緩存隊列,對程序執行流程和CPU負載情況進行記錄,接收A9發過來的緩存數據并進行參數解析,同時根據緩存中dst參數分派緩存到App M3的相應消息鏈表中。而App M3協處理器則完成實際的解碼工作,App M3將通過運用于嵌入式平臺的Codec Engine來完成對IVA-HD加速引擎的操作。App M3將提取消息鏈表中消息請求相應設置IVA-HD加速引擎的狀態和初始化參數,在進行實際解碼時會通過Codec Engine 來調用IVA-HD加速引擎來完成解碼任務并將解碼結果通過 緩存隊列發送回Cortex-A9處理器。整個系統解碼的框架圖如圖4所示:

3 系統實現

3.1 Cortex-A9軟件實現

Cortex-A9運行Linux操作系統,包括內核模塊omapdce.ko和virtio緩存、RPMsg總線驅動程序設計和ffmpeg多媒體庫及DRM顯示接口調用.

3.1.1 virtio緩存隊列實現

Virtio緩存隊列以共享散列表的方式和協處理器進行數據通信,通過中斷方式通知對方散列表的添加,包括以下幾個方面:

1)Irq_require()注冊中斷函數,Register_bus_type(“virtio”)向系統注冊virtio總線

2)Regsiter_virtio_driver(&virtio_driver)向virtio總線注冊一個驅動客戶端,用于創建向RPMsg總線注冊的設備。

3)系統在發現協處理器后將通過register_virtio_device(&virtio_device)向virtio總線注冊一個設備,設備內部含有創建virtio緩存隊列的函數指針

4)virtio_bus->match(&virtio_device,&virtio_driver)函數將匹配virtio_driver與virtio_device是否合適,如果匹配成功,virtio_driver->probe(virtio_device)來創建send_virqueue、recv_virqueue及注冊到RPMsg的rpmsg_device,。這樣virtio緩存隊列就和RPMsg總線聯系在一起。

3.1.2 RPMsg消息框架實現

RPMsg總線將掛載許多rpmsg_driver和rpmsg_device,和rpmsg_driver都有本地端口src和目的端口dst屬性,每次發送消息時會調用rpmsg_send((void*)data,src,dst)將消息添加到virtio的緩存隊列中,而當消息msg達到RPMsg總線時,總線把msg分配給dst屬性和msg->dst相同的rpmsg_driver,并調用rpmsg_driver->callback()進行消息處理。

3.1.3 omapdce.ko驅動模塊的實現

Omapdce.ko模塊將作為一個RPMsg driver,其實現了應用程序引擎相關API的內核實現,主要包括ioctl_engine_open()、ioctl_viddec_create(),ioctl_viddec_control()、ioctl_viddec_process(),他們提供了應用API engine_open、viddec_create()、viddec_control()、viddec_process()的驅動實現,這些驅動函數將調用RPMsg總線rpmsg_send()、rpmsg_recv()與協處理器進行消息通信以完成工作任務。

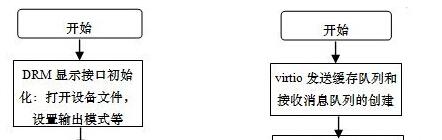

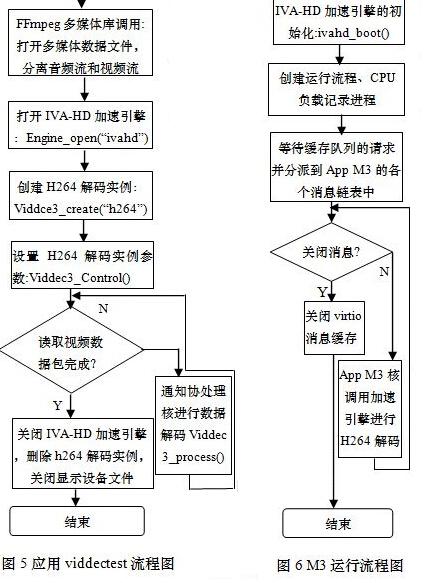

3.1.4 解碼應用viddectest實現

H264解碼應用程序viddectest的工作主要分為以下幾個方面

1)Linux顯示接口DRM初始化,通過Drmopen()函數打開/dev/dri/card0設備文件,獲取設備資源drmModeGetResources(),創建幀緩存drmModeAddFB2()及設置輸出分辨率及模式drmModeSetCrtc()

2)FFmpeg媒體庫的調用,通過AVOpenStreamFile()打開多媒體文件,AVFindStream()分離出音頻流和視流,然后依次通過AVGetPacket()讀取視頻流數據包送去解碼器進行解碼。

3)加速引擎初始化和利用消息總線進行解碼數據通信,通過Engine_open()打開H264解碼引擎,Viddec3_create()創建一個解碼實例對象,Viddec3_control()設置解碼所需的參數,Viddec3_process()將用RPMsg消息總線送出解碼數據流并接收解碼后的圖像緩存數據,其流程圖如圖5所示:

3.2 Cortex-M3軟件實現

雙核Cortex-M3運行TI BIOS實時操作系統,負責與主處理核的virtio緩存隊列通信及通過codec engine調用IVA-HD加速引擎實現H264解碼,運行流程圖如圖6所示,主要包括以下內容:

1) virqueue_create(&send_queue),virqueue_create(&recv_queue)創建與Cortex-A9主處理核通信的 virtio發送及接收緩存隊列。

2) Message_get_queue(&recv_queue)從virtio緩存隊列獲取主處理核發過來的請求數據,Message_send_queue派發到App M3的消息隊列中。

3) App M3將獲取消息鏈表的消息,設置IVA-HD加速引擎的工作狀態并初始化,如果為解碼消息則通過Codec Engine 調用IVA-HD加速引擎來完成解碼過程。

4) 將解碼后的圖像緩存封裝成virtio緩存,調用Message_send_queue()通過virtio緩存隊列發送回主處理核A9調用DRM進行顯示輸出。

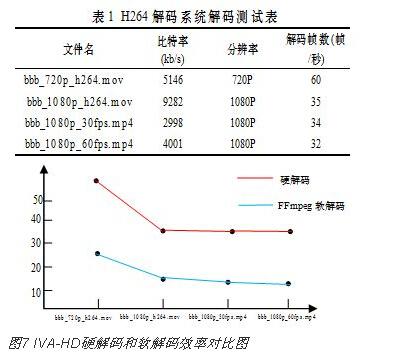

4 測試

本文在OMAP4430開發平臺上設計實現了基于異構多核的全高清H264解碼,為了測試解碼器的性能,將針對不同比特率的720P、1080P 的網絡視頻文件Big_Buck _Bunny_Sunflower 進行解碼測試,測試結果如表1所示,同時采用FFmpeg開源庫項目的軟解碼進行測試,其對比圖如圖7所示

圖7 IVA-HD硬解碼和軟解碼效率對比圖

從圖6可以看出本次設計的H264解碼器在解碼720P(1280*720)和1080P(1920*1080)視頻時分別達到60和34幀每秒,相比FFmpeg開源H264軟解碼器效率提高了一倍。而普遍全高清流暢視頻的幀率為30幀每秒,達到實時解碼性能需求。

5 結束語

隨著移動互聯網時代的到來,在移動終端上流暢播放全高清視頻成為任務日常需求。為此本文采用移動Soc OMAP4430異構多核處理器為實驗平臺,通過基于virtio緩存隊列和RPMsg消息框實現了異構多核間多媒體數據通信,同時結合IVA-HD多媒體硬件加速引擎設計了一款全高清H264視頻硬解碼系統。實驗結果表明設計的解碼系統比開源FFmpeg軟解碼器在性能上提升了一倍,達到實時性要求。具有解碼速度快、解碼過程由硬件加速器完成無需消耗主核運算資源、核間通信效率高、功耗小等優點。

-

處理器

+關注

關注

68文章

19160瀏覽量

229120 -

視頻

+關注

關注

6文章

1933瀏覽量

72810 -

互聯網

+關注

關注

54文章

11105瀏覽量

103012

發布評論請先 登錄

相關推薦

x4418開發板支持Linux平臺下H264硬件編解碼

H264硬件解碼驗證

創龍帶您解密TI、Xilinx異構多核SoC處理器核間通訊

Jacinto6 SoC上VISION SDK和PSDKLA之間的IVA-HD共享

采用異構多核處理器結合IVA-HD設計高清H264視頻硬解碼系統

采用異構多核處理器結合IVA-HD設計高清H264視頻硬解碼系統

評論