1 引 言

近年來,隨著網絡和多媒體技術的發展,視頻信息通信的重要性和需求急劇增長,而其中的關鍵就在于視頻壓縮編碼技術的應用。提出了一種基于TMS320DM642 DSP的視頻編碼方案,實現了H.264算法。同H.264相比,MPEG4具有軟硬件開發成本低和更容易實現的優勢,是目前視頻編碼應用的主流。本文提出了一種基于TMS320DM642 DSP的MPEG4視頻編碼器的實現方法,該方案可用于遠程視頻監控、視頻會議等諸多領域。

MPEG4是由國際運動圖像專家組(MPEG)開發制定的國際通用視頻壓縮編碼標準,目前已經發展成為可適應不同傳輸帶寬、可用最少的數據來獲得最佳質量圖像的高效壓縮算法和工具。MPEG采用了DCT、量化、熵編碼等算法,通過對形狀、運動、紋理等信息的分析,消除圖像數據在時間和空間上的相關性,具有高效壓縮性及普遍適用性等獨特優勢,為視頻信息高效存儲、傳輸提供了方便。

MPEG4為不同的應用對應的碼率、分辨率、質量和服務定義了編碼器和碼流的不同框架和級別,其中的簡單框架提供了對矩形視頻對象的編碼功能。本文所實現的就是MPEG4視頻編碼算法的簡單框架。

2 MPEG4編碼器硬件平臺

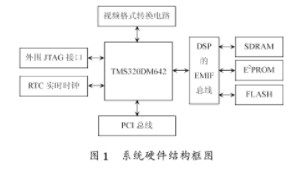

實現MPEG4編碼器的硬件平臺以TMS320DM642DSP為核心,并配合以適當的外部存儲器SDRAM,FLASH等外圍設備。

2.1 TMS320DM642特性

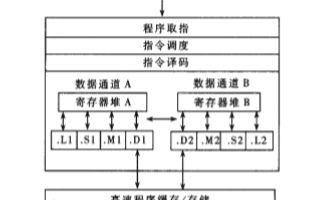

TMS320DM642是TI為多媒體應用而開發的基于C64x內核的高性能定點數字信號處理器,時鐘頻率600 MHz,最高處理能力可達4 800 MIPS。DM642具有C6000系列DSP的公共定點指令集,增加了多媒體擴展指令,可以更加方便快速地執行圖像處理中的算法。DM642的這些特點,使其非常適合于視頻圖像處理,是實現MPEG4視頻編碼器的理想硬件平臺。

2.2 硬件系統結構

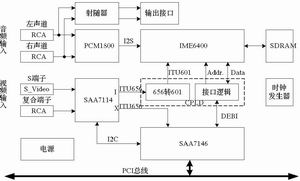

DM642作為整個系統的核心,對視頻數據進行高速處理,完成MPEG4編碼算法;可編程視頻格式轉換電路將輸入的原始視頻數據進行預處理,轉換成編碼器可接受的視頻格式的數字信號;E2PROM和FLASH用來固化應用程序和初始化參數,SDRAM作為片外存儲器,在編碼過程中存儲待處理的視頻數據,以上三者通過EMIF總線與DM642連接;通過JTAG接口,利用CCS,可方便地實現系統軟硬件仿真與調試;實時時鐘為數字視頻提供實時時間基準信息。

3 MPEG4編碼器的軟件實現和優化

3.1 MPEG4的軟件實現

MPEG4是一個開放的框架標準,并沒有規定具體的算法和程序,用戶可根據需要自行開發代碼,我們采用了XVID 1.1.0開放源碼來實現MPEG4編碼器。XVID代碼實現了MPEG4的簡單框架算法,不需要形狀編碼,只對I-VOP和P-VOP進行編碼。但XVID是針對PC機應用而設計開發的,要將他移植到DSP中,必須對代碼進行分析,結合DSP的指令結構和特點進行修改。

XVID代碼實現的MPEG4編碼器,以原始視頻數據中的每一幀作為一個視頻對象,首先判斷是I幀還是P幀,I幀需要對整幀圖像數據進行編碼存儲,P幀則進行運動估計和補償,只編碼當前幀與參考幀之間的圖像殘差和運動矢量。每幀數據都被分為16×16宏塊,每個宏塊又分為8×8子塊,在宏塊和子塊的基礎上進行DCT、量化、VLC編碼。基于不高的圖像質量需求,我們減化了XVID的某些功能,如GMC(全局運動補償)、RVLC等,減少了代碼運算量,降低了復雜度。

3.2 代碼優化

為提高代碼執行效率,必須結合DSP的特點對代碼進行優化,優化主要分為3個層次:

3.2.1 項目級優化

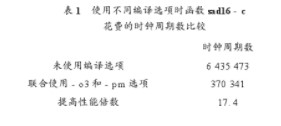

TI提供了功能強大的集成開發環境CCS,包含了各種高效的編譯工具,在代碼編譯過程中,通過使用編譯器提供的編譯選項(如-o3和-pm等),編譯器可自動改善代碼結構,減少代碼中指令的相關性,通過軟件流水等方法,提高指令并行性,改善循環性能,并可以優化代碼的尺寸。

3.2.2 C語言程序級優化

通過使用CCS中的profile工具,對C代碼進行評估,找出運算量最大的程序段,如DCT、量化、運動估計等,這部分代碼的優化對提高編碼器性能有顯著影響,我們采用了以下C程序級優化方法:

(1) 使用C6000 DSP特有的關鍵字和內聯函數來改寫C代碼,如使用關鍵字restrict可消除數據間的相關性以提高代碼并行執行能力,而使用內聯函數(如_add2(),nassert())可快速優化C代碼,作為直接映射為內聯C6000指令的特殊函數,可提高代碼在DSP中的執行效率。

(2) 使用整型訪問短型數據,使用32位整型一次訪問2個16位短型數據,分別存放在32位寄存器的高、低16位字段,可減少對內存的訪問次數,將程序讀取數據的效率提高一倍,再使用能同時對2個寄存器對應高低16位進行操作的內聯函數,如add2();mpy2()等,可大大提高代碼執行效率。

(3) 采用循環展開的方法,將多循環變為少循環甚至單循環,減少循環嵌套,消除冗余循環,可以提高指令并行執行的程度。

(4) DSP沒有專門的硬件除法運算單元,除法都用連續減法實現,運算量比較大,所以要盡量減少除法運算,不能減少的除法用移位運算來實現,可減少運算耗時。

(5)使用TI圖像庫函數。TI提供了功能強大的IM-AGE庫支持,包括了很多圖像處理常用函數,如8×8子塊的DCT變換(IMG_fdct_8×8)、SAD計算(IMG_sad_8×8),這些函數都是優化過的,代碼效率很高,可直接應用到程序中。

3.2.3 匯編程序級優化

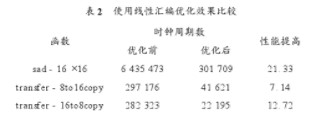

線性匯編語言是C6000系列DSP所特有的一種編程語言,類似匯編,但不需要給出指令使用的功能單元、寄存器、并行性等細節信息,匯編優化器可根據代碼情況自動確定。我們將代碼中運算量大、調用頻率高的關鍵部分用線性匯編進行了改寫,如量化、DCT、SAD等模塊,進一步優化了循環迭代、提高了指令的并行性效果。表2給出了改寫前后幾個函數模塊程序對3幀foreman.qcif測試序列編碼時消耗的時鐘周期數對比。

3.3 存儲空間的配置

DSP的片上存儲空間有限,編碼器要處理的大量視頻數據(包括當前幀和參考幀等圖像)必須放在片外,而CPU訪問片外的速度要比訪問片內慢很多。利用DM642的EDMA功能,CPU對前一幀數據編碼的同時,通過ED-MA通道提前將片外的數據搬移到片上內存,二者并行工作,提高了數據由片外傳輸至片內的效率,可減少CPU等待時間。

3.4 實驗結果

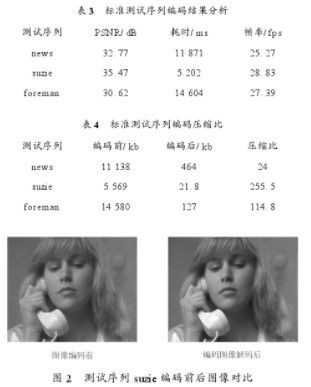

使用編碼器對標準qcif格式(176×144)測試序列進行編碼來測試編碼器性能,其中news序列300幀,suzie序列150幀,foreman序列400幀,通過TI的集成開發環境CCS 2.0進行硬件仿真實驗,在設定碼率為100 b/s的條件下。

通過分析測試序列編碼結果,編碼器的編碼速率達到25 fps以上,可以滿足實時編碼的要求。在傳輸碼率降低的情況下,編碼速率還可以進一步提高。從編碼結果可以發現,不同測試序列編碼前后的壓縮比不同,這是由于測試序列圖像的運動情況、背景變換造成的,如suzie序列背景單一,運動緩和,壓縮比較高,而news序列由于背景不斷變換,壓縮比就相對較低。通過對比編碼前和編碼后解碼得到的圖像,畫面無失真現象,圖像質量并沒有明顯下降。

4 結 語

本文探討了MPEG4編碼器在DM642上的實現方案和優化的方法,實現了MPEG4編碼的簡單框架算法。實驗結果表明,本文所提出的方案具有較高的易實現性和實用性,增加和改進的代碼優化方法是有效的,性能測試獲得了滿意的效果。在此基礎上,我們還可進一步對實現MPEG4高級框架和代碼優化方法的改進,進行更深入地研究,以滿足更高的應用要求。

-

處理器

+關注

關注

68文章

19160瀏覽量

229115 -

編碼器

+關注

關注

45文章

3594瀏覽量

134147 -

數字信號處理器

+關注

關注

5文章

456瀏覽量

27331

發布評論請先 登錄

相關推薦

基于DSP的MPEG2的視頻編碼器設計與實現

怎么實現基于C6000系列DSP的MPEG-4視頻編碼卡的軟硬件設計?

基于ARM的MPEG 4視頻編碼器

MPEG-4 ASP視頻編碼器的軟件優化設計

基于MPEG4硬件編碼的視頻監控系統的實現

MPEG4圖像壓縮

基于MPEG-4的視頻DCT編碼器的實現

基于數字信號處理器實現MPEG4視頻編碼器的軟硬件設計

基于數字信號處理器實現MPEG4視頻編碼器的軟硬件設計

評論