引言

對于IO互聯體系架構的復雜要求是系統工程化應用需要直接面對的挑戰。DSP互聯技術的研究已經成為新興的熱點問題。

DSP之間互聯的方式有很多種,高帶寬的片間、板間互聯技術成為需要重點突破的關鍵技術。

1 高速互聯點對點交換技術

無論是單分段共享總線互聯系統,還是級聯的多分段共享總線互聯系統,在這類基于共享的總線體系結構中,所有通信無不是在爭用總線帶寬,由此造成外設越多可用帶寬就越少,從而帶來嚴重的傳輸瓶頸。不僅如此,在基于共享的并行總線上,大量的引腳數目也帶來一定的電氣特性和機械特性等問題,使得信號頻率以及信號可傳輸距離都受到很大程度的制約。

因此,需要一種可升級的新型高性能系統體系結構,于是出現了點對點交換式總線,典型的新型總線有PCI-Express、InfiniBand、Hyp erTransport、RapidIO等。

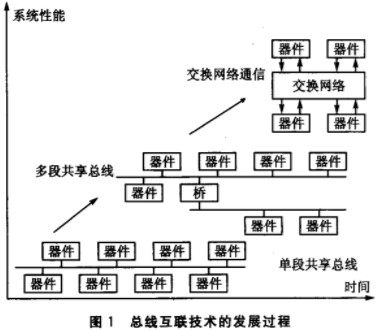

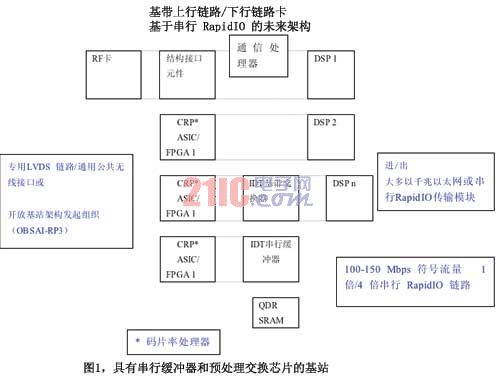

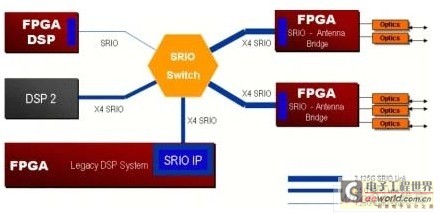

總線互聯技術的發展過程如圖1所示。其中,Infiniband的目標應用是系統域(SAN)互聯,系統域網絡用于構建集群系統以得到更大的系統。RapidIO互聯架構是一個開放的標準,可以滿足嵌入式基礎設施在應用方面的廣泛需求。HyperTransport和PCI-Express雖然具有某些與RapidIO相同的特征,但把它們視為PCI總線的點到點版本更為恰當。

在這幾種新型總線技術中,RapidIO主要面向高性能嵌入式系統互聯通信,是一個開放的點對點分組交換標準,可連接多處理器、存儲器、網絡設備中的存儲器映射I/O器件、存儲子系統等。這一互聯技術可以實現1~60Gbps的性能水平,可以在8對LVDS差分線上實現全雙工的10 Gbps數據傳輸。RapidIO以其高帶寬、低延時及具備硬件保證達99.999%的高可靠性(即系統處于出錯狀態的時間僅為0.001%)為多核DSP系統的互聯提供了良好的解決方案。

2 基于RapidIO多核DSP系統高速互聯的設計

2.1 RapidIO IP核的設計

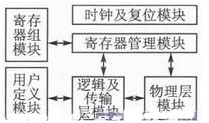

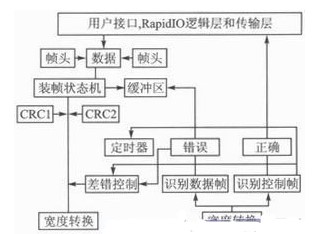

RapidIO IP核可以分為6大部分:邏輯及傳輸層協議實現。包括負責事務組包、拆包等功能的邏輯及傳輸層模塊;物理層協議實現,包括包的控制符號傳送、流量控制、錯誤管理等功能的物理層模塊;負責對寄存器進行讀寫操作的寄存器管理模塊;集中實現各層寄存器的寄存器組模塊;時鐘及復位模塊;用戶定義模塊。其結構如圖2所示。

2.2 多核DSP互聯接口總體方案

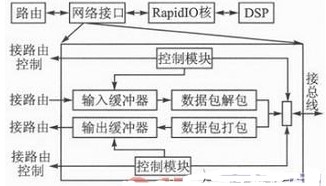

越來越多的高速信號處理系統采用多DSP核進行數據運算,用可擴展的RapidIO構建互聯結構是非常有效的一種方式。例如一個可擴展的4核DSP系統,網絡采用4×4的mesh拓撲結構,在4塊芯片上實現,芯片內部互聯采用并行總線,芯片之間互連采用基于RapidIO物理層協議的高速串行總線,結構如圖3所示。

這樣的設計并非把RapidIO應用集中,把單個芯片作為RapidIO拓撲結構的一個節點,而是把整個片上網絡作為RapidIO拓撲結構的一個節點。網絡內部的協議完全自定義,不僅能利用RapidIO接口對基于片上網絡架構的多核DSP系統作片外擴展,又能使片上網絡的拓撲結構不依賴于RapidIO獨立設計。因為在RapidIO的拓撲結構中,數據交換的單元是交換開關,而本設計中數據交換由獨立于RapidIO協議的路由器來完成。如果需要兼容其他的總線協議,只需要更改網絡接口的設計,極大地簡化了工作。

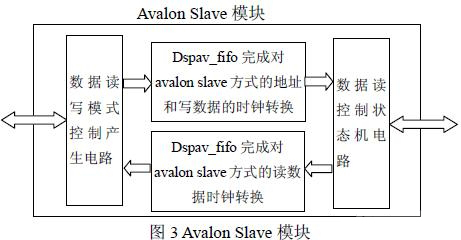

2.3 4核DSP網絡接口的結構

為了實現多核DSP之間的數據通信,互聯接口必須能夠解析來自片上網絡的數據包并轉換成RapidIO IP核所需要的數據格式,或者接收來自RapidIO IP核的數據,并按照網絡協議組裝成數據包在網絡上發送,實現片上網絡同片外DSP核的通信。互聯接口要支持不同時鐘域的數據傳輸,滿足片上網絡全局異步、局部同步的時鐘要求,還需要能夠檢測來自網絡數據包的錯誤,保證可靠傳輸,并使用基于信用量的流控機制,防止緩沖器溢出造成數據丟失。網絡接口使用多個虛通道技術緩解網絡死鎖,提高網絡的吞吐率。根據這些要求設計的多核DSP互聯接口結構如圖4所示。

4個DSP通過串行RapidIO互相連接起來,在幾個DSP內部利用串行RapidIO協議,數據在幾個DSP之間高速運轉。另外,還可以通過一個外部的控制處理器來實現控制這幾個DSP的一些功能,可根據需要給每個DSP分配不同的算法模塊,對多個DSP進行負載均衡,從而實現更高的運算效率。

3 RapidIO專用電路中核心IP模塊設計

RapidIO協議可以用大規模集成電路來實現,通過協議本身的控制作用完成對數據通路的控制作用。因此RapidIO專用集成電路就是基于這個協議的框架結構,從根本上解決嵌入式系統互連的通信問題,從而提高系統的整體性能。

3.1 發送和接收IP模塊設計

發送和接收模塊主要圍繞采用的雙端口存儲器進行復雜的控制邏輯設計。根據協議的要求,可在RapidIO專用電路的雙口SRAM中規定一個口寫數據,一個口讀數據,從而降低控制邏輯設計的復雜性。在本設計中規定A口是只寫的,而B口是只讀的,它們的數據寬度為32位,深度為1024。

3.1.1 發送緩沖IP模塊設計

在雙口SRAM的外圍設計了較復雜的控制邏輯構成發送緩沖區,A口和B口的地址計數器的地址由兩部分組成:ID號和地址遞加計數邏輯。A口的輸入數據來自于RapidIO封裝的數據幀,而B口的輸出數據又被送到了RapidIO發送狀態機內,只不過B口的數據是需要重發的數據。

因為RapidIO數據幀最大為68個雙字,發送窗口數被設計成7,所以已經發送的數據在這個雙口SRAM中是分段保存的。當RapidIO發送狀態機開始發送數據,同時對數據進行封裝時,A口的寫信號有效,并且A口的計數器進行遞增計數,遞增計數器和段地址構成了A口的有效地址。這樣已發送的數據就被保存在這個以雙口SRAM為核的緩沖區隊列中(最多為476個雙字數據)。在這個雙口SRAM的外圍設計了段指示變量用來指示在該段中保存字數據的個數(因為發送的數據可能有不夠256個字節,即64個雙字的情況)。

相鄰節點返回的數據響應幀內,包含相鄰節點希望接收的下一個數據幀的序號ID,當數據響應幀類型為datanot accept或data retry類型時,激活了發送狀態機內的重發機制,B口當前地址和A口的段指示變量進行比較,當B口的當前地址和A口相應的段指示變量相等時,通知發送狀態機該數據已經被重新發送完畢,結束幀的發送。只有該幀數據的正確的響應幀被接收到時,A口才能繼續發送新的數據,并且發送緩沖區的窗口向前滑動。通過使用這種方法,已發送的數據就源源不斷地保存在這個緩沖區隊列中,而且不會丟失。

3.1.2 接收緩沖IP模塊設計

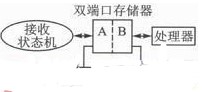

在雙口SRAM的周圍加入了一些外圍的控制電路構成了接收緩沖區。雙口SRAM的A口和接收狀態機相連,雙口SRAM的B口和處理器接口相連。A口和B口分別使用了地址計數邏輯。接收緩沖IP模塊如圖5所示。

由于RapidIO的一個數據幀是以272字節封裝的,并且在數據幀的第80個字節處插入了一個CRC校驗序列,這樣就增加了判斷的難度。當接收機開始接收數據幀內嵌入的第一個CRC校驗序列時,通過接收狀態機進行判斷:當接收到的第一個CRC校驗序列和接收狀態機本地產生的CRC一樣時,A口的地址計數電路繼續計數;當接收到的第一個CRC校驗序列和接收狀態機本地產生的CRC不一樣時,說明前面接收到的數據是無效的,此時地址計數電路停止計數,并且地址指示變量減去20。

當接收完一個數據幀內的所有有效數據時(不包括數據幀末尾的CRC校驗碼),地址計數電路停止計數,同時在接收狀態機內進行判斷:當接收到的數據幀末尾的CRC校驗序列和接收狀態機本地產生的CRC校驗序列一致時,地址指示變量的值不變;當接收到的數據幀末尾的CRC校驗序列和接收狀態機本地產生的CRC校驗序列不一致時,地址指示變量減63(標準的數據幀內的有效數據是64個字)。通過這樣的方法在由這個雙口SRAM構造的接收數據緩沖區內保存了一個完整有效的數據幀。

3.2 發送/接收狀態機

發送狀態機和接收狀態機模塊包含了RapidIO協議的差錯控制和流量控制的功能。差錯控制功能主要是通過使用CRC校驗機制和定時器機制來完成的。發送狀態機和接收狀態機是通過相互交換內部信息來實現對數據進行差錯控制和流量控制的,如圖6所示。

3.2.1 發送狀態機模塊設計

如圖6所示,來自處理器接口的原始數據依次傳送到RapidIO的邏輯層和物理層時,在數據的頭部封裝了地址、序號和長度等頭部信息,同時發送狀態機得到每個數據的CRC碼;當數據大于80個字節時,在第80個字節的后面插入1個CRC碼,然后在該數據幀的尾部插入1個CRC碼,這樣就將一個原始的數據轉換成了1個RapidIO數據幀,然后將這個封裝的數據幀傳到串行化數據模塊進行發送。

如果數據幀被對方節點正確的接收,則發送端口可以繼續發送數據;如果數據幀被對方拒絕接收,則停止數據的繼續發送,并且接收端口和發送端口通過同步控制幀重新進行端口同步,當這種同步重新建立后發送端口才可以繼續發送數據;在發送狀態機模塊中采用了滑動窗口技術,一方面可大大提高數據的吞吐量;另一方面可以盡量避免由于接收方緩沖區資源不足而導致的多次發送失敗。

3.2.2 接收狀態機模塊設計

當接收到數據幀后,對接收到的數據幀通過CRC校驗機制進行錯誤檢查,同時得到幀的序號和設備號等信息,并且將數據幀的接收狀態通知本地發送端口,由本地發送端口根據接收數據的狀態作出判斷,然后向對方節點設備發送響應幀信號。

當接收狀態機接收到一個完整的消息后,則由接收狀態機向本地處理器接口發出中斷信號,通知處理器將接收緩沖區內的數據取出;當接收狀態機接收到控制幀后,根據控制幀的類型作出判斷,如果是錯誤數據的響應幀,則本地發送端口和接收端口同時處于停止發送和接收數據狀態,并且通知本地發送端口發送link請求幀和link相應幀,使得接收和發送鏈路重新建立連接;如果是用于鏈路控制的控制幀,則本地發送端口根據接收到的控制幀類型向相鄰節點發送相應的響應控制幀。

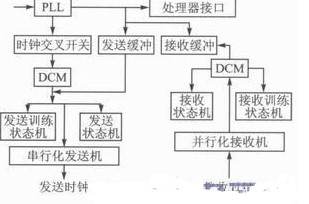

3.3 時鐘信號設計

RapidIO協議規定使用雙數據時鐘發送和接收數據。

在專用電路內的時鐘布局分為發送時鐘模塊和接收時鐘模塊兩大子模塊。對時鐘的分頻和倍頻是通過專用集成電路內的數字時鐘管理器DCM完成的。來自處理器的輸出時鐘要驅動專用電路芯片和其他外設,所以在專用電路的內部加入PLL,保證輸出時鐘能提供足夠的時鐘頻率、驅動能力和較陡的時鐘邊沿。時鐘資源在專用電路內的布局如圖7所示。

發送時鐘模塊的主要功能包括:

①使用DCM的相移功能,提供RapidIO發送數據合適的采樣時鐘相位,包括從發送緩沖區將數據提取出來,以及在發送數據前提供的較好的冗余時鐘相位,保證時鐘能正確地采集發送的數據和幀同步信號。

②在進行數據串行化的時候,通過DCM的倍頻功能將上層模塊的數據發送變成雙數據進行發送,即時鐘的上沿和下沿同時發送數據。

③通過差分引腳將LVTTL發送時鐘變為LVDS差分時鐘進行發送。

接收時鐘模塊中的主要功能包括:

①接收到的差分LVDS時鐘轉換為LVTTL時鐘。

②對接收到的時鐘信號通過DCM對其進行分頻,以便能夠正確地將接收到的DDR數據轉化為SDR數據。

③對接收到的時鐘通過DCM進行相位移動,以便為接收緩沖區正確地接收數據提供正確的采樣時鐘相位。

除了此處提到的模塊,RapidIO協議專用集成電路內部還有串行和并行模塊,接口模塊等,在此就不一一介紹了。

結語

適用于多核DSP系統的高速互聯接口對于研究多核的體系結構具有實際意義。研制滿足RapidIO協議的專用集成電路不僅可以快速實現網絡結構,而且可以降低系統的功耗,提高可靠性,具有很好的應用價值。

-

dsp

+關注

關注

552文章

7962瀏覽量

348310 -

嵌入式

+關注

關注

5072文章

19026瀏覽量

303524 -

IP

+關注

關注

5文章

1664瀏覽量

149345

發布評論請先 登錄

相關推薦

怎么利用FPGA實現DSP與RapidIO網絡互聯?

如何實現DSP與RapidIO網絡互聯?

怎么實現基于RapidIO的雙主機節點嵌入式系統互聯的設計?

看看在SpinalHDL中AXI4總線互聯IP的設計

基于FPGA的串行RapidIO-PCI轉接橋設計

基于Wishbone片上總線的IP核的互聯

基于FPGA實現DSP與RapidIO網絡互聯

基于RapidIO和存儲映射的高速互連網絡

首款串行RapidIO 2.1 IP 解決方案(Altera

基于FPGA實現DSP與RapidIO網絡互聯

串行RapidIO提升模塊化基站設計

利用串行RapidIO實現FPGA協處理

基于AXI總線的RapidIO端口控制器IP核的設計方法

基于串行RapidIO總線互聯的核心IP設計

基于串行RapidIO總線互聯的核心IP設計

評論