前言

隨著通用移動(dòng)通信系統(tǒng)(UMTS)網(wǎng)絡(luò)在日本和歐洲實(shí)現(xiàn)商用,市場(chǎng)對(duì)多頻段寬帶碼分多址(W-CDMA)收發(fā)器芯片的要求更加苛刻——除了縮小芯片面積和主板占用空間、減少組件數(shù)量、降低材料成本外,還要求芯片具備足夠的靈活性,不僅要支持工作頻段I,還要支持其他多個(gè)頻段。考慮到UMTS的全雙工性質(zhì),再加上支持所有頻段要求在面積更小的芯片上集成多個(gè)發(fā)射和接收通道,如何最大限度降低這些通道之間的串?dāng)_,就成為一個(gè)非常具有挑戰(zhàn)性的任務(wù)。第一顆采用0.13微米CMOS工藝制造的單芯片直接轉(zhuǎn)換收發(fā)器于2003年2月面世;第一顆采用0.35微米SiGe BiCMOS工藝制造的單芯片 UMTS收發(fā)器于2004年正式推出。最新發(fā)布的直接變換設(shè)計(jì)包括一個(gè)采用0.35微米SiGe BiCMOS工藝制造的適用于WCDMA/HSDPA網(wǎng)絡(luò)的三頻段單芯片收發(fā)器。

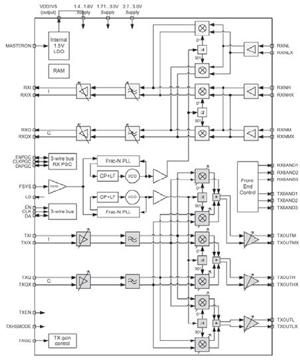

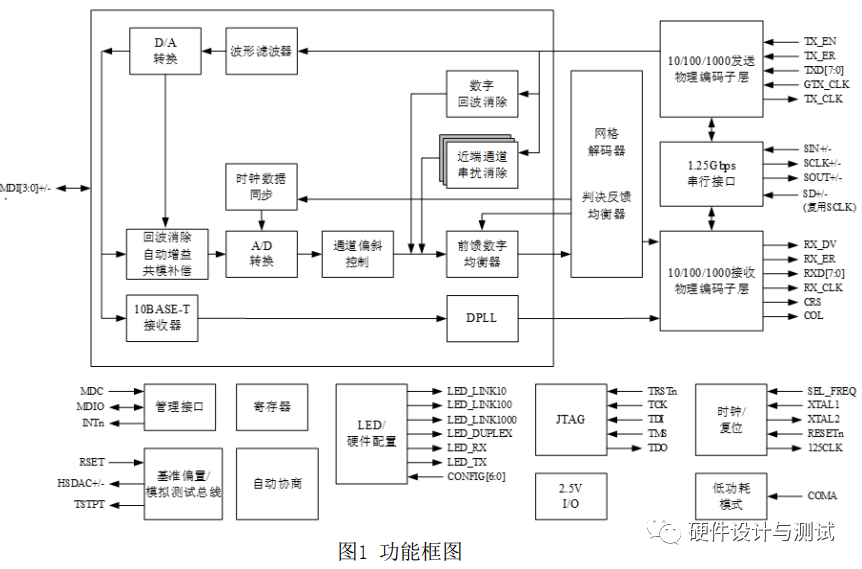

本文介紹了一種適用于頻分復(fù)用(FDD)網(wǎng)絡(luò)的低功耗、多頻段、全集成化單芯片UMTS W-CDMA/HSDPA直接轉(zhuǎn)換型收發(fā)器。它采用 0.13微米CMOS工藝制造而成。該設(shè)計(jì)包括三條零中頻接收(RX)通道,三條直接轉(zhuǎn)換型發(fā)射(TX)通道,兩個(gè)分?jǐn)?shù)型頻率合成器。它們都由一個(gè)多標(biāo)準(zhǔn)編程接口控制。圖1顯示了該芯片的完整框圖。

接收器包括差分輸入端口、第二低噪放大器級(jí)(2nd LNA)、兩個(gè)下變頻器(帶CMOS Gilbert型混頻器以及緊隨其后的低噪緩沖放大器)、一個(gè)經(jīng)過(guò)校準(zhǔn)的模擬有源六階基帶(BB)濾波器,并且伴隨一個(gè)附加的二階可編程陷波濾波器(2.7 MHz)。所有直流偏置由內(nèi)部電路補(bǔ)償。

該收發(fā)器包括一個(gè)Butterworth型三階模擬有源基帶濾波器,以及三個(gè)直接上變頻器、可變?cè)鲆娣糯笃?/u>(VGA)級(jí)(每條通道的增益控制范圍超過(guò)85dB)、高功率輸出驅(qū)動(dòng)級(jí)(典型輸出功率為11dBm)。VGA級(jí)的自適應(yīng)偏置,可確保整個(gè)輸出功率范圍內(nèi)功耗最低。

混頻器包括全集成式壓控振蕩器(VCO),后者集成了片上調(diào)諧電路、自動(dòng)上電校準(zhǔn)和環(huán)路濾波器等功能。

所有功能均由一個(gè)基于三線制總線設(shè)計(jì)的靈活的多標(biāo)準(zhǔn)編程接口控制,這不僅實(shí)現(xiàn)了后向兼容,而且可支持DigRF標(biāo)準(zhǔn)所規(guī)定的全部讀/寫(xiě)存取操作。

該器件的工作電壓范圍為2.7 -3 V,工作環(huán)境溫度范圍為-30℃至+85℃,可配置成不同的參考振蕩頻率以及不同的基帶接口參數(shù)(例如 I/Q共模電壓),從而實(shí)現(xiàn)最佳兼容性。多種節(jié)電模式可確保各類(lèi)操作情景下的功耗最低。接收通道的最大功耗為通道的最大功耗為35mA(打開(kāi)陷波濾波器時(shí)為37mA),而發(fā)射器的功耗始終低于80mA。如果發(fā)射和接收功能都沒(méi)有啟動(dòng),一個(gè)被稱(chēng)為“睡眠模式”的特殊操作模式將被激活。在這種模式下,器件的典型功耗一般為2mA。如果移動(dòng)終端(UE)未被用于無(wú)線信號(hào)收發(fā)(例如,正在使用高級(jí)移動(dòng)終端都具有的個(gè)人數(shù)字助理(PDA)功能),這對(duì)于延長(zhǎng)電池工作時(shí)間非常有用。在睡眠操作模式下,所有的寄存器設(shè)置都保存在一個(gè)特殊的隨機(jī)存取存儲(chǔ)器(RAM)中,這樣,在下次被喚醒時(shí),集成電路就能取回所有的設(shè)置。

如果被用于多模環(huán)境,該收發(fā)器可作為功耗最低的前端控制中心,以及活動(dòng)的備用收發(fā)器(例如GSM收發(fā)器)。其實(shí)現(xiàn)方式是:激活一個(gè)特殊的工作模式,該模式可關(guān)閉發(fā)射和接收功能,從而實(shí)現(xiàn)功耗最小化,并且對(duì)所有6個(gè)前端控制輸出引腳進(jìn)行仲裁設(shè)置。

該芯片采用非常袖珍的無(wú)引腳封裝技術(shù)—PG-WFSGA-81-1 (超細(xì)間距半球珊陣列),面積僅為5×5毫米,最大高度為0.8毫米。球珊間距為0.5毫米。

一、分?jǐn)?shù)型頻率合成器

接收器和發(fā)射器都集成了參考頻率為26MHz的分?jǐn)?shù)型頻率合成器,同時(shí)搭載了參考電阻器。較低的帶內(nèi)相噪,為使用更寬的PLL環(huán)路帶寬(目的是全面集成環(huán)路濾波器)創(chuàng)造了條件,因此可最大限度減少外部組件的數(shù)量。要覆蓋所有的工作頻段(包括附加的頻率容限),在4GHz頻段工作的差分VCO有一個(gè)很寬的調(diào)諧范圍,它被劃分為256個(gè)VCO頻段。可以通過(guò)在VCO RF輸出端口激活一個(gè)附加的二分頻器以支持UMTS頻段V和頻段VI。相應(yīng)的VCO頻段由內(nèi)部的標(biāo)定算法進(jìn)行選擇,該算法將在PLL被啟動(dòng)或者一個(gè)新的頻點(diǎn)被設(shè)定時(shí)被觸發(fā)。同時(shí),進(jìn)一步的校準(zhǔn)可最大限度降低PLL的偏變,例如環(huán)路濾波器拐角頻率的離散等。

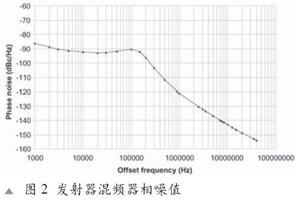

圖2顯示了混頻器相噪模擬量。

超低帶內(nèi)相噪是實(shí)現(xiàn)接收器和發(fā)射器誤差向量幅度(EVM)最小化的重要基礎(chǔ)。

二、零中頻接收器

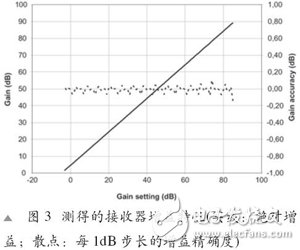

根據(jù)過(guò)去發(fā)布的一個(gè)設(shè)計(jì),每條接收通道由一個(gè)0o/90o I/Q主-從二分頻器驅(qū)動(dòng),后者可產(chǎn)生為直接將差分射頻輸入信號(hào)混頻至基帶濾波器的異常精確的正交信號(hào)。可編程增益放大器(PGA)的增益范圍為89dB,每dB步長(zhǎng)的步長(zhǎng)精度大約為0.1dB,整個(gè)增益范圍的步長(zhǎng)精度為2dB。

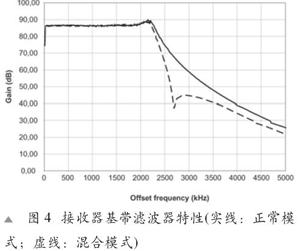

主要針對(duì)增益步長(zhǎng)采用R-2R網(wǎng)絡(luò)即可實(shí)現(xiàn)上述精確度。在解調(diào)器的后面,采用一個(gè)六階Chebychev型跳耦結(jié)構(gòu)濾波器(帶面向I/Q基帶接口的差分信號(hào))進(jìn)行抗鋸齒失真和信道隔離處理。可通過(guò)軟件編程方式激活附加的2.7MHz陷波器,從而滿足UMTS頻段II和III的要求。整個(gè)濾波器得到了優(yōu)化,最大振幅誤差為±0.5 dB,相位畸變不超過(guò)±3o。在接收器初始化期間,濾波器的2.275MHz的拐角頻率被校準(zhǔn),結(jié)果使整個(gè)采樣和溫度范圍的偏差僅為5%。基帶濾波器特性的模擬量參見(jiàn)圖4,其中,實(shí)線代表隨頻率變化的正常濾波器衰減,虛線對(duì)應(yīng)的是被激活陷波器級(jí)的特性。

為了最小化增益轉(zhuǎn)換時(shí)的DC瞬變,接收鏈中的所有運(yùn)算放大器的偏差均被校準(zhǔn)為零。一個(gè)拐角頻率為3.75KHz的附加DC環(huán)路可清除所有的殘余DC偏差。因此,在增益變化時(shí),瞬態(tài)DC偏差不會(huì)超過(guò)±50 mV。

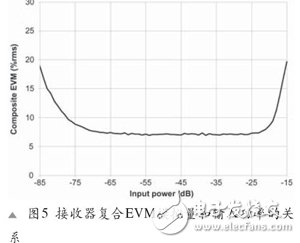

接收器的最小三階交調(diào)截取點(diǎn)(IIP3)為-6 dB,二階交調(diào)截取點(diǎn)(IIP2)大于35 dBm。高增益范圍的噪聲系數(shù)優(yōu)于12dB。最大 EVM為12.5%(有效值),使得接收器能夠被用于高速下行分組接入(HSDPA)7/8類(lèi)網(wǎng)絡(luò)。典型采樣的EVM大約為8%(有效值),如圖5所示。

三、低功耗射頻前端設(shè)計(jì)

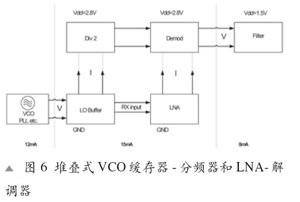

尤其對(duì)于CMOS設(shè)計(jì)而言,最重要的是最大限度降低電路功耗,從而克服該項(xiàng)工藝的固有缺陷。由于接收器的功耗是一個(gè)重要的預(yù)算參數(shù),我們選擇了一個(gè)先進(jìn)的射頻前端。依據(jù)有關(guān)文獻(xiàn)中所發(fā)布的一個(gè)設(shè)計(jì),VCO分頻器和解調(diào)器分別直接位于VCO緩存器和LNA之上。因此,兩個(gè)功能塊共用一個(gè)輸入電源,從而顯著降低了器件功耗。具體工作原理如圖6所示。

四、直接上變頻發(fā)射器

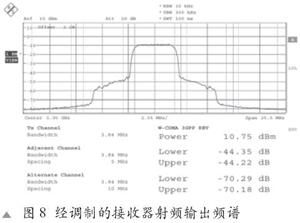

發(fā)射器內(nèi)含一個(gè)完全差分化可編程輸入緩沖器,以處理不同的基帶輸入信號(hào)。一個(gè)附加的三階Butterworth型基帶濾波器(校準(zhǔn)角頻為 4.4MHz)能夠消除各類(lèi)有害的信號(hào)內(nèi)容(譬如基帶DAC的雜散輻射等),同時(shí)不會(huì)對(duì)有用的信號(hào)產(chǎn)生過(guò)大的干擾。此外,精度高于±0.2 dB的可調(diào) -1 dB和-2 dB增益步長(zhǎng),能夠處理各類(lèi)HSDPA信號(hào)群的較高波峰因子。通過(guò)提高以下所述的增益控制輸入引腳的電壓可以補(bǔ)償衰減,并且形成一個(gè) “高線性度”模式,以符合線性度規(guī)范要求。基帶濾波器輸出信號(hào)可驅(qū)動(dòng)直接變換式調(diào)制器(每條發(fā)射通道一個(gè))中集成的Gilbert型混頻器的輸入級(jí)。由于布局高度對(duì)稱(chēng)并且完美匹配,再加上在發(fā)射器初始化時(shí)采用了一個(gè)校準(zhǔn)程序,DC偏差始終保持在很低的水平(在高輸出功率范圍內(nèi)通常為-40dBc)。射頻輸入由來(lái)自集成化VCO(高頻段和中頻段通道為二分頻器,低頻段通道為四分頻器)的0o/90o信號(hào)驅(qū)動(dòng)。混頻器的輸出信號(hào)然后被緩存,并被發(fā)送至射頻差分輸出引腳。總增益一般超過(guò)95 dB,分布在基帶和射頻模塊。通過(guò)在不同級(jí)上分配增益(按照優(yōu)化的加權(quán)因子),可實(shí)現(xiàn)VGA的近似對(duì)數(shù)線性特征。通過(guò)在增益控制引腳(TXGC)上施加適當(dāng)?shù)碾妷海?.5-2.2 V),-77dBm至+7dBm的保證輸出功率范圍(取決于所采用的UMTS頻段和發(fā)射通道)可達(dá)到控制。最大功耗(通常為80mA)可隨輸出功率的下降快速下降,在低增益范圍內(nèi)可降低至26mA。當(dāng)輸出功率最大時(shí),在相應(yīng)的接收頻段,發(fā)射通道一般可實(shí)現(xiàn)-152 dBc/Hz的本底噪聲,同時(shí)保持-43dBc的ACLR(有余量)和3%的EVM(典型值)。圖8顯示的是中心頻率為1950MHz 時(shí)的典型調(diào)制輸出頻率。

五、芯片接口

串行控制總線

該集成電路由兩個(gè)獨(dú)立的串行三線制總線控制。其中一條總線負(fù)責(zé)控制常規(guī)配置,另一條獨(dú)立的總線用于設(shè)置接收增益。編程接口可后向兼容前代產(chǎn)品并可根據(jù)DigRF標(biāo)準(zhǔn)處理相關(guān)命令。最大總線時(shí)鐘頻率等于參考時(shí)鐘頻率(15.36 MHz至38.4 MHz)。也可通過(guò)主用三線制總線(負(fù)責(zé)配置的總線)對(duì)接收增益進(jìn)行設(shè)置。在本例中,備用總線引腳可被用作GPO(通用輸出)引腳。

前端控制

由于多頻段和多模操作所導(dǎo)致的前端復(fù)雜度的加大,要求我們對(duì)外部組件(例如LNA、PA和轉(zhuǎn)換器等)進(jìn)行有效控制。因此,該集成電路包含非常靈活的軟件編程前端控制功能模塊,它可通過(guò)以事件觸發(fā)方式轉(zhuǎn)換6個(gè)專(zhuān)用輸出引腳滿足外部組件控制要求。為了確保兼容未來(lái)的前端組件(例如三增益LNA),可選擇一個(gè)電壓級(jí)別可變的附加邏輯“高”信號(hào)。

操作測(cè)試功能

可通過(guò)啟動(dòng)一個(gè)特殊的測(cè)試模式和讀回測(cè)試圖形對(duì)集成電路功能進(jìn)行檢查,例如檢查是否有所有輸入電壓等。這有助于查明生產(chǎn)過(guò)程中的焊接問(wèn)題。在操作過(guò)程中,鎖定檢測(cè)引腳邏輯狀態(tài)可跟蹤接收器和發(fā)射器PLL的鎖定狀態(tài)。利用這些信息,信道轉(zhuǎn)換防護(hù)間隔可被最小化。

六、結(jié)語(yǔ)

支持UMTS FDD標(biāo)準(zhǔn)所規(guī)定的所有工作頻段的單芯片全集成化3G UMTS/W-CDMA收發(fā)器已經(jīng)推出。該集成電路采用標(biāo)準(zhǔn)化0.13微米 CMOS工藝制造而成。該設(shè)計(jì)包括兩個(gè)分?jǐn)?shù)型頻率合成器(搭載全集成化VCO、片上調(diào)諧和PLL)、零中頻接收通道和直接轉(zhuǎn)換型發(fā)射器通道。接收器和發(fā)射器都具備出色的性能,為創(chuàng)建滿足UMTS最低性能規(guī)范(帶容限)的平臺(tái)解決方案創(chuàng)造了條件。該器件的工作電壓為2.7-3 V,接收模式下功耗為 35 mA,在發(fā)射器活動(dòng)時(shí)的最大功耗為80 mA。這些結(jié)果表明了本文所述收發(fā)器的競(jìng)爭(zhēng)優(yōu)勢(shì),因?yàn)樗赏瑫r(shí)滿足BiCMOS工藝產(chǎn)品的功耗和性能要求。該芯片采用非常袖珍的無(wú)引腳封裝,面積僅為5×5毫米,高度僅為0.8毫米,完全符合ARIB WCDMA和UMTS標(biāo)準(zhǔn)。

-

放大器

+關(guān)注

關(guān)注

143文章

13553瀏覽量

213113 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3397瀏覽量

105864 -

移動(dòng)通信

+關(guān)注

關(guān)注

10文章

2600瀏覽量

69793

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)問(wèn)0.13微米幾何設(shè)計(jì)規(guī)則與0.5微米幾何設(shè)計(jì)規(guī)則是什么

適用于承受10kV ESD的手持式計(jì)算機(jī)的RS232收發(fā)器

怎么采用標(biāo)準(zhǔn)CMOS工藝設(shè)計(jì)RF集成電路?

CMOS技術(shù)及接收器拓?fù)浣Y(jié)構(gòu)

10-37GHz CMOS四分頻器的設(shè)計(jì)

收發(fā)器的復(fù)用器電路

頻分復(fù)用怎么理解_頻分復(fù)用概念

WE2408:可直接轉(zhuǎn)換零一中頻接收結(jié)構(gòu)收發(fā)器

zpwsmileKLA-Tencor光刻工藝控制解決方案可將產(chǎn)量?jī)?yōu)化至0.13微米

XPM技術(shù)使用標(biāo)準(zhǔn)邏輯CMOS 90納米硅工藝 現(xiàn)在可用于ASIC和SoC

Fairchild LVX低壓雙電源CMOS轉(zhuǎn)換收發(fā)器的用法介紹

SM88E1111IP千兆以太網(wǎng)收發(fā)器產(chǎn)品簡(jiǎn)介

TIDA-010132-適用于雷達(dá)和電子戰(zhàn)應(yīng)用的多通道射頻收發(fā)器 PCB layout 設(shè)計(jì)

適用于頻分復(fù)用網(wǎng)絡(luò)的0.13微米CMOS工藝制造的直接轉(zhuǎn)換型收發(fā)器

適用于頻分復(fù)用網(wǎng)絡(luò)的0.13微米CMOS工藝制造的直接轉(zhuǎn)換型收發(fā)器

評(píng)論