自2005年9月LXI總線推出以來,已經顯示出其組建測試系統的眾多優點。基于LXI總線組建測試系統具有易于使用、靈活性高、模塊化和可擴縮性、實現更快的系統吞吐率、可分布式應用、長壽命、低成本、通過IEEE1588時鐘同步、機架空間小、合成儀器等諸多優點。

1553B總線的全名為"時分制指令/響應式多路傳輸數據總線",國內多型戰斗機、軍艦等武器平臺都采用其作為傳輸總線。因此研制基于LXI總線的1553B通訊模塊,不僅能滿足多型武器裝備對1553B總線的測試需求,也對LXI總線在國內的研究和應用有推動作用。

1 模塊總體方案

模塊基本設計指標為:滿足LXI規范C類儀器標準;支持DHCP、自動配置IP地址和手動配置IP地址;支持ICMP協議、TCP/IP協議和UDP協議;同步采用網絡命令方式;能完成1553B在BC模式下的所有功能。

根據指標要求采用基于SOPC的32位處理器+實時多任務操作系統(Real Time Operation System,RTOS)總體方案,在一塊FPGA芯片上集成了控制器和邏輯單元,既降低了開發的難度、減少了模塊體積,也易于以后的升級。32位處理器有足夠的資源可以擴充利用,RAM和ROM可以做的足夠大,整個TCP/IP協議族可以做到系統里面去,甚至可以嵌入一個帶TCP/IP協議族的操作系統。

2 基于SOPC的硬件設計與開發

片上可編程系統(System on a Programmable Chip,SOPC)將處理器、存儲器、I/O口、LVDS和CDR等系統設計需要的功能模塊集成到一個PLD器件上構建成一個可編程的片上系統,是一種靈活高效的SOC解決方案。SOPC結合了SOC和可編程邏輯器件各自的優點,具有靈活的設計方式、可剪裁、可擴充、可升級,并具備軟硬件在系統可編程的功能,成為SOC設計的新趨勢。

2.1 模塊硬件架構

模塊硬件主要由NiosII軟核處理器、以太網組件、1553B總線組件、存儲器、片內RAM、通用I/O接口和調試配置模塊7部分組成,架構示意如圖1所示。

圖1 硬件架構示意圖

1)NiosII軟核處理器:模塊的CPU,負責系統工作調度。在其內部移植了μC/OSII實時操作系統和LwIP協議;它接受客戶端通過以太網發送過來的請求,經解析后回復Web界面或控制1553B功能接口;2)以太網組件(DM9000A):完成對以太網控制器的操作,將網絡上的數據經以太網控制器送到網際層,由NioslI軟核處理器內的LwIP協議處理;或者將網際層送來的數據經以太網接口發送出去:3)1553B總線組件(BU-61580):受NiosllI軟核處理器控制,完成在BC模式下各類消息和命令的發送及狀態的讀取;4)Flash存儲器:主要用來存儲模塊的一些固定參數和靜態Web界面;5)片內RAM:RAM是在FPGA剩余邏輯中用Quartusll內所帶的MegaWizard管理器生成的,這樣就不需要外加RAM芯片。片內RAM主要是用來存儲程序運行過程中所接收和產生的一些數據;6)通用I/O接口:用來完成對LED或按鍵的控制;7)JTAG調試模塊和EPCS配置模塊:J1TAG模塊用來完成對程序的調試工作。配置是對FPGA的內容進行編程的過程,每次上電后都需要配置,EPCS配置模塊允許NioslI訪問EPCS串行配置器件。

具體開發主要有3部分工作:1)NiosII軟核處理器及其外設的設計。2)自定義宏功能模塊RAM的開發,這部分工作在QuartuslI軟件中完成;3)應用軟件程序的編寫,在NiosIIIDE軟件開發環境中完成。

2.2 模塊硬件設計

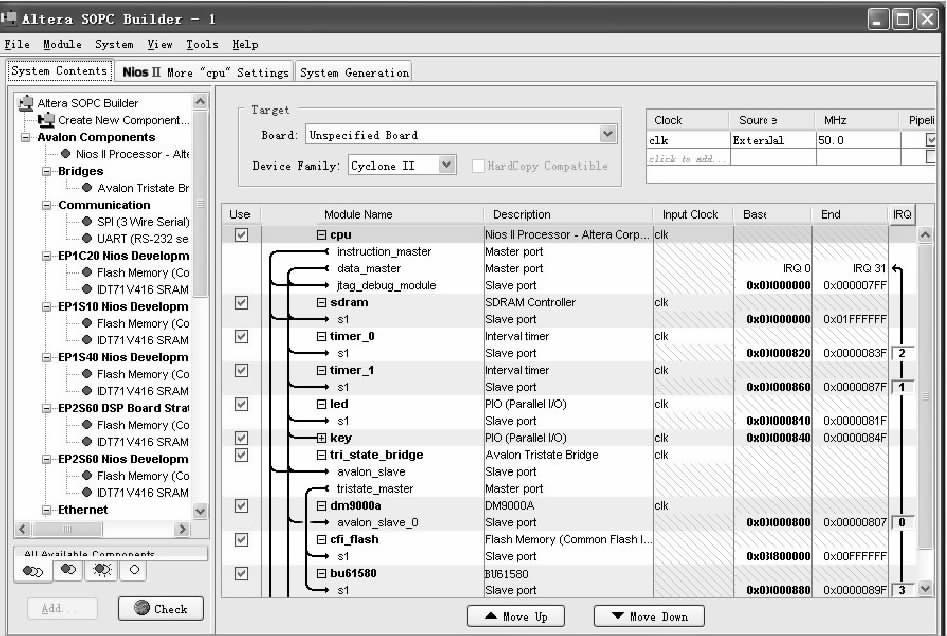

SOPC Builder是Altera公司為用戶自定義系統而開發的工具。用戶使用SOPC Builder可以將IP核、存儲器、接口、微處理器和自定義組件等復雜系統組件簡單又快速的集成到Ahera高密度FPGA芯片上。按照模塊硬件系統的要求,借助SOPC Builder生成的模塊硬件結構,包括:32位標準NiosII軟核處理器:cpu;JTAG調試接口:jtag-debug-module;外部SDRAM存儲器接口:sdram;Avalon三態橋:tri_state_brid ge;EPCS串行閃存控制器:EPCS_controller;外部FLASH存儲器接口:cfi_flash;定時/計數器:time0/timel;以太網接口:dm9000a;1553B接口:bu61580;LED接口:led;64KRAM接口:RAM;按鍵接口:key;系統識別模塊:sysid。

圖2 基于SOPC Builder的硬件系統設計

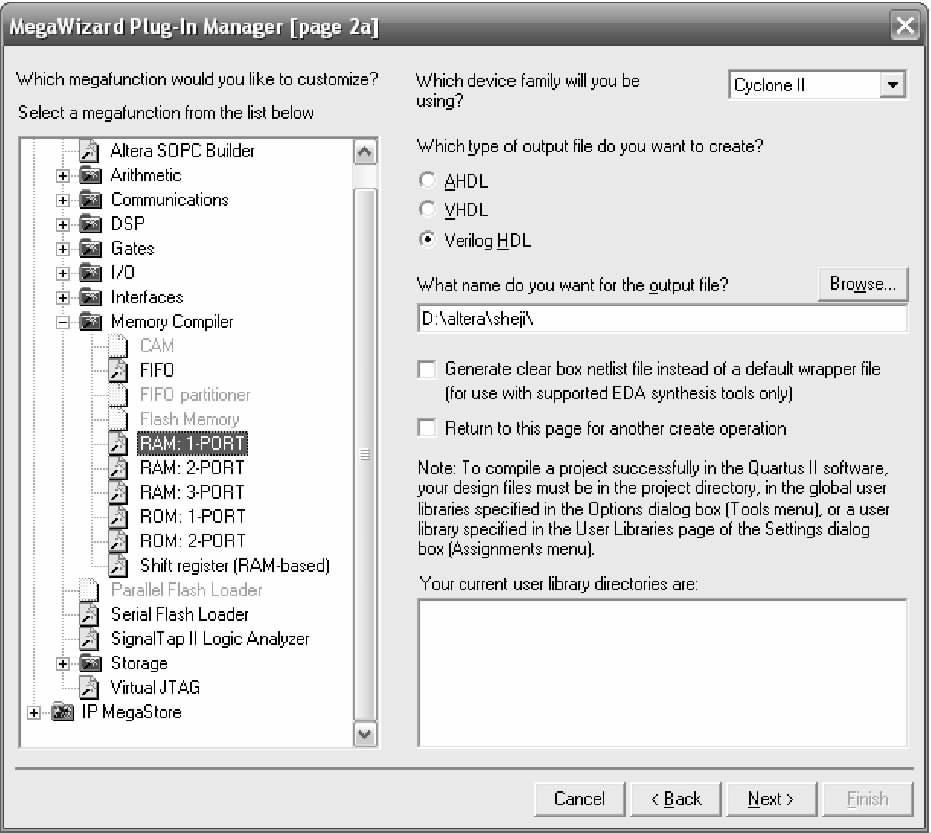

2.3 宏功能模塊RAM生成

CycloneII器件內部的RAM塊只有M4K一種,可用來實現真正的雙端口、簡單雙端口和單端口的RAM,可以支持移位寄存器和ROM方式。用QuartusII內所帶的MegaWizard管理器來生成RAM,首先運行MegaWizard管理器選擇"創建一個新的宏功能",在出現的對話框內選擇Insta lled Plug-Ins下的memory compiler下的RAM:1-PORT,如圖3所示。

圖3 MegaWizard管理器

在接下來的各頁中選擇如下參數:數據線寬度16位;存儲64個字;自動單時鐘驅動;選擇生成*.v,*.bsf,*_inst.v,*_bb.v,*_waveforms.html 5個文件。其他參數默認即可。

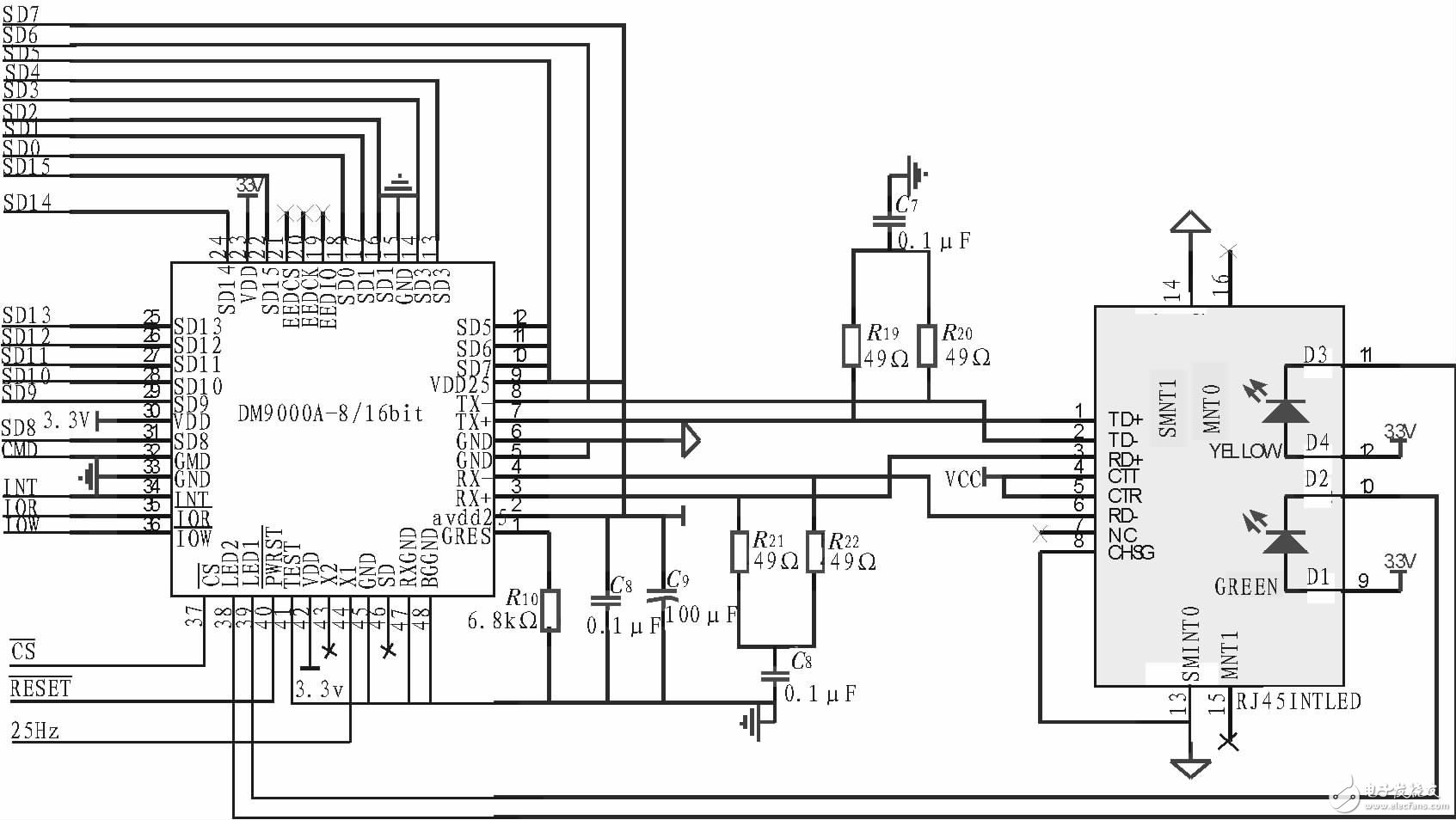

2.4 以太網接口設計

以太網控制器選用DM9000A,芯片為48管腳的LQFP封裝,支持處理器接口以字節/字模式的I/O命令操作內部存儲器數據,集成10/100M帶有AUTO-MDIX的接收器,支持用于全雙工流控制的IEEE802.3x標準,提供IP/TCP/UDP校驗和生成以及校驗過程,可選的EEPROM配置。

DM9000A與控制器和RJ45連接器的連接如圖4所示。DM9000A與控制器有兩種數據總線寬度的連接方式,即8位/16位模式,論文選用16位操作模式。DM9000A通過TX+、TX-、RX+和RX- 4條線與自帶隔離變壓器的RJ45轉換器相連。RESET引腳為DM9000A的復位引腳,低電平有效;X1外接25 Hz時鐘頻率。

圖4 DM9000A外圍連接圖

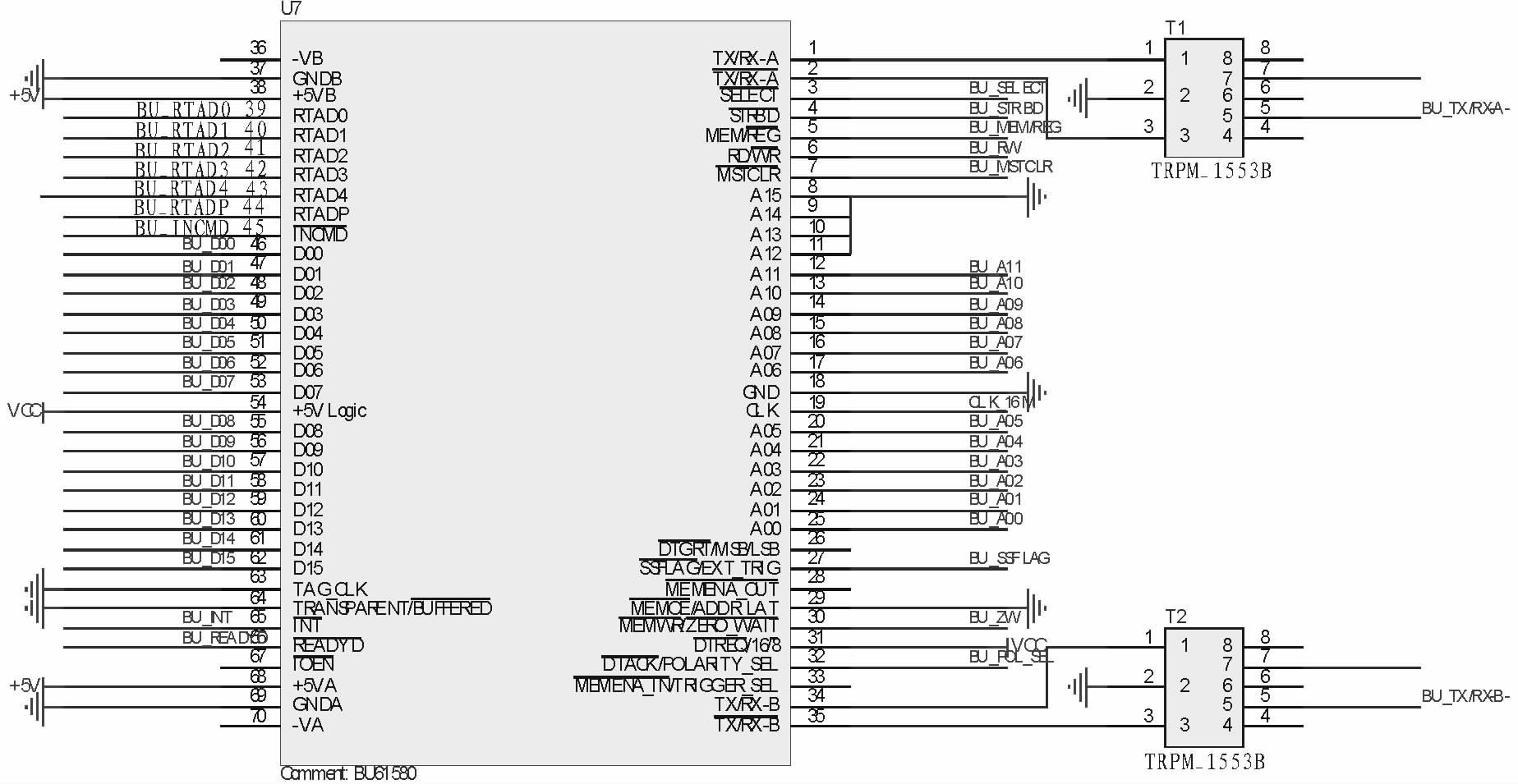

2.5 1553B接口設計

BU-61580與控制器的接口形式非常靈活,本文根據需求和資源情況選擇16位緩沖連接方式。為了提高本模塊的抗干擾性,論文采用變壓器耦合方式。BU-61580的外圍電路連接圖如圖5所示。

圖5 BU-61580的外圍電路連接圖

3 模塊軟件設計與開發

3.1 軟件結構設計

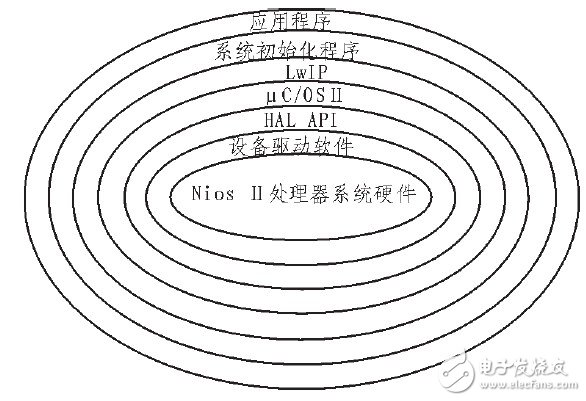

軟件結構層次由NiosII處理器系統硬件、設備驅動程序、HAL API、μC/OSII、LwIP協議棧、系統初始化和應用程序7部分組成,如圖6所示。

圖6 軟件結構層次圖

1)NiosII處理器系統硬件:模型的核心,包括在FPGA中實現的NiosII軟核處理器和硬件外設;2)設備驅動程序:管理以太網、1553B組件和其它外設的軟件函數;3)HAL API:硬件抽象層應用程序接口,對設備驅動程序提供標準化的接口,對外層提供類似于POSIX的API;4)μC /OSII:實時操作系統層,為LwIP協議棧、1553B任務和嵌入式Web任務提供多任務和任務間通訊服務;5)LwIP協議棧:通過套接字API為應用程序和應用系統初始化提供網絡服務;6)系統初始化:包括μC/OSII、LwIP協議棧和1553B組件初始化函數,也包括所有應用程序的任務、信號量、隊列和事件性標志等實時操作系統任務間通訊資源的創建;7)應用程序:最外一層是建立的各項應用任務。

應用程序工作過程如下:首先進行系統初始化,然后進入工作等待狀態。以太網任務等待客戶端通過以太網發來的數據包,當有數包到達時,經物理層處理后交于TCP/IP層處理。在TCP/IP協議層之上,建立了3個套接字接口來偵聽套接字連接:嵌入式Web端口、PING端口和1553B端口。對于1553B任務,根據客戶端不同的請求,將啟動不同的任務來完成相應的數據命令的發送或狀態的讀取。

3.2 基于μC/OSII的LwIP協議實現

輕量型IP(Light Weight IP,LwIP)協議是用于嵌入式系統開放源代碼的TCP/IP協議棧。LwIP在保持TCP協議主要功能的基礎上減少對RAM的占用,非常適合在嵌入式系統中使用。

LwIP協議棧在設計時就考慮了移植問題,把所有與硬件、OS和編譯器相關的部分獨立了出來,因此LwIP在μC/OSII上移植只需修改目錄下的文件即可。

3.3 1553B總線協議任務的實現

為方便對BU-61580芯片操作,開發了BU-61580的驅動程序。驅動程序包括BU-61580芯片的初始化函數、BC發送接收命令函數、BC發送發送命令函數、BC發送接收/發送命令函數、BC發送不帶數據字的方式命令函數和BC發送帶數據字的方式命令函數。

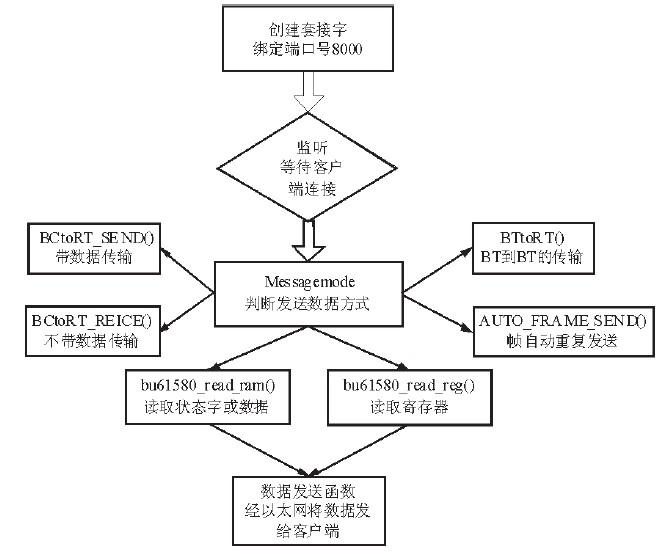

參考嵌入式Web服務器的實現方式,基于LwIP和μC/OSII建立了端口號為8000的1553B套字接口任務,流程如圖7所示。

圖7 套字接口任務程序的流程圖

首先建立1553B任務接口守護進程,創建TCP套接字,綁定端口,將TCP套接字轉換成偵聽套接字,進入循環結構,等待接受用戶的連接請求。當有客戶端請求連接端口8000時,調用套接字數據接收函數recv()將客戶端發送的數據讀取過來,將數據映射到定義的結構體變量alt_avalon_BU61580*bdev上;用請求解析函數int 1553B_request(alt_avalon BU61580*bdev)根據messagemode判斷需要采取什么操作方式:然后BU-61580的發送數據函數將數據內容寫到相應的寄存器或存儲器內,啟動BC發送;如果調用讀取數據函數,則將存儲器或寄存器地址傳遞給讀取函數,將讀取到的數據調用函數int 1553B_transmit(&bdev[i],i)經以太網打包后發送給客戶端。

4 儀器驅動程序開發

儀器驅動程序是介于上層用戶應用程序和底層儀器硬件之間的一組函數,用戶在開發上層應用程序時,可以調用這些基本動作函數來使用儀器,而無須與底層硬件通訊。

參閱VPP規范,模塊提供了基于VISA函數的儀器驅動程序。通過調用VISA函數,向模塊發送命令來完成模塊的功能。開發環境為LabWindo ws/CVI,而選用Agilent VISA作為VISA函數庫,主要是考慮Agilent是LxI總線的發起者,而且其提供的Agilent I/O Libraries封裝了許多關于LxI的功能。VISA函數所用的LxI儀器描述符有兩種:

1)對于VXI-11規范為:TCPIPO::192.168.4.10::instO::INSTR;

2)對于Sockets接口為:TCPIPO::192.168.4.10::8000::SOCKET.

其中192.168.4.10為模塊地址(非固定),8000為1553B接口任務的端口號。開發的驅動程序以動態鏈接庫形式提供給上層應用程序使用。

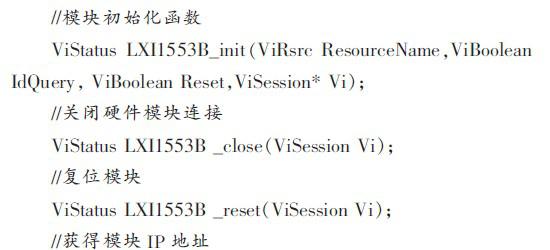

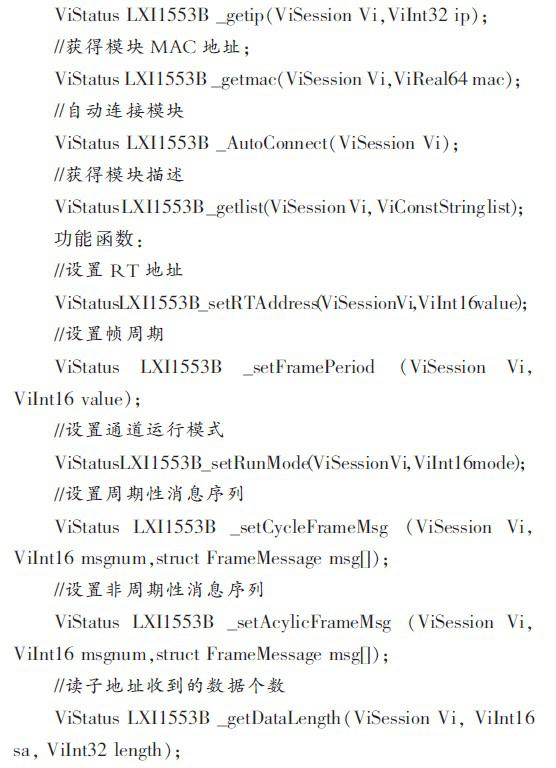

儀器驅動程的開發步驟、驅動函數原形以及發送的具體命令本文不再贅述。具體的驅動程序函數及其功能如下:

系統函數:

5 結論

針對基于LxI總線的1553B模塊開發需求,本文提出了一種利用SOPC技術實現LxI總線到1553B總線通訊的硬件解決方法。在NioslI軟核處理器上移植了μC/OSII嵌入式實時操作系統,實現了TCP/IP協議;開發了以太網和1553B自定義組件,并開發了其相應的DM9000A和BU-61580驅動程序;最終開發了儀器的驅動函數為便于模塊工程應用。

文中設計方法降低了儀器的開發難度,減少了模塊體積,同時也便于模塊的升級,具有良好的工程應用和經濟價值。

-

處理器

+關注

關注

68文章

19178瀏覽量

229201 -

存儲器

+關注

關注

38文章

7455瀏覽量

163624 -

操作系統

+關注

關注

37文章

6747瀏覽量

123204 -

總線

+關注

關注

10文章

2869瀏覽量

87997

發布評論請先 登錄

相關推薦

MIL-STD-1553B入門視頻教程 1553B總線資料課件

1553b總線

1553B總線

基于ARM的1553B總線應用

基于SOPC的1553B總線遠程終端接口設計

基于SOPC的1553B總線接口邏輯設計

基于PCI局部總線的1553B總線接口卡設計

MIL-STD-1553B入門教程_1553B總線資料課件201

1553B通訊模塊設計與開發方案

基于DSP的1553B總線系統設計解析

基于SOPC的1553B總線通訊解決方案

基于SOPC的1553B總線通訊解決方案

評論