通過(guò)在可編程邏輯器件中嵌入低成本、高性能的處理器,芯片開(kāi)發(fā)商不但能提高系統(tǒng)的整體性能,而且能夠從可編程邏輯器件原本就具備的開(kāi)發(fā)時(shí)間短、上市快的特點(diǎn)受益。利用本文談到的Floorplanner工具可以對(duì)嵌入式處理器、相關(guān)的IP和定制邏輯進(jìn)行布局控制和分組,簡(jiǎn)化復(fù)雜系統(tǒng)級(jí)芯片的開(kāi)發(fā),提高系統(tǒng)整體性能。

嵌入式處理器內(nèi)核越來(lái)越多地在FPGA設(shè)計(jì)中得到采用,人們開(kāi)始認(rèn)識(shí)到高級(jí)可編程邏輯所帶來(lái)的好處。通過(guò)將低成本高性能的嵌入式處理器內(nèi)核與可定制的FPGA電路配合使用,電子設(shè)備生產(chǎn)商能為其特定的產(chǎn)品量身定制芯片,從而以較低的成本和較快的速度將產(chǎn)品推向市場(chǎng)。但若想合理地采用這項(xiàng)先進(jìn)技術(shù),設(shè)計(jì)者需要功能強(qiáng)大的工具才能滿(mǎn)足設(shè)計(jì)要求。 Floorplanner即是適合這類(lèi)應(yīng)用的一種工具,它允許設(shè)計(jì)者控制嵌入式處理器、相關(guān)IP以及定制邏輯的布局和分組,從而簡(jiǎn)化復(fù)雜的系統(tǒng)級(jí)芯片的開(kāi)發(fā)過(guò)程,并提升系統(tǒng)的整體性能。

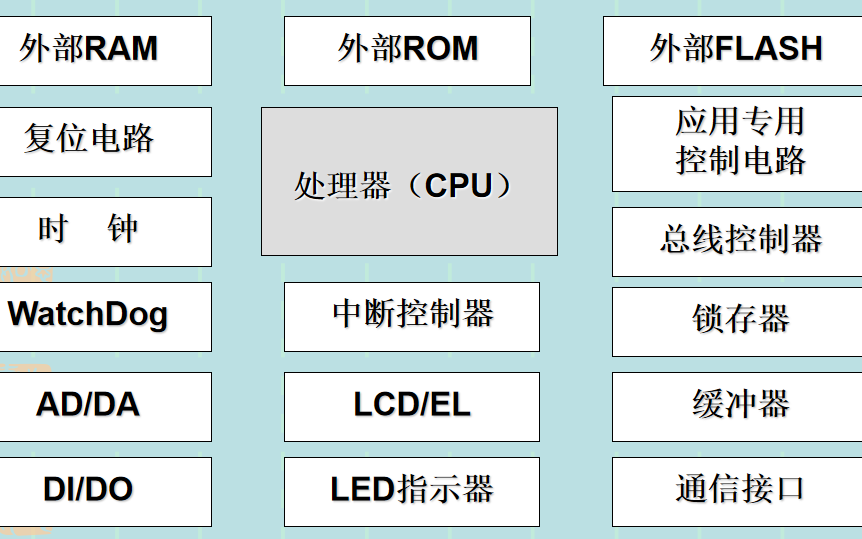

本文將討論如何在一個(gè)集成了PowerPC內(nèi)核、一個(gè)DDR內(nèi)存控制器以及一個(gè)LCD控制器的嵌入式系統(tǒng)的開(kāi)發(fā)過(guò)程中采用Floorplanner。在圖1中,DDR內(nèi)存控制器通過(guò)一個(gè)高速處理器本地總線(xiàn)(PLB)與PPC相連,因而在該系統(tǒng)中可以通過(guò)高速內(nèi)存訪(fǎng)問(wèn)來(lái)實(shí)現(xiàn)指令和數(shù)據(jù)傳輸。LCD控制器對(duì)帶寬要求較低,可以通過(guò)較低速的片上外圍總線(xiàn)(OPB)與PPC連接,OPB通過(guò)一個(gè)PLB到OPB橋?qū)⒌退俚耐鈬鷥?nèi)核與PLB相連。圖中還顯示了兩個(gè)片上存儲(chǔ)控制器和BRAM的用法,這是一個(gè)很重要的特性。從系統(tǒng)模塊圖可以看出,當(dāng)系統(tǒng)中額外增加其它總線(xiàn)控制器時(shí),嵌入式系統(tǒng)設(shè)計(jì)能夠輕松地對(duì)其提供支持。

圖1基于PowerPC 405的嵌入式系統(tǒng)框圖

系統(tǒng)生成

我們可以采用系統(tǒng)生成器來(lái)定義所需處理器以及相關(guān)控制器的參數(shù),從而簡(jiǎn)化嵌入式系統(tǒng)的設(shè)計(jì)和創(chuàng)建,并產(chǎn)生嵌入式系統(tǒng)的源設(shè)計(jì) (通常包含一個(gè)處理器內(nèi)核、幾個(gè)總線(xiàn)結(jié)構(gòu)以及現(xiàn)有的IP)。同時(shí),系統(tǒng)生成器還能產(chǎn)生系統(tǒng)啟動(dòng)所需的軟件頭文件。有了這些工具,軟、硬件設(shè)計(jì)工程師就能同時(shí)并行地進(jìn)行嵌入式系統(tǒng)開(kāi)發(fā)。

對(duì)硬件設(shè)計(jì)工程師而言,系統(tǒng)生成器能夠創(chuàng)建系統(tǒng)中關(guān)鍵部件安裝時(shí)所需的所有文件,并能使外圍器件定義、外圍器件創(chuàng)建、以及處理器上數(shù)百個(gè)管腳與外圍器件和系統(tǒng)總線(xiàn)的連接自動(dòng)進(jìn)行。對(duì)于開(kāi)發(fā)工程師而言,系統(tǒng)生成器在進(jìn)行HW/SW系統(tǒng)權(quán)衡時(shí)能提供很大幫助,而且還能解決軟硬件優(yōu)化的問(wèn)題。如果沒(méi)有系統(tǒng)生成器,則必須手動(dòng)產(chǎn)生系統(tǒng),將使系統(tǒng)設(shè)計(jì)時(shí)間和設(shè)計(jì)復(fù)雜度增加。

如何利用Floorplanner

很多EDA廠(chǎng)商都提供的另一種工具是Floorplanner,硬件設(shè)計(jì)工程師利用該工具可以控制擺放那些與他們所感興趣的功能相關(guān)的邏輯,并且在功能實(shí)現(xiàn)后立即查看器件內(nèi)的布局線(xiàn)路情況。以嵌入式系統(tǒng)為例,F(xiàn)loorplanner可以幫助設(shè)計(jì)工程師查看和(或)控制處理器以及相關(guān)外圍器件的擺放,這些外圍器件的布局可能對(duì)滿(mǎn)足設(shè)計(jì)性能要求非常關(guān)鍵。

如前所述,PowerPC 405內(nèi)核中包含一個(gè)片上存儲(chǔ)(OCM)控制器,該OCM控制器既能提供到64位指令BRAM(ISBRAM)的接口,也能提供到32位數(shù)據(jù)BRAM (DSBRAM)的接口,它最多能尋址16MB的DSBRAM和16MB的ISBRAM。OCM控制器最大的優(yōu)點(diǎn)是能夠保持一個(gè)固定的執(zhí)行時(shí)延。為了滿(mǎn)足 FPGA的時(shí)序的要求,硬件設(shè)計(jì)工程師必須控制OCM BRAM相對(duì)于OCM控制器接口的擺放位置:DSBRAM必須放在PPC405核之上,而ISBRAM必須置于PPC405之下,如圖2所示。要想控制這類(lèi)布局,最簡(jiǎn)單的方法也許就是采用Floorplanner工具。

Floorplanner具有查看和(或)擺放邏輯的功能,該工具應(yīng)用恰當(dāng)時(shí)能夠提升嵌入式系統(tǒng)的性能,但若應(yīng)用不當(dāng)則會(huì)降低系統(tǒng)性能。因此,用戶(hù)要想成功地應(yīng)用該工具,還應(yīng)該注意以下幾點(diǎn)建議:

1. 硬件設(shè)計(jì)工程師在采用Floorplanner對(duì)硬件開(kāi)始布局之前,必須清楚了解設(shè)計(jì)和目標(biāo)結(jié)構(gòu),這對(duì)正確的設(shè)計(jì)布局和硬件資源利用非常關(guān)鍵。

2. 在對(duì)FPGA進(jìn)行物理布局時(shí)必須優(yōu)先考慮I/O。如圖3所示,控制信號(hào)I/O應(yīng)該放在FPGA的頂部或底部,數(shù)據(jù)總線(xiàn)I/O應(yīng)放在左側(cè)或右側(cè),這樣才能保證最有效地利用FPGA的布線(xiàn)資源,并最大程度地優(yōu)化性能。

3. 算術(shù)功能在FPGA中通常利用專(zhuān)用的進(jìn)位鏈(carry-chain)來(lái)實(shí)現(xiàn),進(jìn)位鏈在一個(gè)特殊的垂直方向上運(yùn)行。例如,一個(gè)10位計(jì)數(shù)器的進(jìn)位鏈就在從器件底端到頂端的垂直方向上運(yùn)行。因而,設(shè)計(jì)者可以將其總線(xiàn)的LSB置于器件的底部而將MSB置于頂部,充分利用進(jìn)位鏈的方向性。

4. Floorplanner根據(jù)邏輯層次的不同來(lái)顯示邏輯單元,因而很容易將邏輯單元?jiǎng)澐譃楣驳慕M或區(qū)域。這種根據(jù)層次分組的方式利用了本地布線(xiàn)資源,因而能夠降低信號(hào)延遲,提高電路性能。

5. 如圖4所示,交替地放置相關(guān)的總線(xiàn)。硬件設(shè)計(jì)工程師可以通過(guò)交替放置相關(guān)的I/O總線(xiàn)來(lái)降低信號(hào)延遲,但只有在這樣的處理不增加額外的邏輯單元時(shí)才有意義。需要提醒的是,在進(jìn)行布線(xiàn)決策時(shí)一定要把整個(gè)設(shè)計(jì)看作一個(gè)整體。

硬件設(shè)計(jì)工程師在嵌入式系統(tǒng)設(shè)計(jì)中適當(dāng)注意以上幾點(diǎn),就能輕松地對(duì)一個(gè)設(shè)計(jì)進(jìn)行組織和規(guī)劃。在對(duì)嵌入式系統(tǒng)進(jìn)行底層規(guī)劃之前,設(shè)計(jì)工程師必須首先給不同的組分配邏輯資源。組通常都是基于設(shè)計(jì)層次的,設(shè)計(jì)層次為嵌入式系統(tǒng)提供了一個(gè)自然的邊界,F(xiàn)loorplanner可以利用這個(gè)邊界輕松地進(jìn)行組創(chuàng)建。系統(tǒng)生成器在創(chuàng)建系統(tǒng)的每一個(gè)模塊時(shí)均相應(yīng)創(chuàng)建了獨(dú)特的分層參考,這就使得嵌入式系統(tǒng)的組定義變得非常簡(jiǎn)單。在需要進(jìn)行底層規(guī)劃的組創(chuàng)建好之后,就可以分配放置這些組的物理區(qū)域。每個(gè)組的放置需要基于前面的幾點(diǎn)建議和設(shè)計(jì)版圖來(lái)進(jìn)行。

設(shè)計(jì)版圖約束

Floorplanner提供了三種方法來(lái)約束邏輯模塊和邏輯組的物理位置分配:

1. 第一種方法就是將邏輯部件置于一個(gè)特定的物理位置,或放在某個(gè)特定的元件內(nèi)部。例如,數(shù)據(jù)總線(xiàn)的一個(gè)輸出(以第10位為例)可以分配給器件的第37腳。但這類(lèi)分配沒(méi)有靈活性,布局工具和布線(xiàn)工具必須將第10位的輸出驅(qū)動(dòng)置于器件管腳37中。這種方法還可以用于布局和分配一組邏輯部件。

2. 第二種方法是將某個(gè)邏輯單元或邏輯組分配給一個(gè)物理區(qū)域。通常采用的都是這種方法,因?yàn)樗试S布局工具和布線(xiàn)工具移動(dòng)某區(qū)域組內(nèi)的邏輯單元,以實(shí)現(xiàn)最優(yōu)的布局和布線(xiàn)。為了優(yōu)化系統(tǒng)設(shè)計(jì),功能更強(qiáng)大的Floorplanner工具還支持組間重疊,以及在一個(gè)經(jīng)過(guò)底層規(guī)劃的區(qū)域?qū)崿F(xiàn)不經(jīng)底層規(guī)劃處理的邏輯。

3. 第三種方法是創(chuàng)建關(guān)聯(lián)布局宏(Relationally Plalced Macro, RPM)。RPM定義了各邏輯單元之間的相對(duì)版圖設(shè)計(jì),但準(zhǔn)確的布局是由布局和布線(xiàn)工具決定的,這樣可以得到最佳的設(shè)計(jì)性能。例如,一個(gè)查找表(LUT) 可以與一個(gè)觸發(fā)器置于同一塊(slice)內(nèi),而一個(gè)塊又可以直接置于另一塊之上。RPM使設(shè)計(jì)工程師能夠控制某些特定模塊的布線(xiàn),但并沒(méi)有嚴(yán)格地限制布局和布線(xiàn)工具。

通過(guò)在嵌入式系統(tǒng)設(shè)計(jì)中應(yīng)用以上提出的建議和方法,硬件設(shè)計(jì)工程師就能控制某些特定部件的布局,改善器件的整體布線(xiàn)(通過(guò)利用區(qū)域性分組),并控制某些特定部件之間的相對(duì)布局(通過(guò)采用RPM)。

應(yīng)用舉例

圖5采用了PPC 405來(lái)說(shuō)明上面所述方法和建議,該應(yīng)用是包含了2個(gè)UART和一個(gè)BRAM控制器的嵌入式設(shè)計(jì)。

在該設(shè)計(jì)中,系統(tǒng)生成器創(chuàng)建層次邊界,而邏輯組則在這些邊界的基礎(chǔ)上創(chuàng)建。為PLB仲裁器、UART和BRAM內(nèi)存控制器均可創(chuàng)建區(qū)域組(area group)。將BRAM和PPC 405限制在特定位置,以使設(shè)計(jì)達(dá)到最佳性能。應(yīng)該注意的是,在分配一個(gè)區(qū)域組時(shí),必須為該區(qū)域中的邏輯單元分配足夠的資源。而當(dāng) Floorplanner的功能更強(qiáng)大時(shí),還能為用戶(hù)提供每個(gè)區(qū)域組所需的資源。本例中的區(qū)域組中所包含的資源為實(shí)現(xiàn)所需資源量的兩倍。這樣,通過(guò)向經(jīng)底層規(guī)劃處理后的區(qū)域中添加布局額外的邏輯單元(不包含在組中邏輯單元)可以對(duì)設(shè)計(jì)進(jìn)一步優(yōu)化。

在分配資源時(shí),BRAM內(nèi)存控制器被置于硅片的中央,這樣可以對(duì)所有BRAM元件以及PPC 405內(nèi)核進(jìn)行同等的訪(fǎng)問(wèn)。在本設(shè)計(jì)之中BRAM中包含了PPC 405內(nèi)核所需的數(shù)據(jù)和指令。UART1和UART2的位置在IO附近,以盡可能減少輸入到時(shí)鐘和時(shí)鐘到輸出的時(shí)間。設(shè)計(jì)中有兩個(gè)PLB接口,一個(gè)是 CPU指令端PLB接口,另一個(gè)是CPU數(shù)據(jù)端PLB接口。因此,PLB仲裁器被放在PPC 405內(nèi)核旁邊。

分配給每一個(gè)區(qū)域組的邏輯單元均根據(jù)區(qū)域約束進(jìn)行布局,而且為提高設(shè)計(jì)性能,還在設(shè)計(jì)中混入了額外的邏輯單元,這也正說(shuō)明了為什么在每個(gè)區(qū)域組分配時(shí)都要保留一定的額外空間的原因。

-

處理器

+關(guān)注

關(guān)注

68文章

19178瀏覽量

229201 -

嵌入式

+關(guān)注

關(guān)注

5072文章

19026瀏覽量

303523 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

514瀏覽量

44074

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

嵌入式linux培訓(xùn)之嵌入式微處理器的選擇

如何提高FPGA嵌入式處理器的系統(tǒng)除錯(cuò)率?

嵌入式微處理器如何選擇

如何利用Floorplanner工具?

嵌入式系統(tǒng)教程之嵌入式處理器的詳細(xì)資料說(shuō)明

利用Floorplanner工具提高嵌入式處理器系統(tǒng)的性能

利用Floorplanner工具提高嵌入式處理器系統(tǒng)的性能

評(píng)論